Похожие презентации:

Программируемые логические устройства. Классические ПЛМ

1. Программируемые логические устройства

Классические ПЛМ2. Способы достижения универсальности компонентов

• Программный. СБИС обрабатываютцифровые данные по заданной

программе (микропроцессоры).

• Аппаратный. Состав и назначение

СБИС определяется конечным

приложением (программируемая

логика).

3. Двухуровневая логика

Every logic function can beexpressed in sum-of-products

format (AND-OR)

minterm

Inverting format (NORNOR) more effective

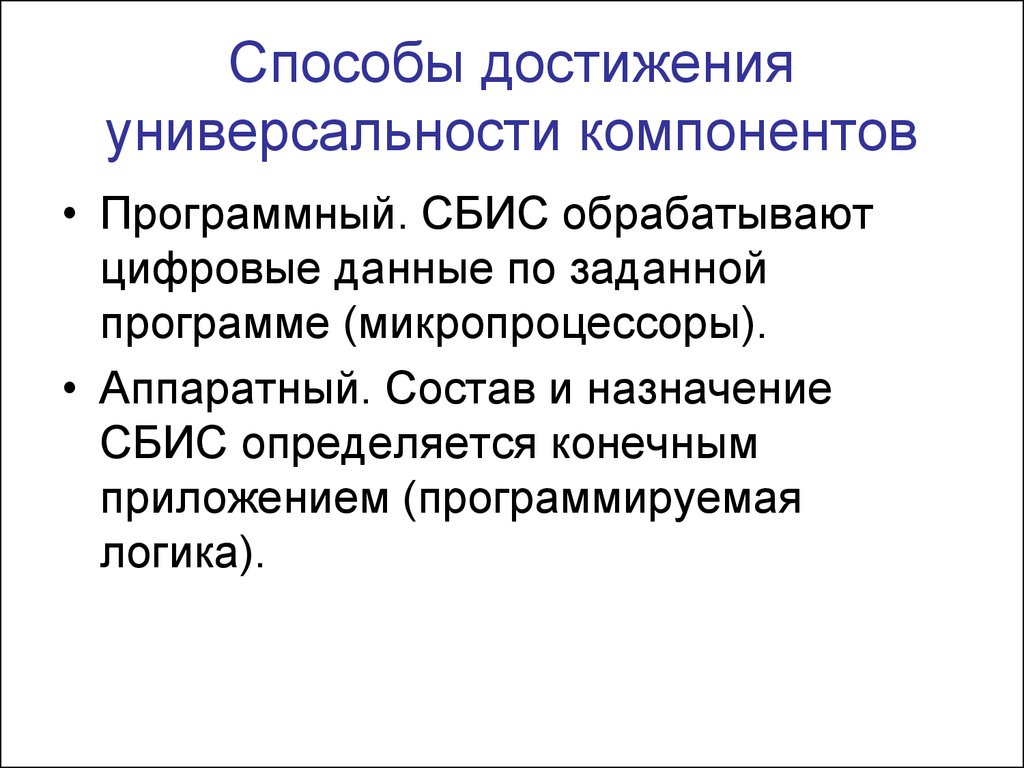

4. Программируемые логические матрицы (ПЛМ)

• Основой ПЛМ служит последовательностьпрограммируемых матриц элементов И и

ИЛИ. В их структуру входят также блоки

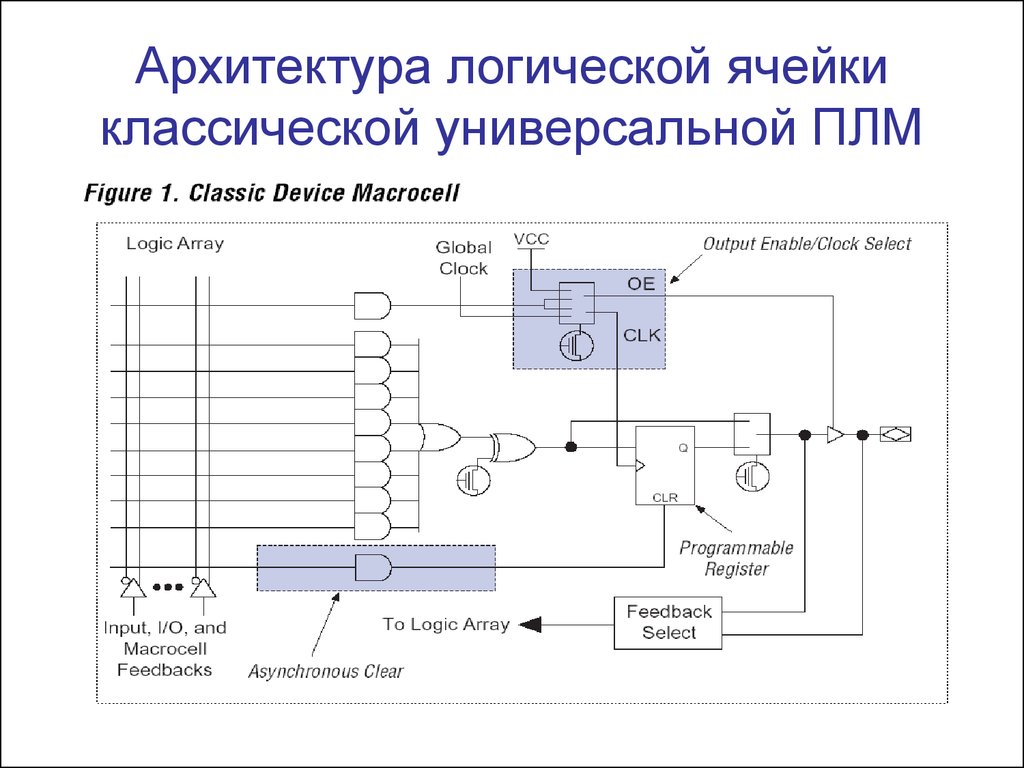

входных и выходных буферных каскадов (БВх

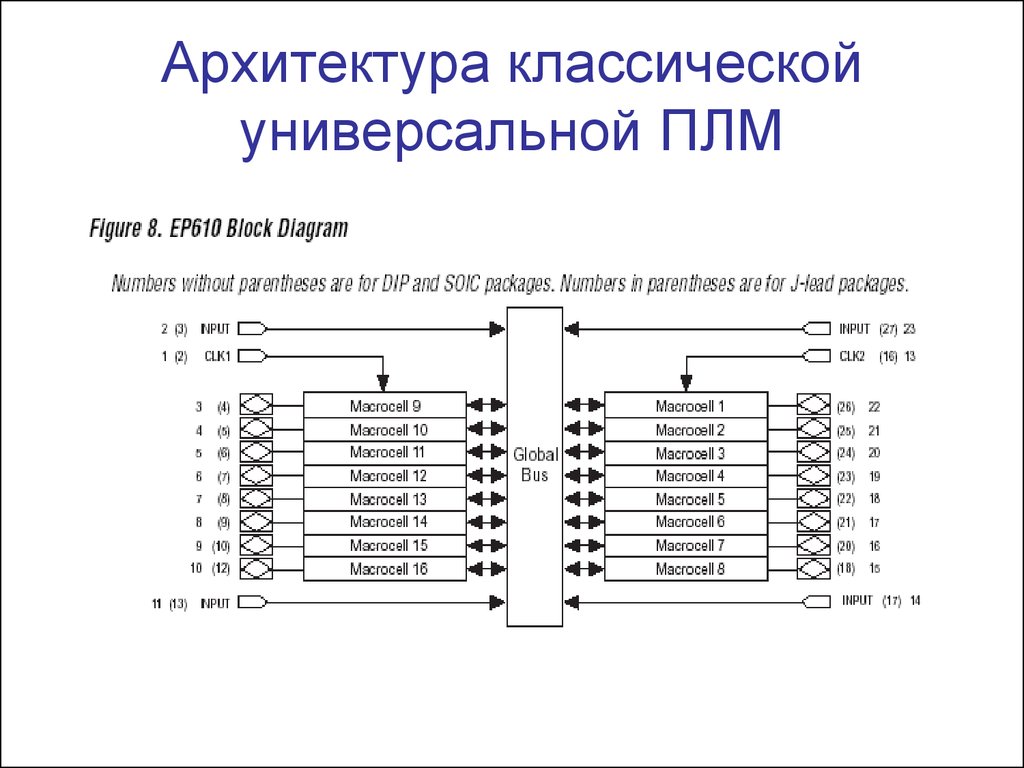

и БВых).

5. Архитектура ПЛМ

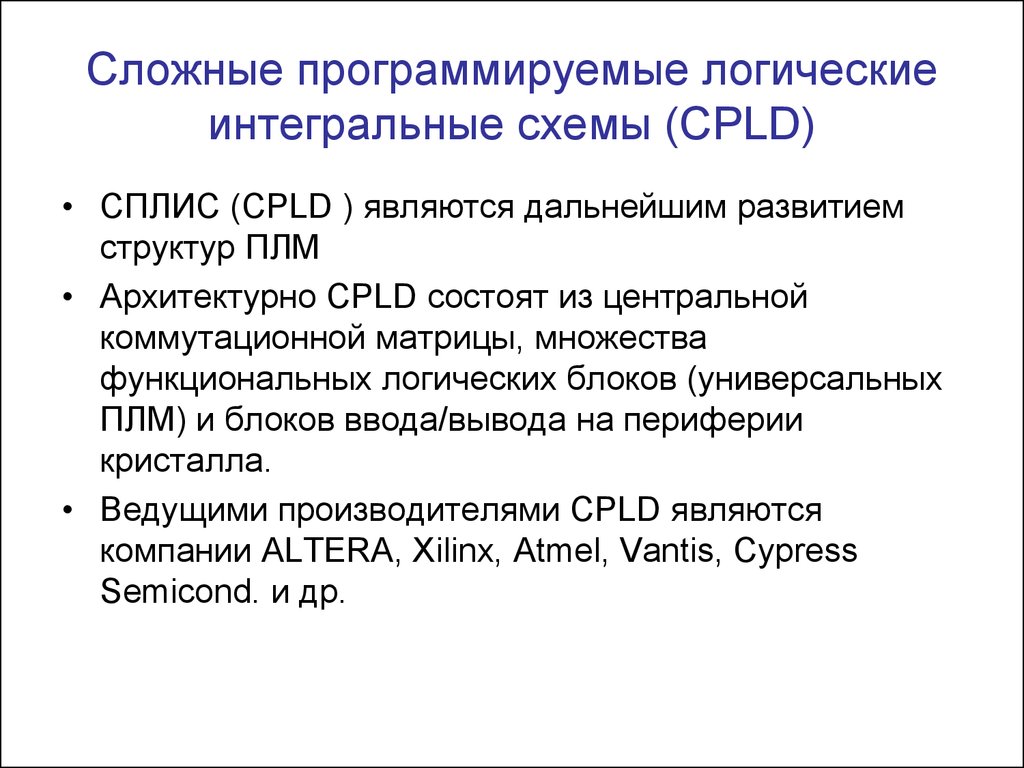

Product termsx0 x1

x2

AND

plane

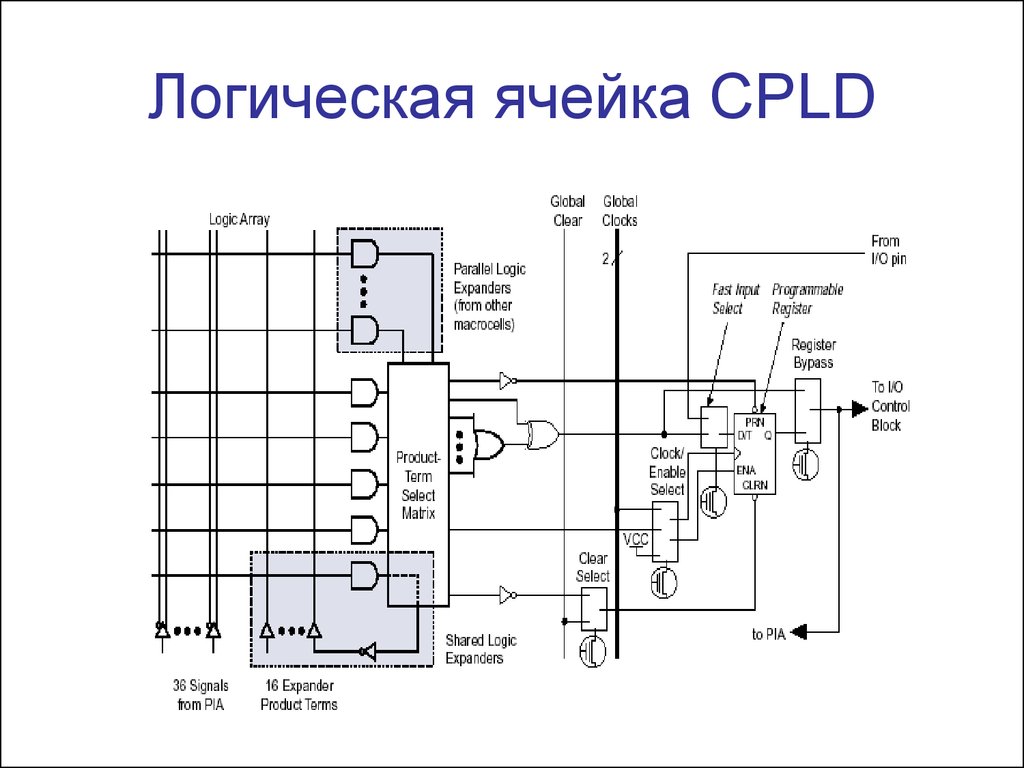

OR

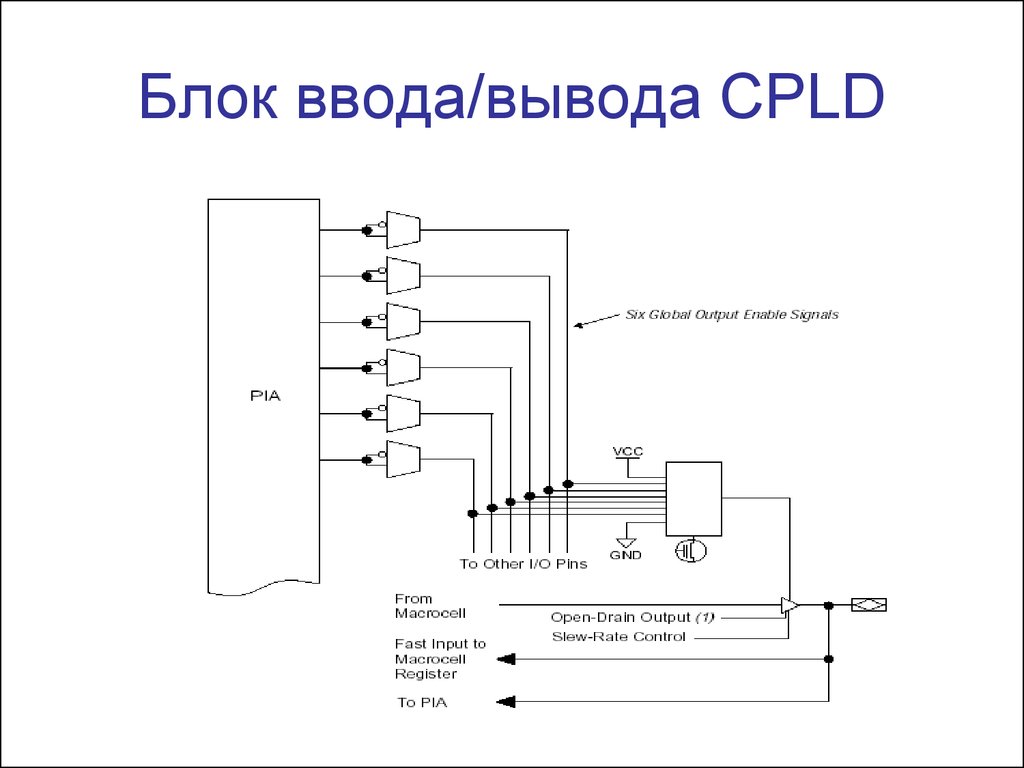

plane

f0

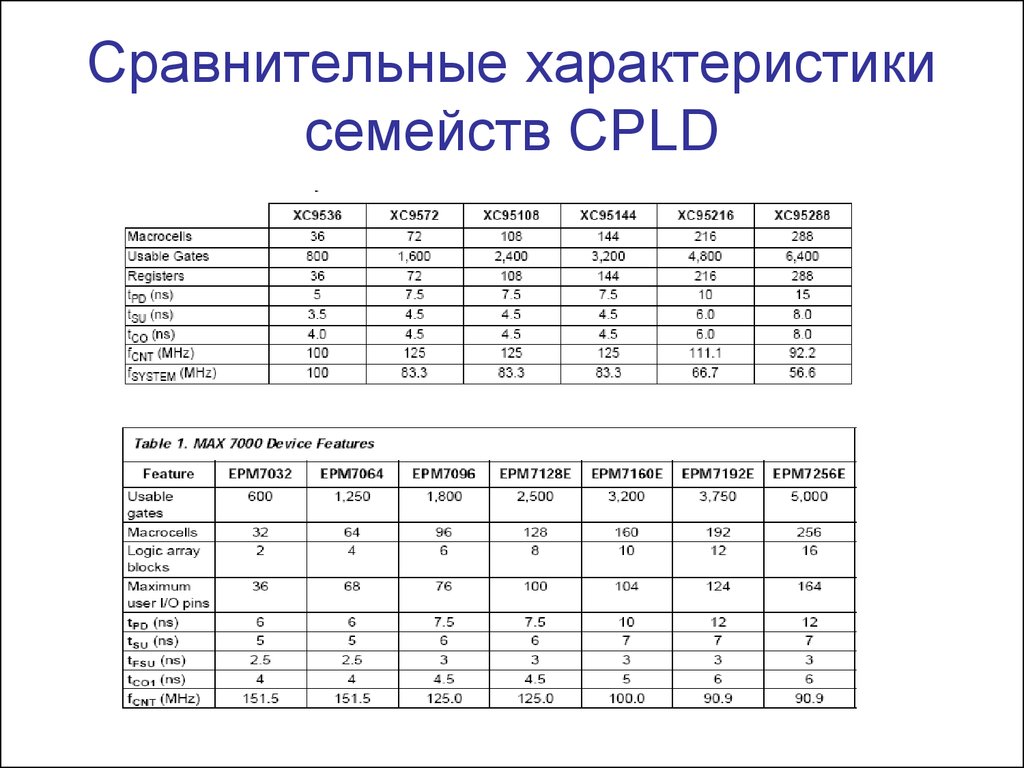

x0

x1

x2

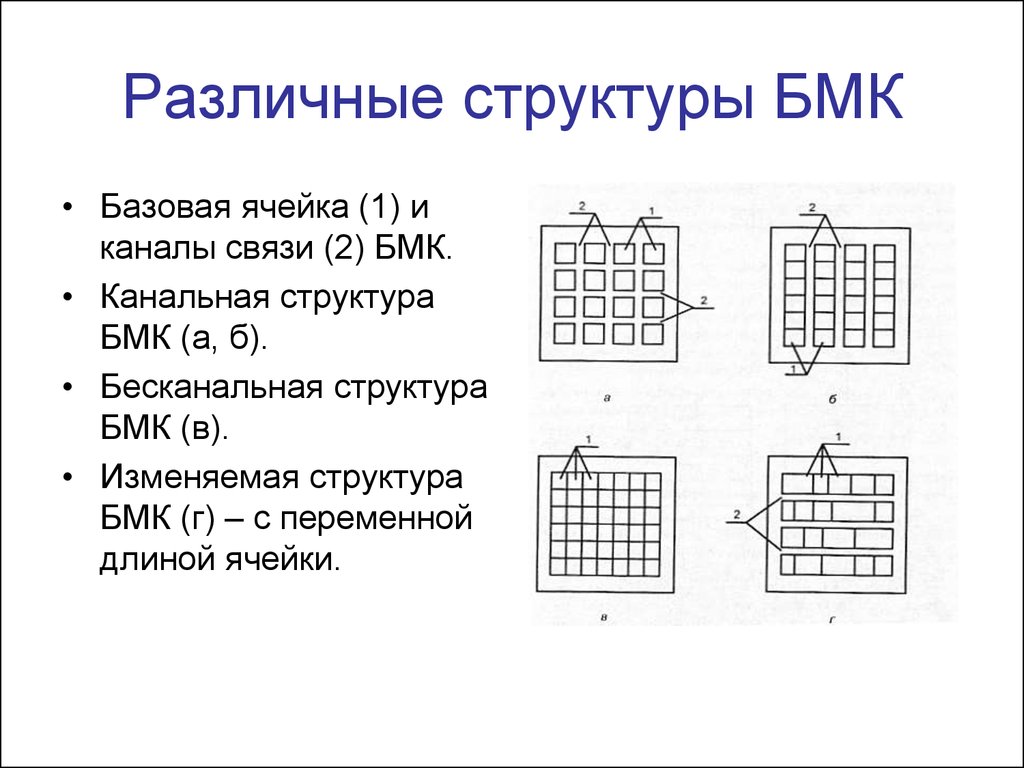

f1

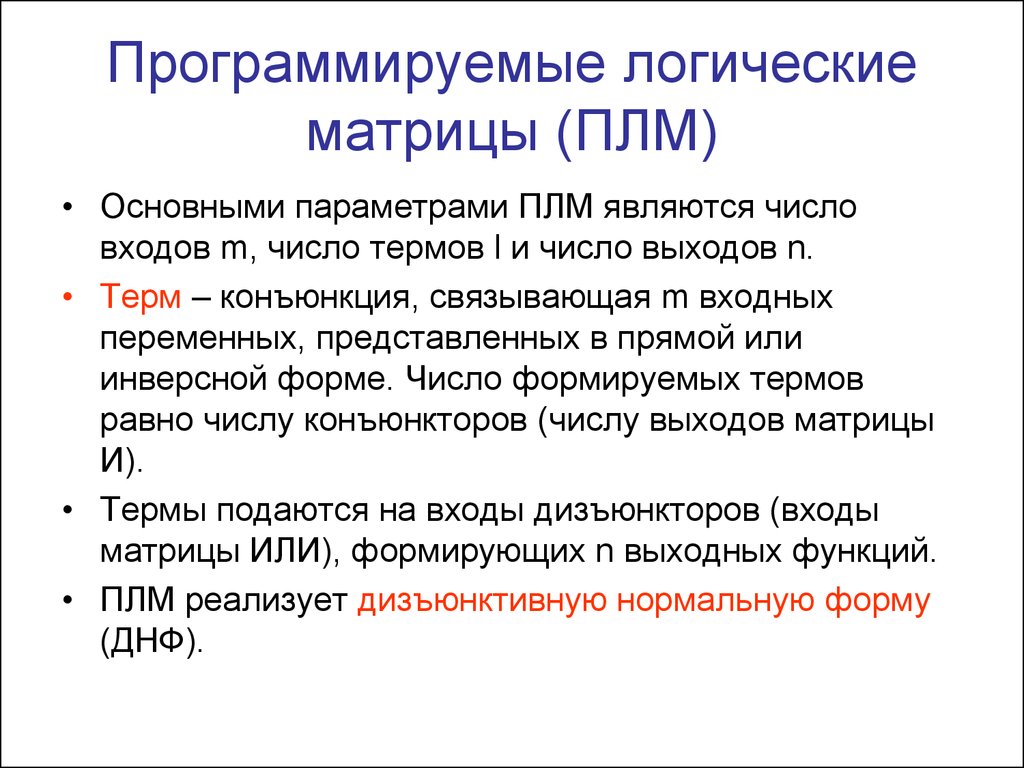

6. Программируемые логические матрицы (ПЛМ)

• Основными параметрами ПЛМ являются числовходов m, число термов l и число выходов n.

• Терм – конъюнкция, связывающая m входных

переменных, представленных в прямой или

инверсной форме. Число формируемых термов

равно числу конъюнкторов (числу выходов матрицы

И).

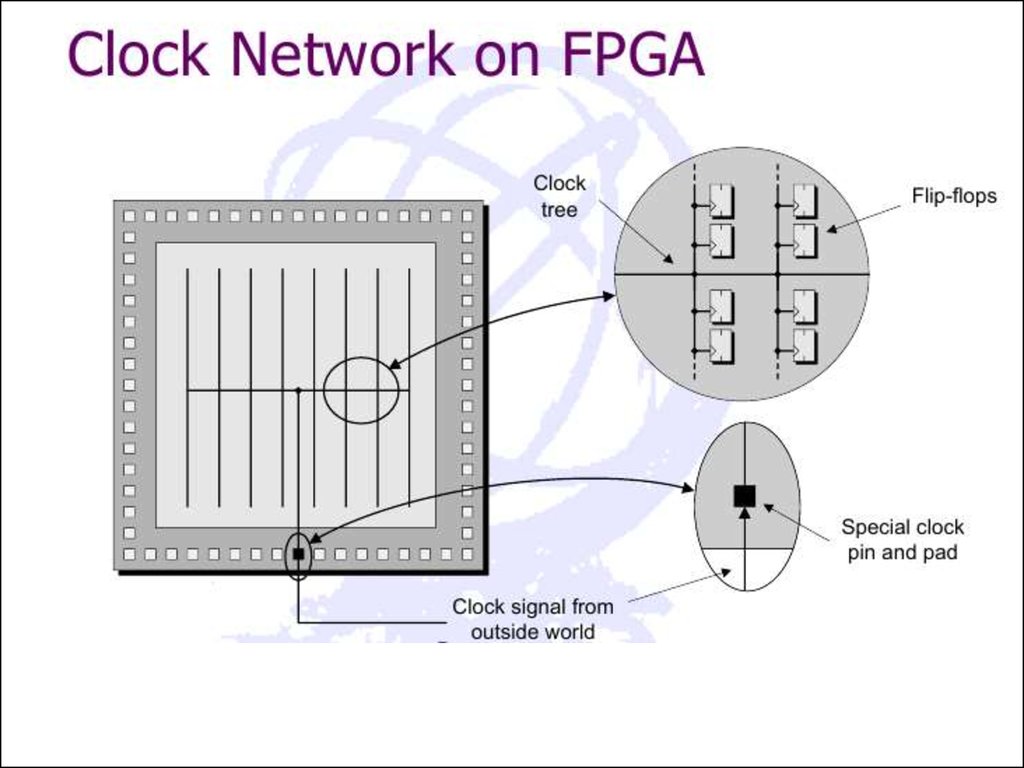

• Термы подаются на входы дизъюнкторов (входы

матрицы ИЛИ), формирующих n выходных функций.

• ПЛМ реализует дизъюнктивную нормальную форму

(ДНФ).

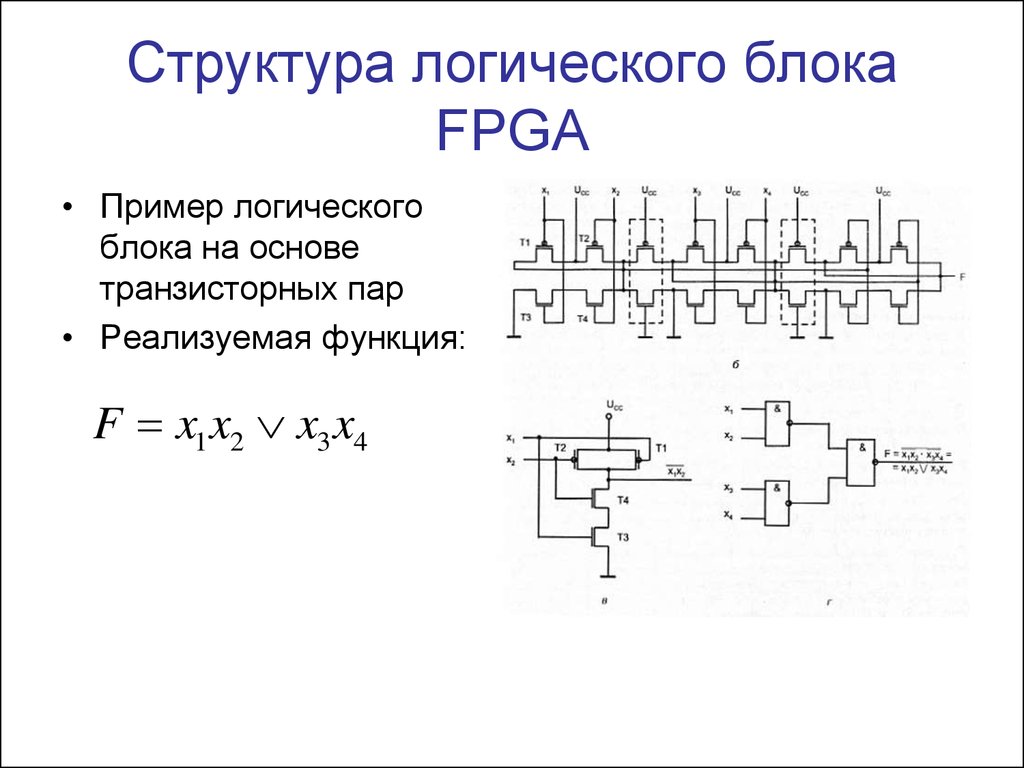

7. Схемотехника ПЛМ

• Упрощенный видбиполярной ПЛМ

• Цепь выработки термов

– диодная схема И

• Матрица ИЛИ

формируется

транзисторами,

включенными по схеме

эмитерных

повторителей

8. Реализация ПЛМ на транзисторах

V DDРеализация ПЛМ на

транзисторах

Or-Plane

And-Plane

f

x0 x0 x1 x1 x2 x2

Pull-up devices

f0 f1

Pull-up devices

GND

9. Способы реализации

I5I4

I3

I2

I1

I0

Programmable

OR array

Programmable AND array

I3

I2

I1

I0

Fixed AND array

I5

I4

I3

I2

I1

I0

Fixed OR array

Programmable AND array

O 3 O2 O1 O0

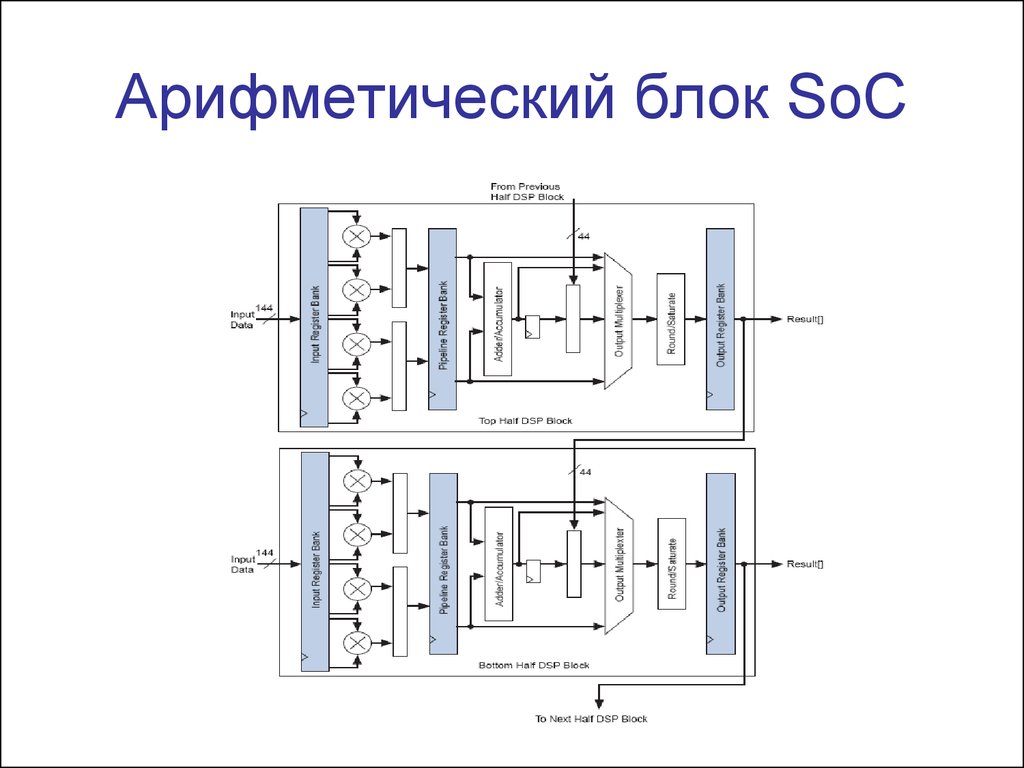

O 3O 2O 1O 0

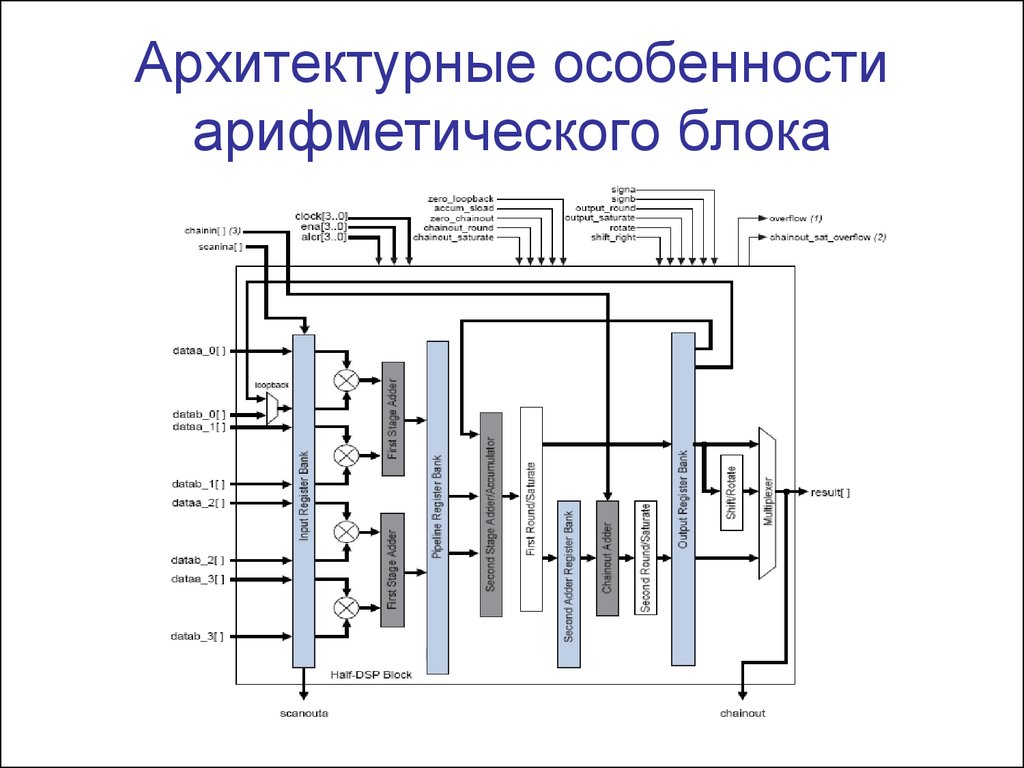

ПЛМ

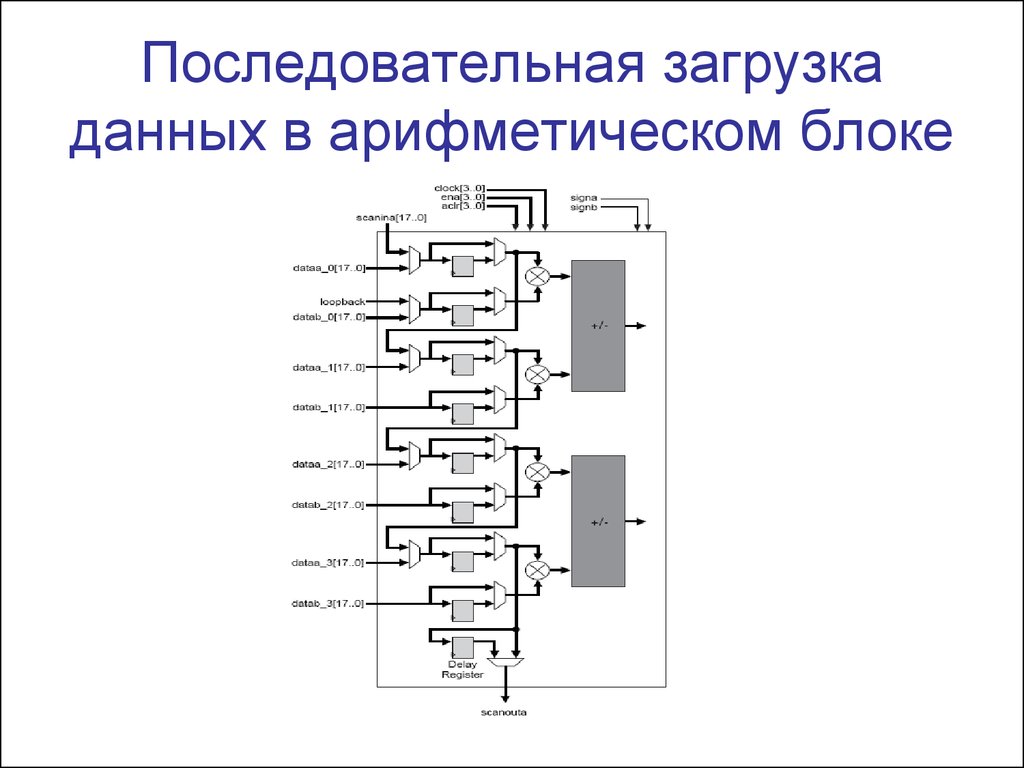

Programmable

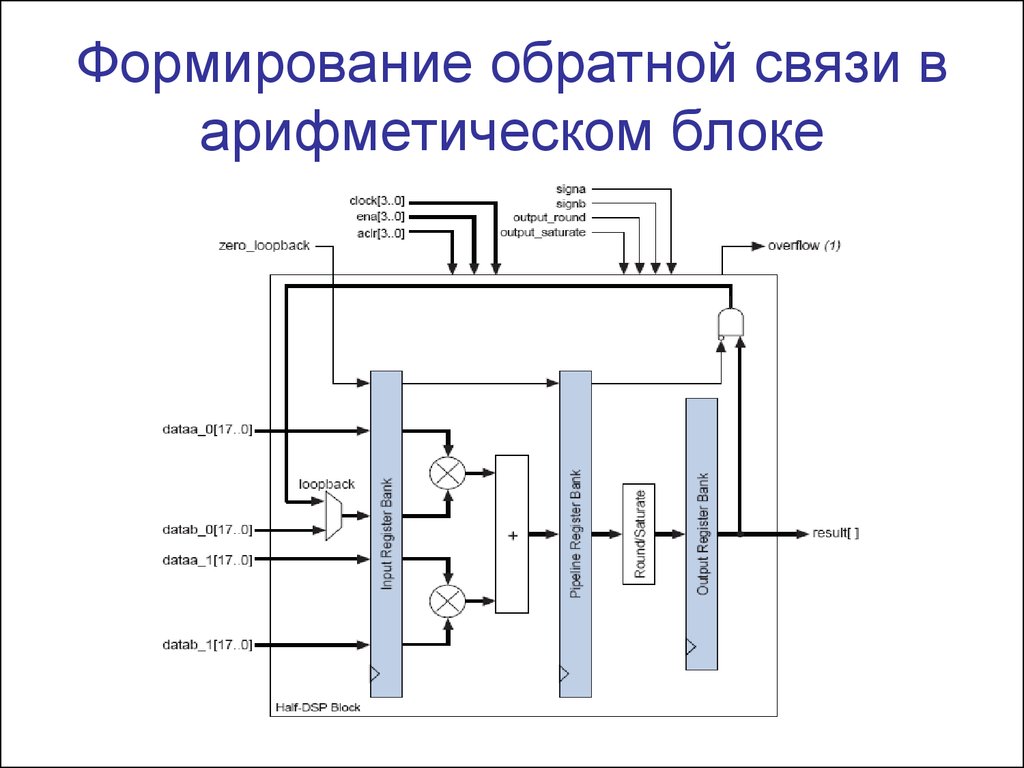

OR array

ПЗУ

Indicates programmable connection

Indicates fixed connection

O 3O 2O 1O 0

ПМЛ

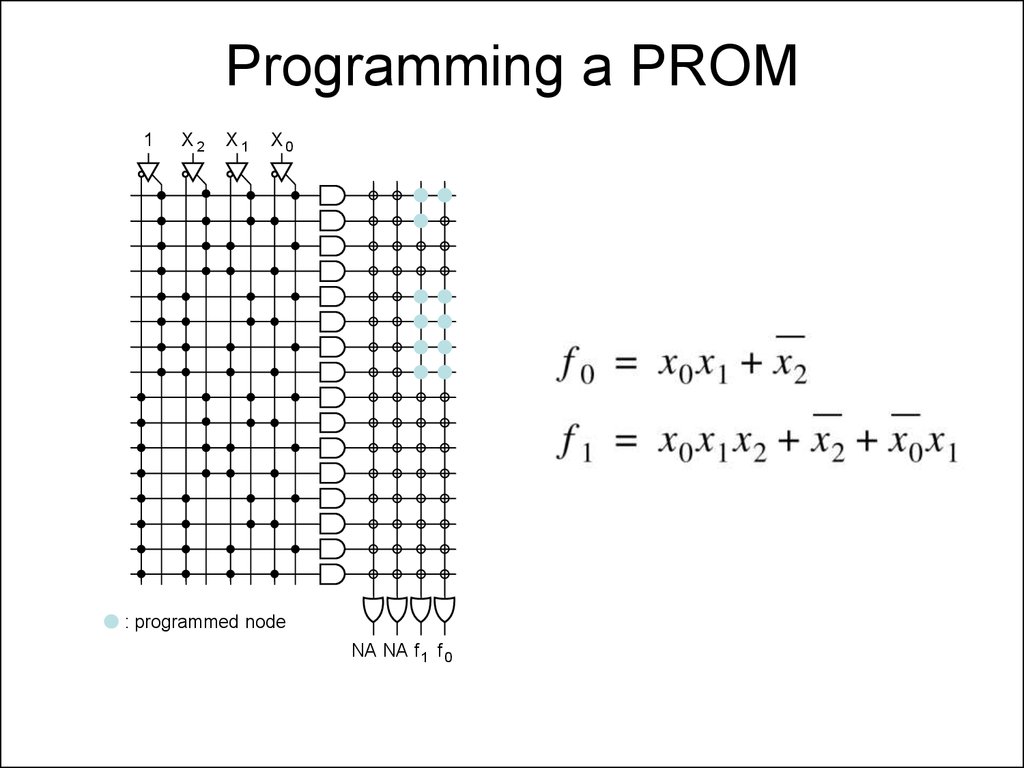

10. Programming a PROM

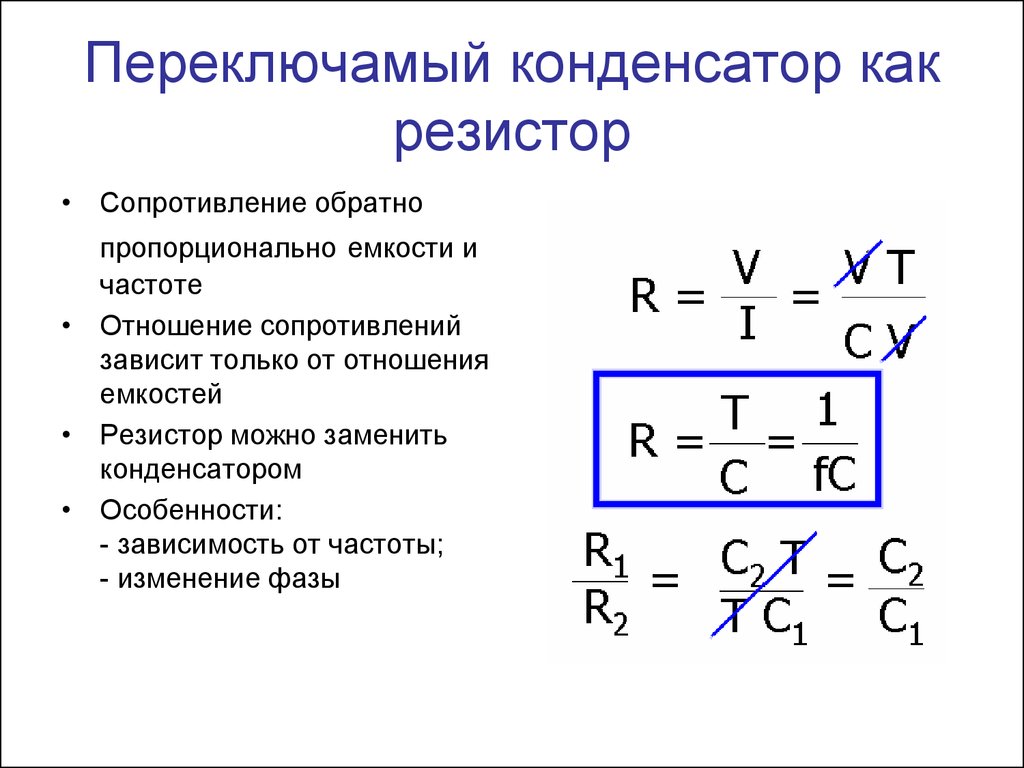

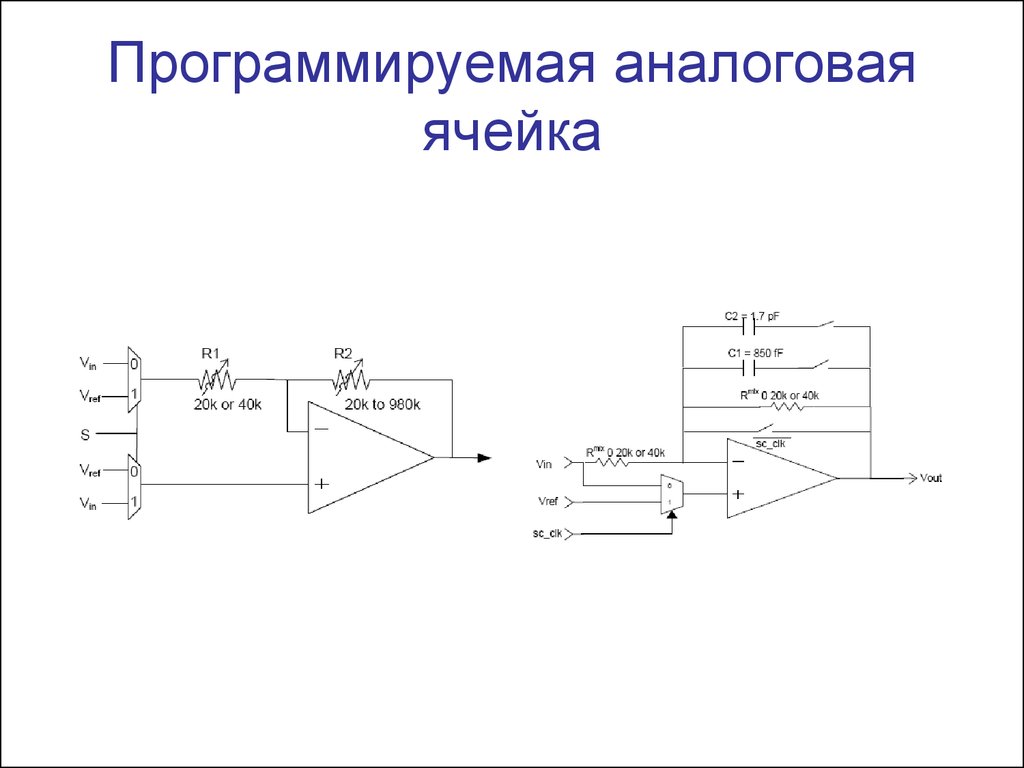

1X2

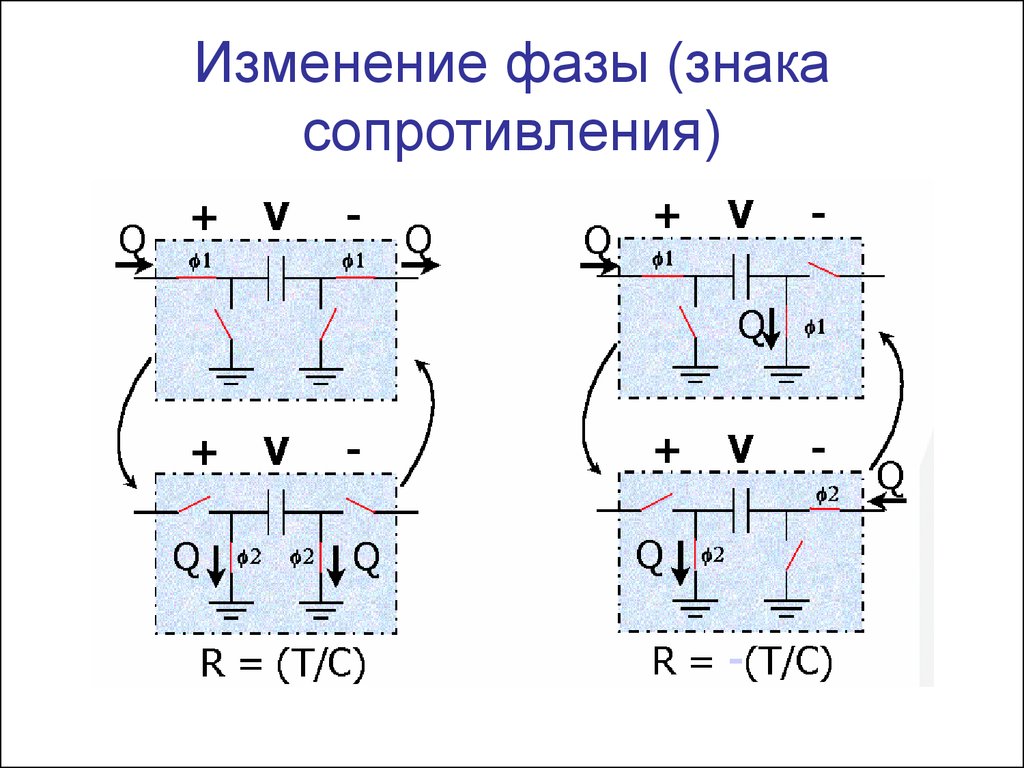

X1

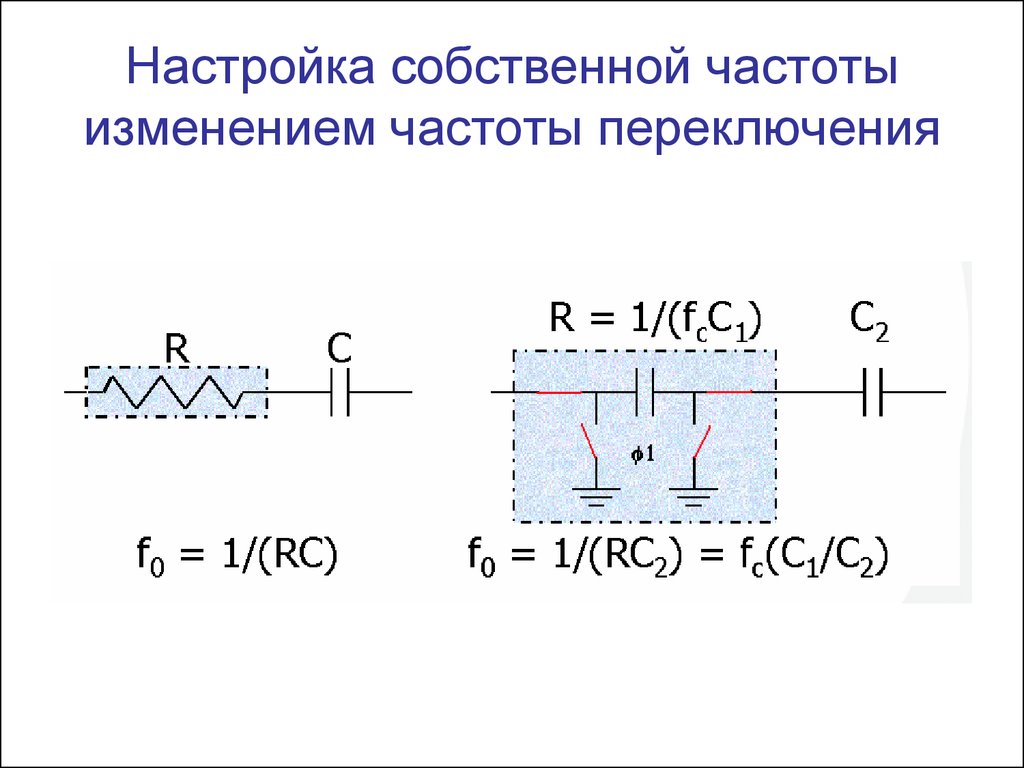

X0

: programmed node

NA NA f 1 f 0

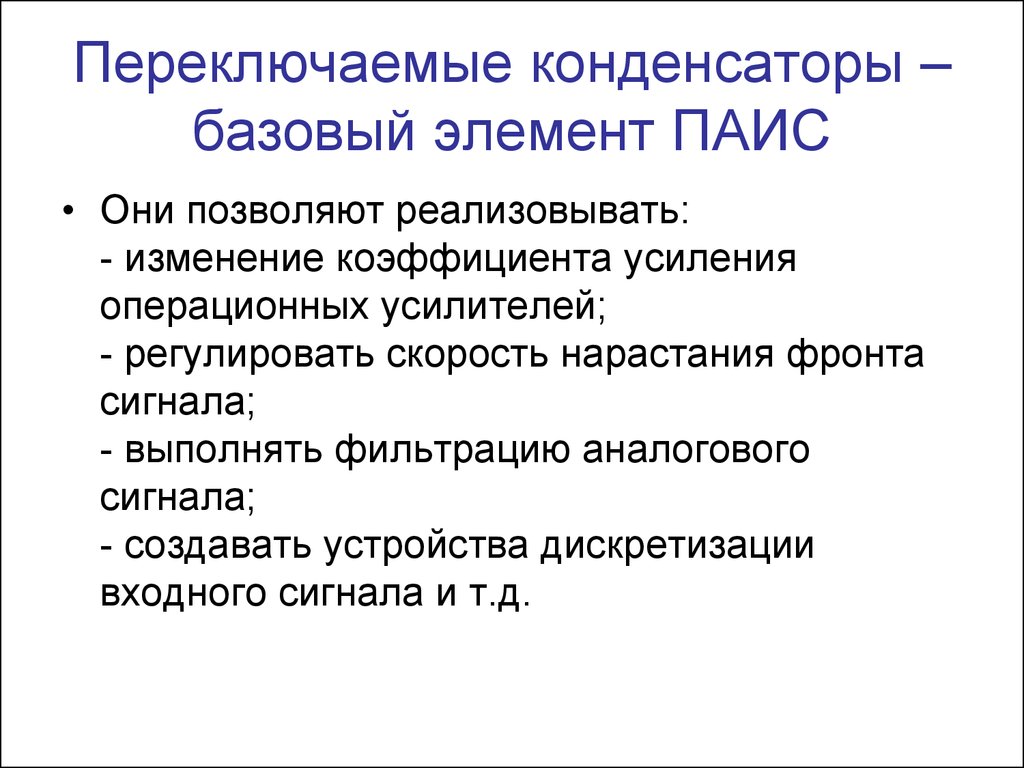

11. Схемотехника ПЛМ

• Воспроизведениескобочных форм

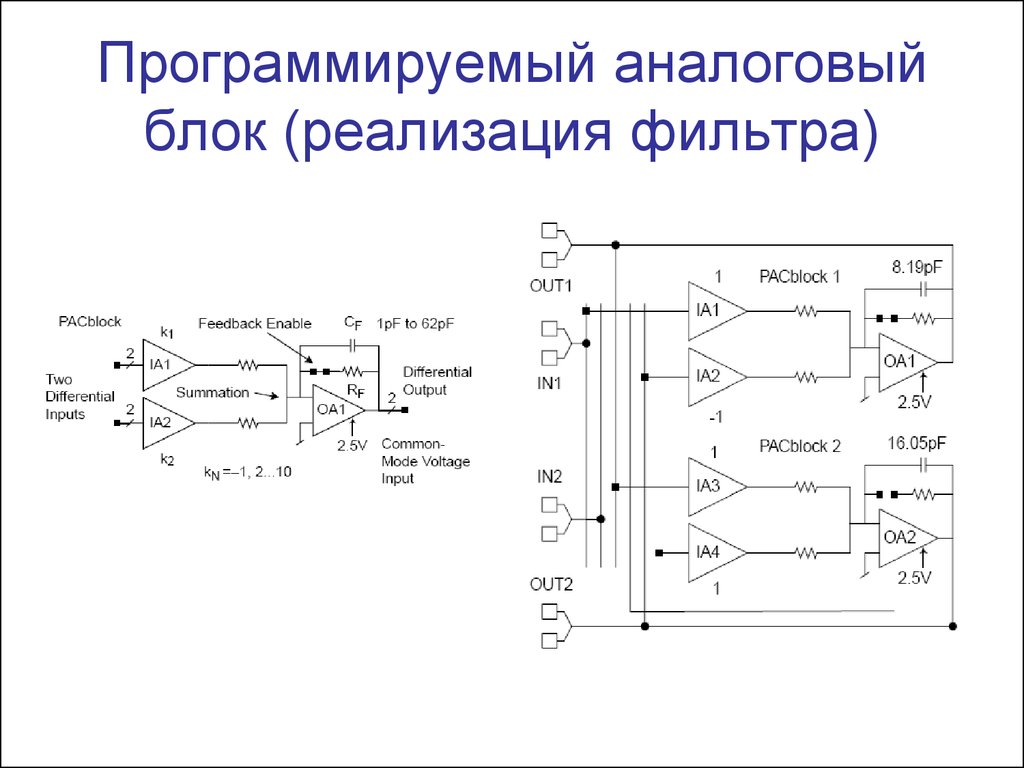

переключательных

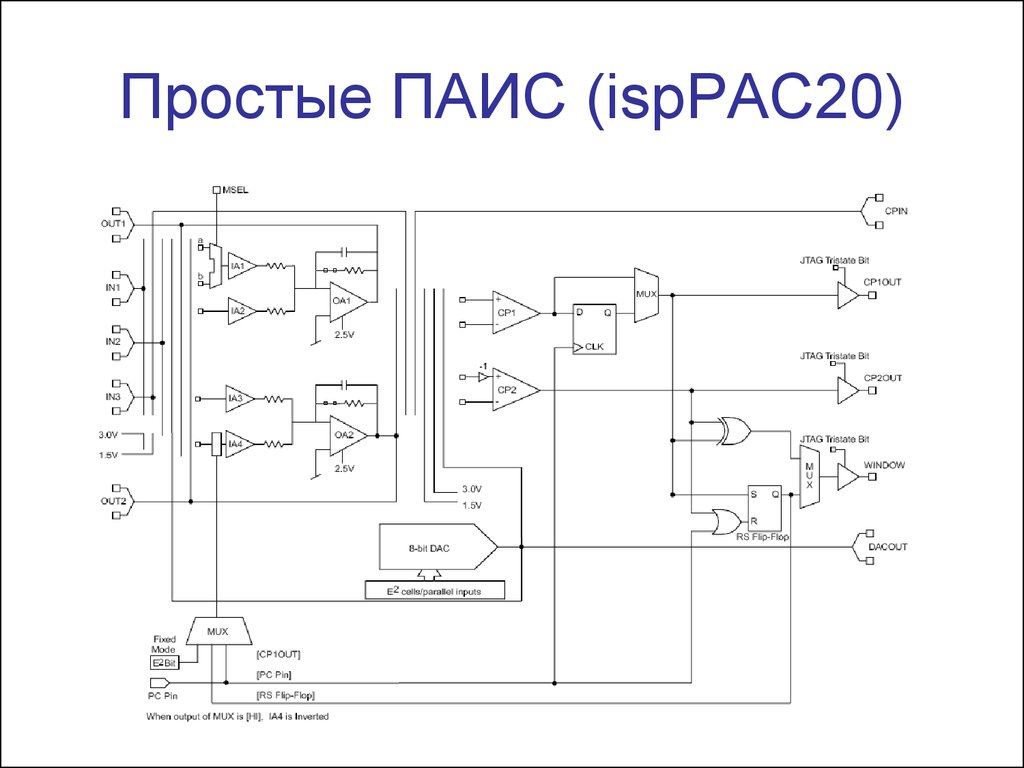

функций – для этого

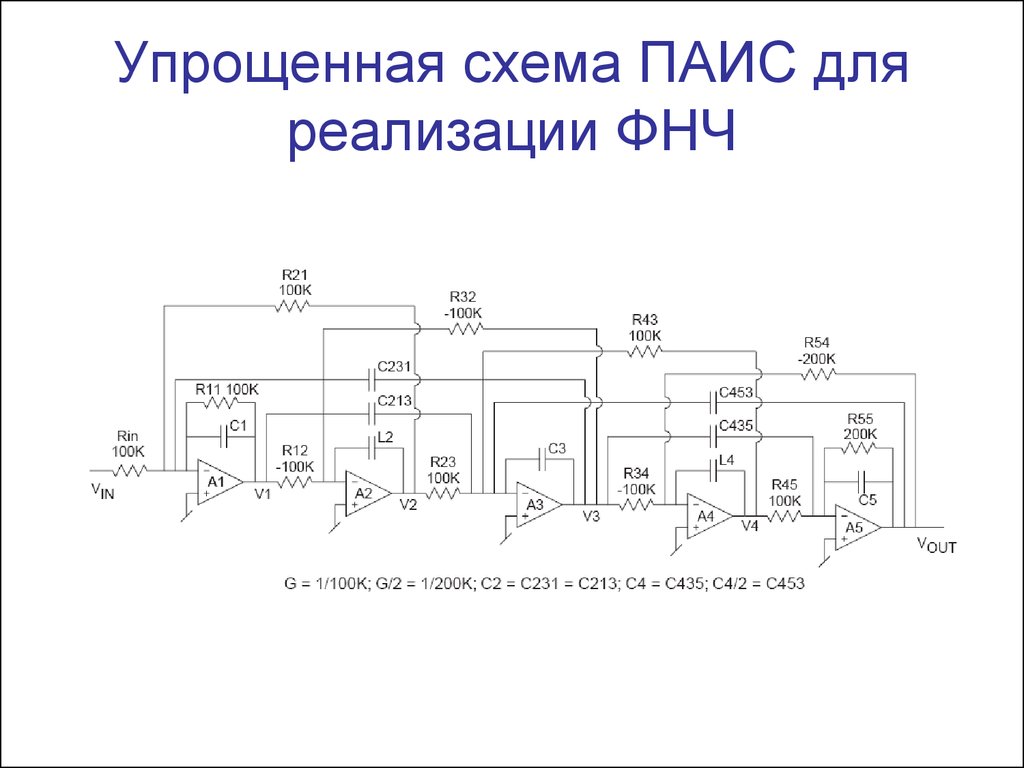

в ПЛМ должны

присутствовать

обратные связи

12. Схемотехника ПЛМ

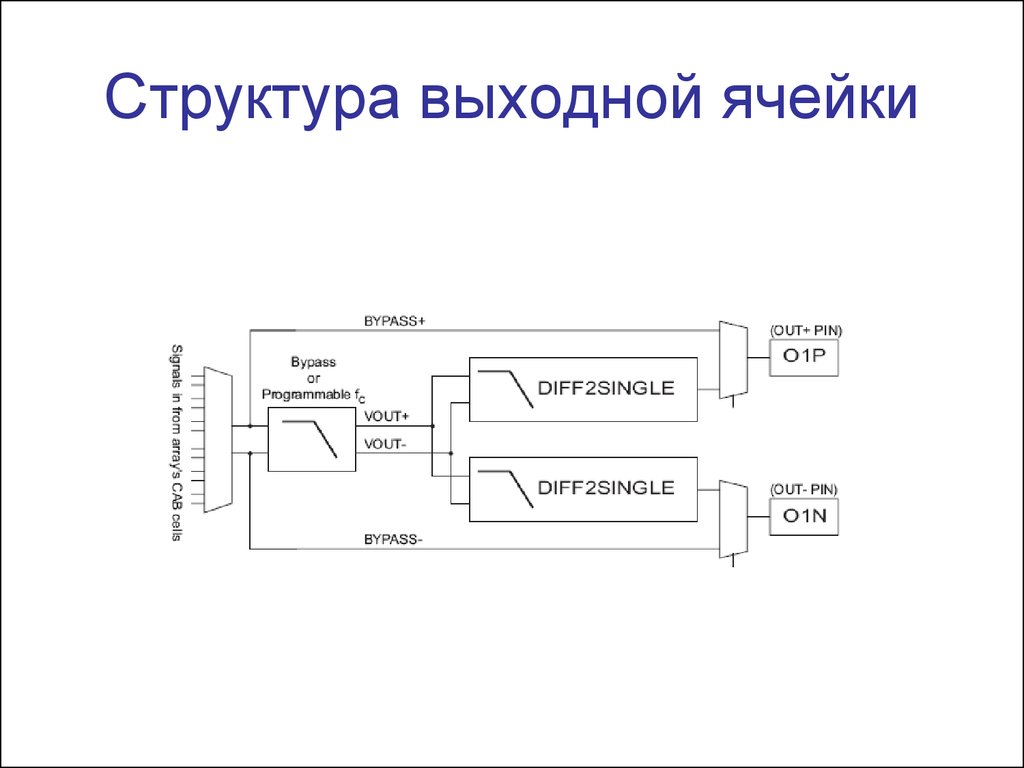

• Для формированияпрямого или

инверсного

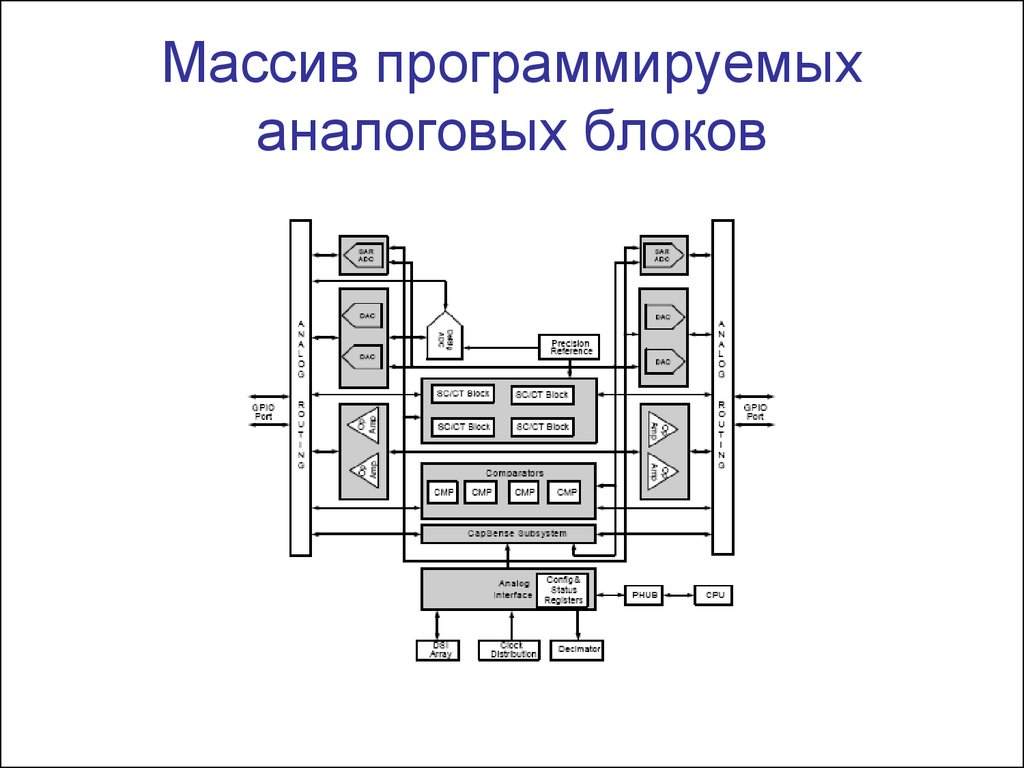

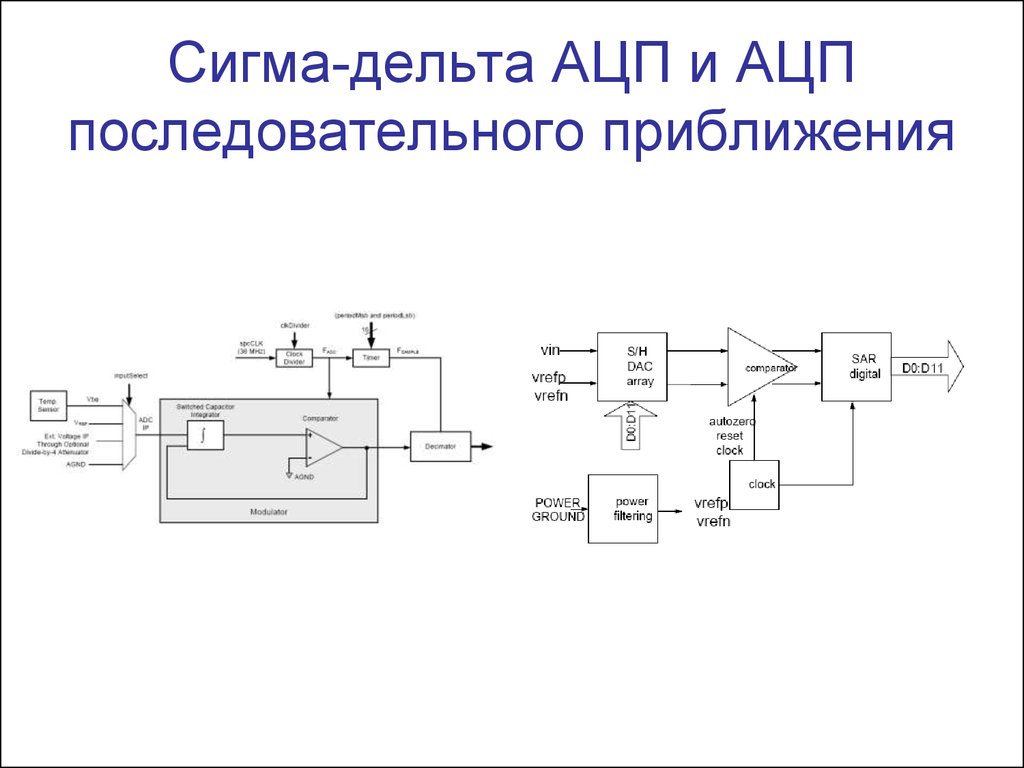

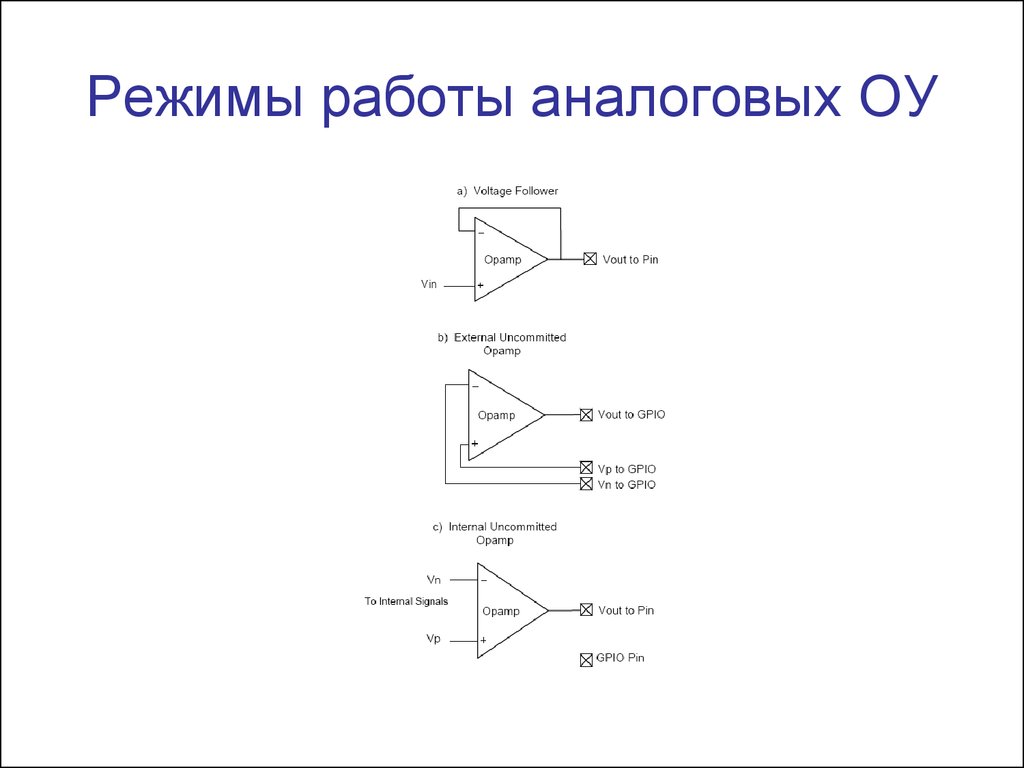

выходного сигнала

используются

сумматоры по

модулю 2

13. Схемотехника ПЛМ

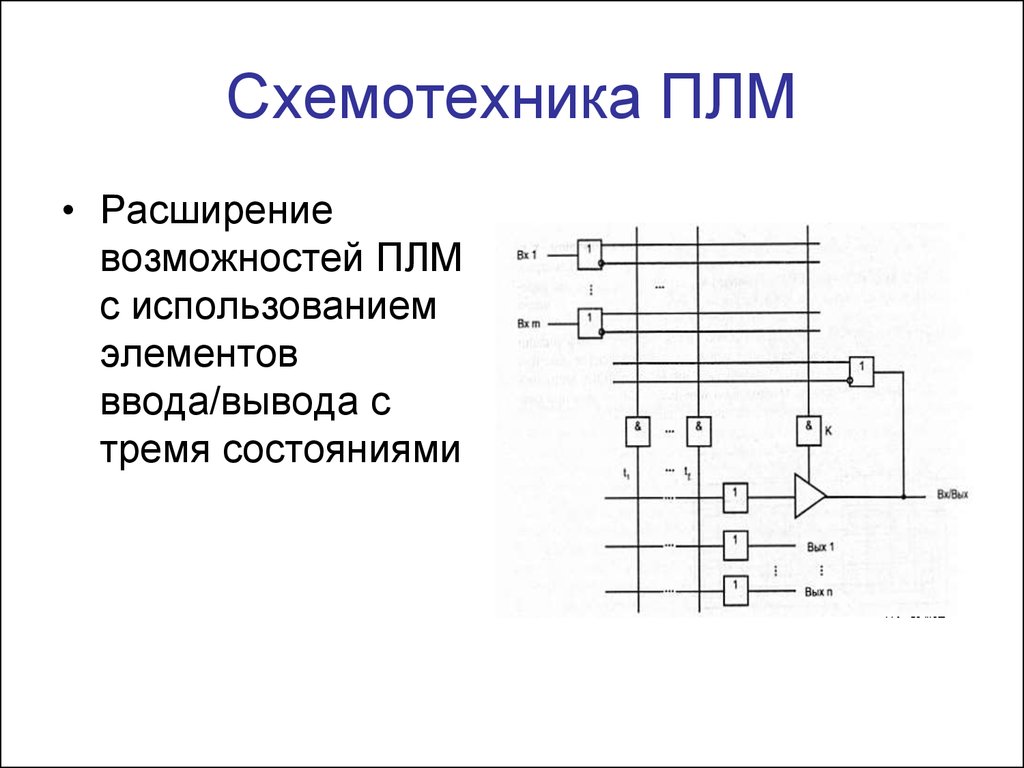

• Расширениевозможностей ПЛМ

с использованием

элементов

ввода/вывода с

тремя состояниями

14. Схемотехника ПЛМ

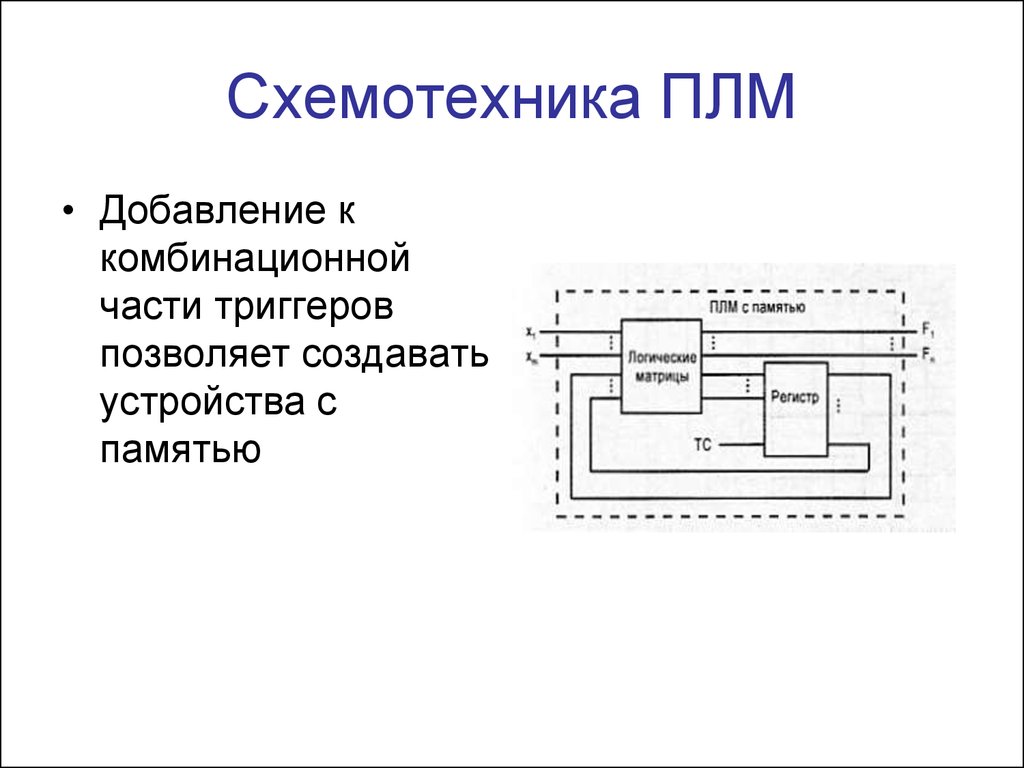

• Добавление ккомбинационной

части триггеров

позволяет создавать

устройства с

памятью

15. Обобщенная структура классической ПЛМ

16. Дальнейшее развитие ПЛМ

• Недостаток классических ПЛМ –фиксированная настройка выходных

макроячеек.

• Совершенствование архитектуры

выходных макроячеек привело к

созданию универсальных ПЛМ.

17. Переход к универсальной ПЛМ

i inputs, j minterms/macrocell, k macrocellsFrom Smith97

18. Архитектура логической ячейки классической универсальной ПЛМ

19. Архитектура классической универсальной ПЛМ

20. Универсальная ПЛМ Atmel

Primary inputsMacrocell

21. Сложные программируемые логические интегральные схемы (CPLD)

• СПЛИС (CPLD ) являются дальнейшим развитиемструктур ПЛМ

• Архитектурно CPLD состоят из центральной

коммутационной матрицы, множества

функциональных логических блоков (универсальных

ПЛМ) и блоков ввода/вывода на периферии

кристалла.

• Ведущими производителями CPLD являются

компании ALTERA, Xilinx, Atmel, Vantis, Cypress

Semicond. и др.

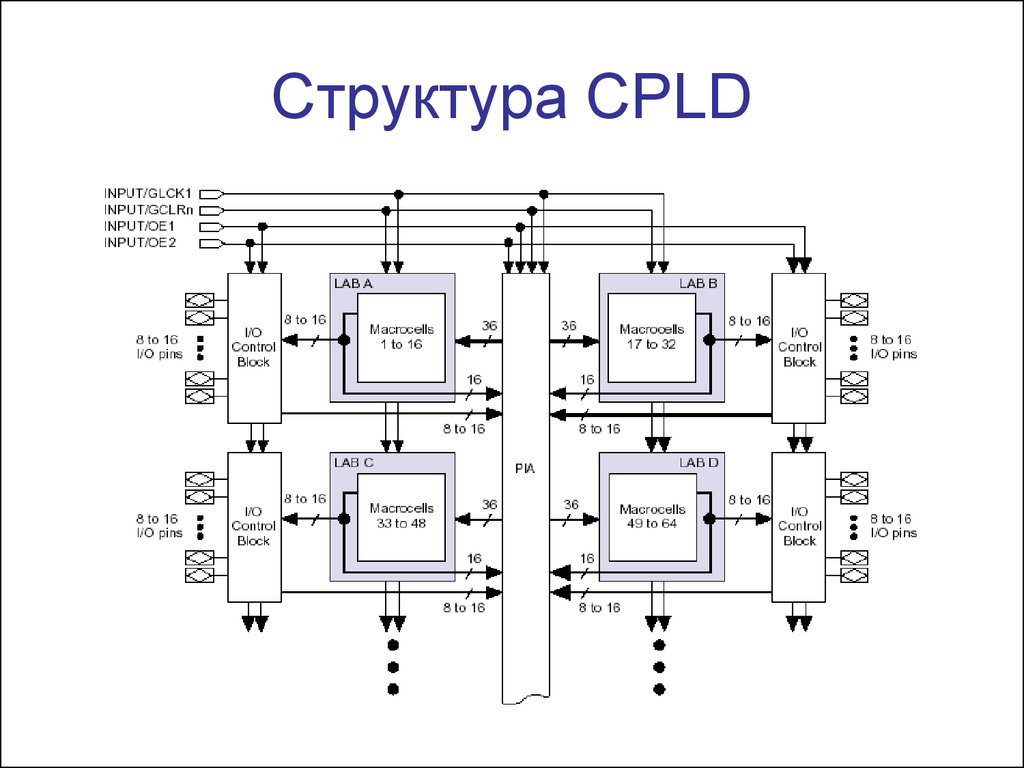

22. Структура CPLD

23. Altera MAX

24. Altera MAX - Способы соединений

column channelrow channel

t PIA

LAB1

LAB2

LAB

PIA

t PIA

Array-based

(MAX 3000-7000)

LAB6

Mesh-based

(MAX 9000)

Courtesy Altera

25. Логическая ячейка CPLD

26. Блок ввода/вывода CPLD

27. Программируемая матрица соединений CPLD

28. Сравнительные характеристики семейств CPLD

29.

30. Базовые матричные кристаллы (БМК)

• БМК относятся к полузаказным ИС. Этополуфабрикат, придание которому индивидуального

характера происходит на заключительных стадиях

производства СБИС.

• Основа БМК – совокупность регулярно

расположенных на кристалле базовых ячеек (БЯ),

между которыми могут располагаться свободные

зоны для создания соединений (каналы).

• БЯ содержат группы нескоммутированных элементов

(транзисторов, резисторов и др.).

• В периферийной области кристалла располагаются

ячейки ввода/вывода.

31. Различные структуры БМК

• Базовая ячейка (1) иканалы связи (2) БМК.

• Канальная структура

БМК (а, б).

• Бесканальная структура

БМК (в).

• Изменяемая структура

БМК (г) – с переменной

длиной ячейки.

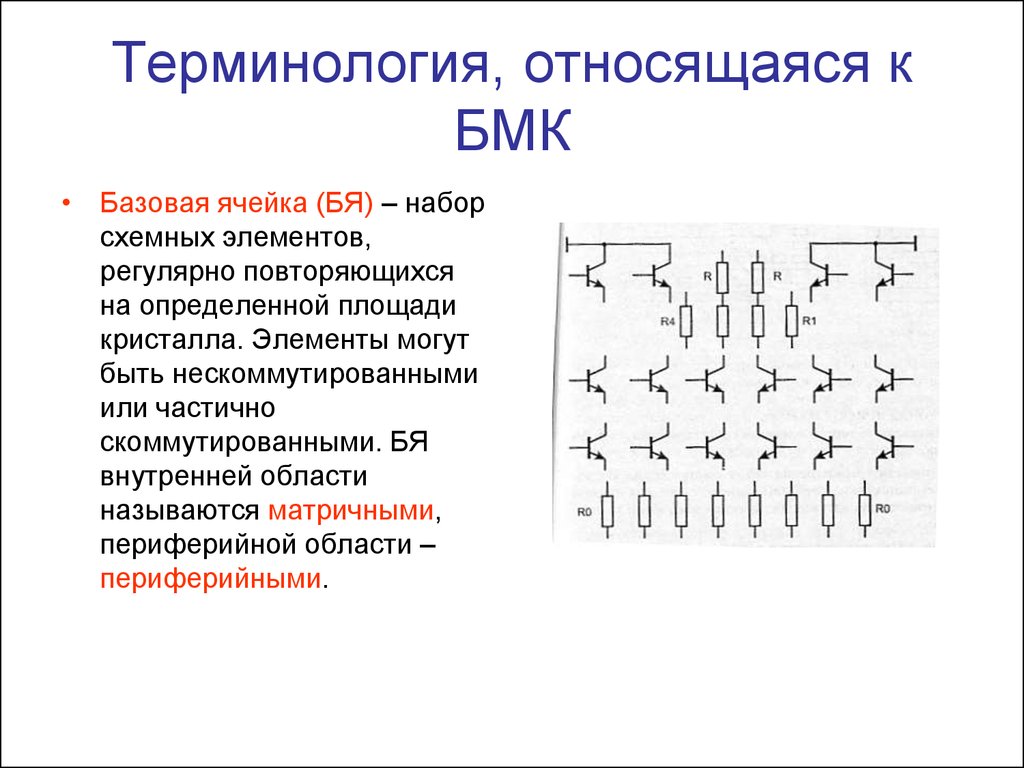

32. Терминология, относящаяся к БМК

• Базовая ячейка (БЯ) – наборсхемных элементов,

регулярно повторяющихся

на определенной площади

кристалла. Элементы могут

быть нескоммутированными

или частично

скоммутированными. БЯ

внутренней области

называются матричными,

периферийной области –

периферийными.

33. Терминология, относящаяся к БМК

• Способы организации ячеек БМК:- Из элементов МБЯ может быть сформирован один

логический элемент, а для реализации более

сложных функций используются несколько ячеек;

- Из элементов МБЯ может быть сформирован

любой функциональный узел, а состав элементов

ячейки определяется схемой самого сложного узла.

• Функциональная ячейка (ФЯ) – функционально

законченная схема, реализуемая путем соединения

элементов в пределах одной или нескольких БЯ.

34. Терминология, относящаяся к БМК

• Библиотека функциональных ячеек – совокупностьФЯ, используемых при проектировании БИС.

Создается на этапе разработки БМК и предоставляет

разработчику готовые схемотехнические решения.

• Эквивалентный вентиль (ЭВ) – группа элементов

БМК, соответствующая возможности реализации

логической функции вентиля (обычно –

двухвходовый элемент И-НЕ или ИЛИ-НЕ).

Используется для оценки логической емкости БМК.

• Каналы трассировки – пути размещения

межсоединений в БМК.

35. Терминология, относящаяся к БМК

• Пример библиотекифункциональных

ячеек БМК фирмы

Actel

36. Терминология, относящаяся к БМК

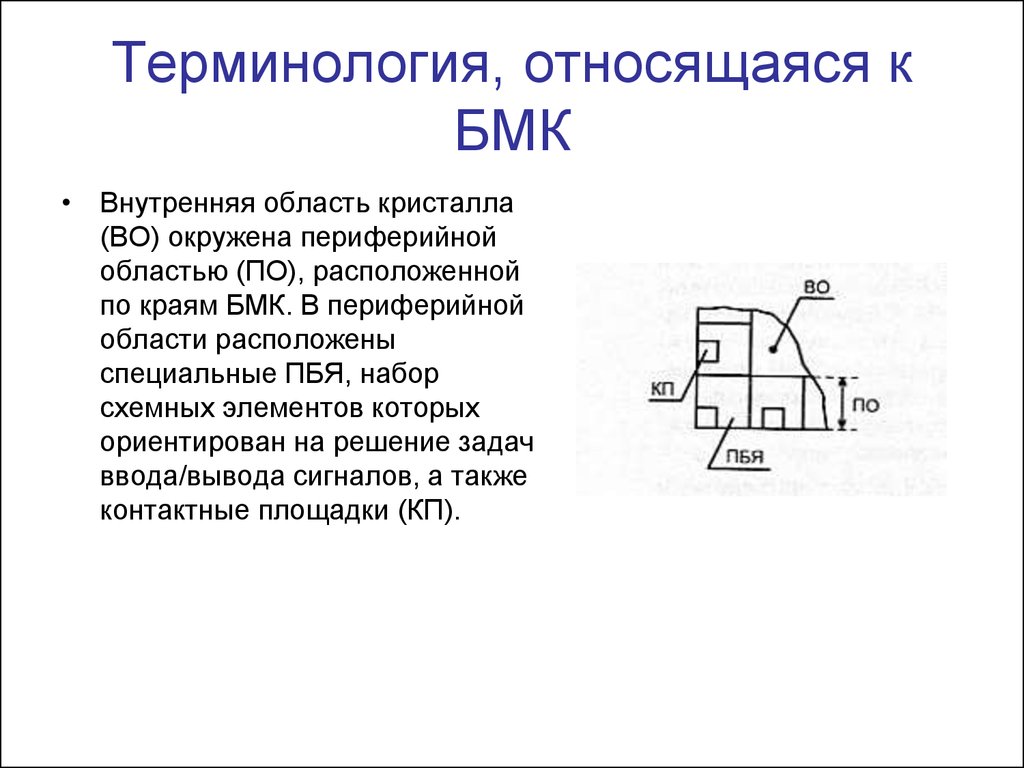

• Внутренняя область кристалла(ВО) окружена периферийной

областью (ПО), расположенной

по краям БМК. В периферийной

области расположены

специальные ПБЯ, набор

схемных элементов которых

ориентирован на решение задач

ввода/вывода сигналов, а также

контактные площадки (КП).

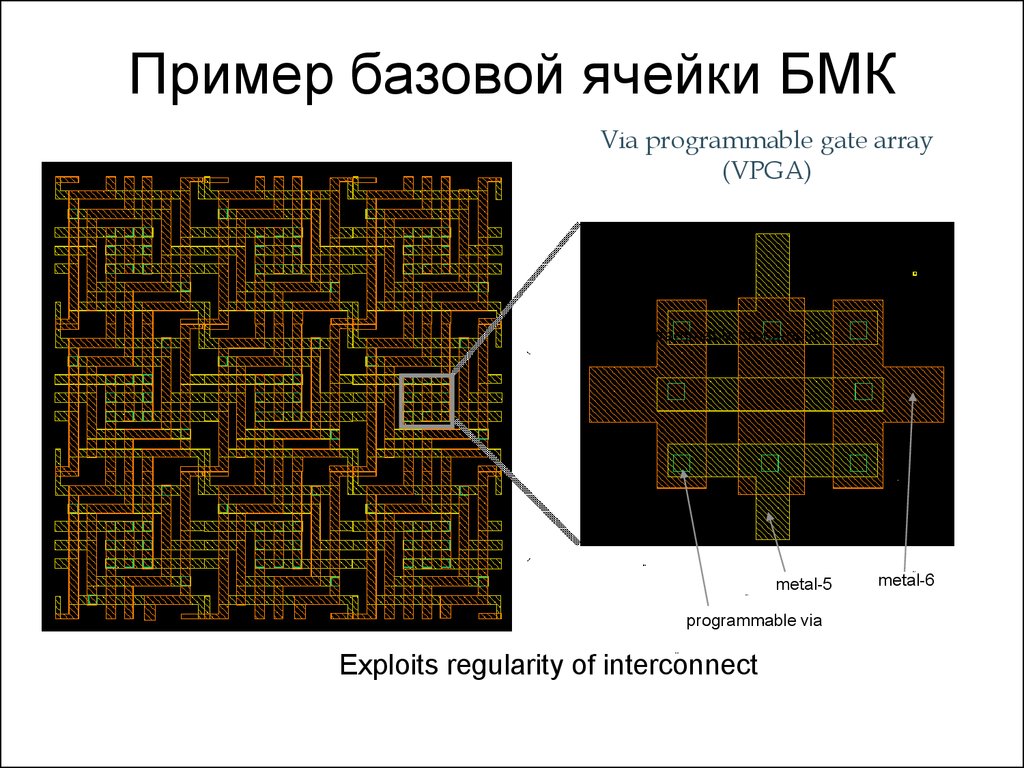

37. Пример базовой ячейки БМК

Via programmable gate array(VPGA)

Via-programmable cross-point

metal-5

programmable via

Exploits regularity of interconnect

metal-6

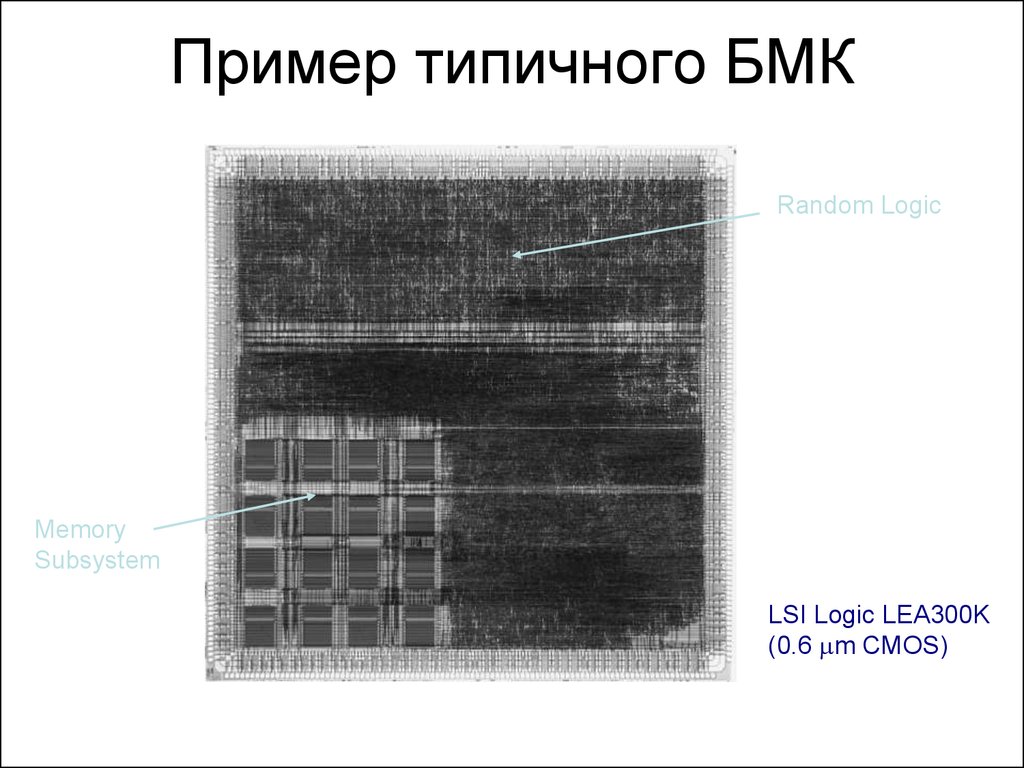

38. Пример типичного БМК

Random LogicMemory

Subsystem

LSI Logic LEA300K

(0.6 mm CMOS)

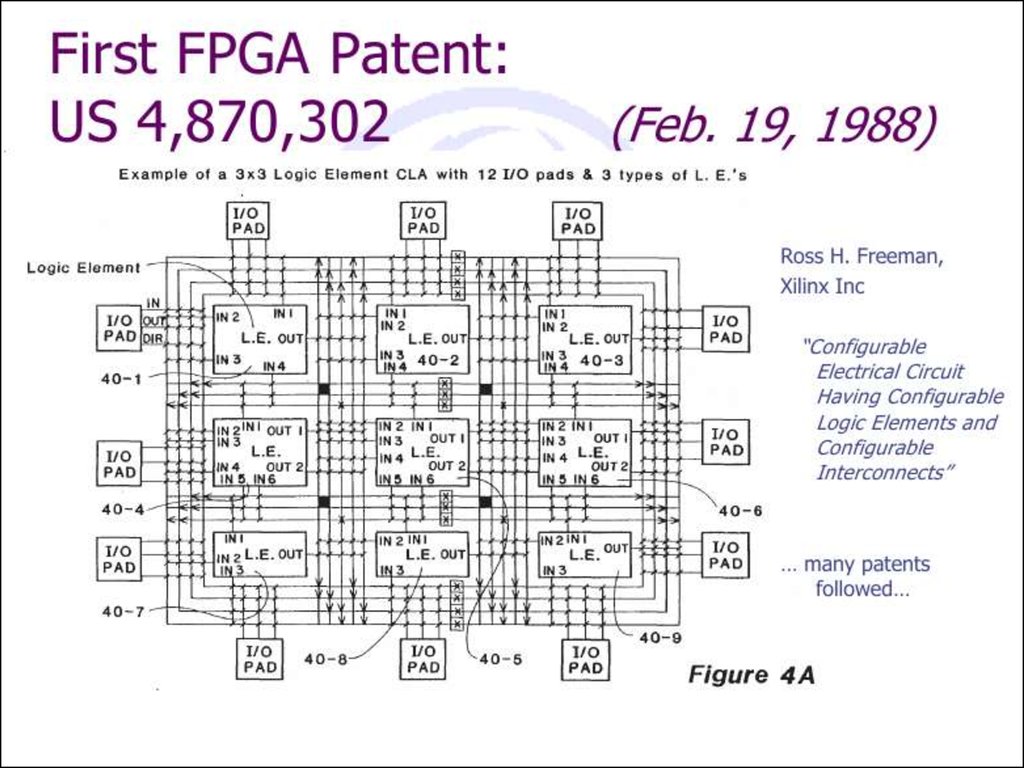

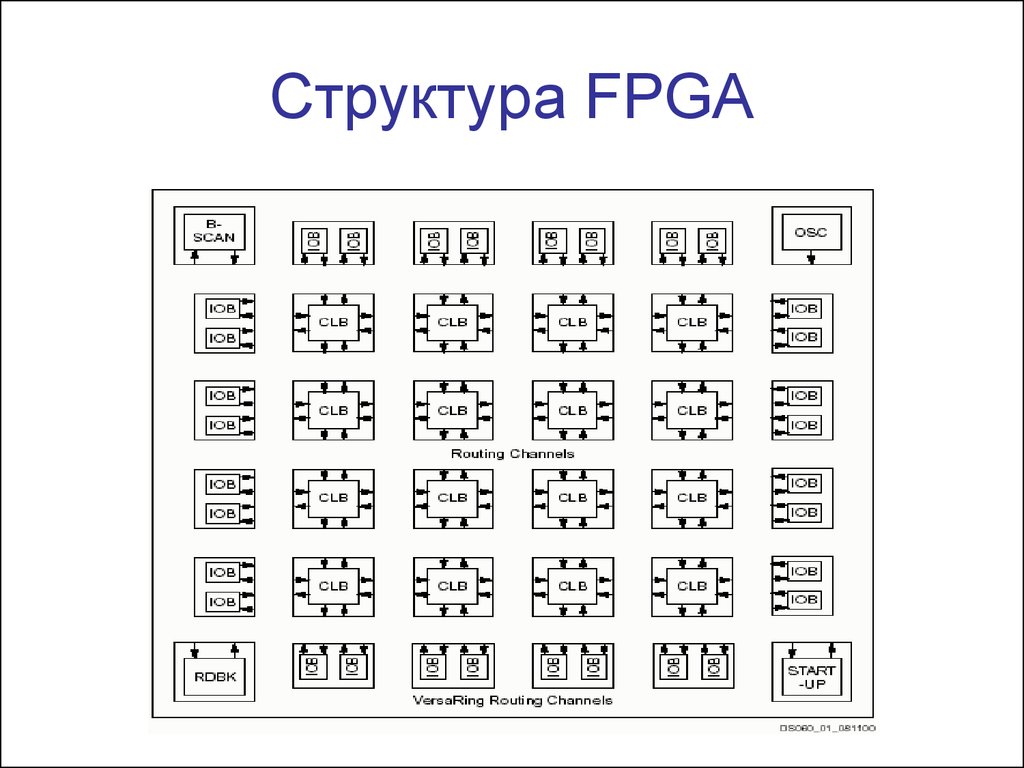

39. Программируемые пользователем вентильные матрицы (FPGA)

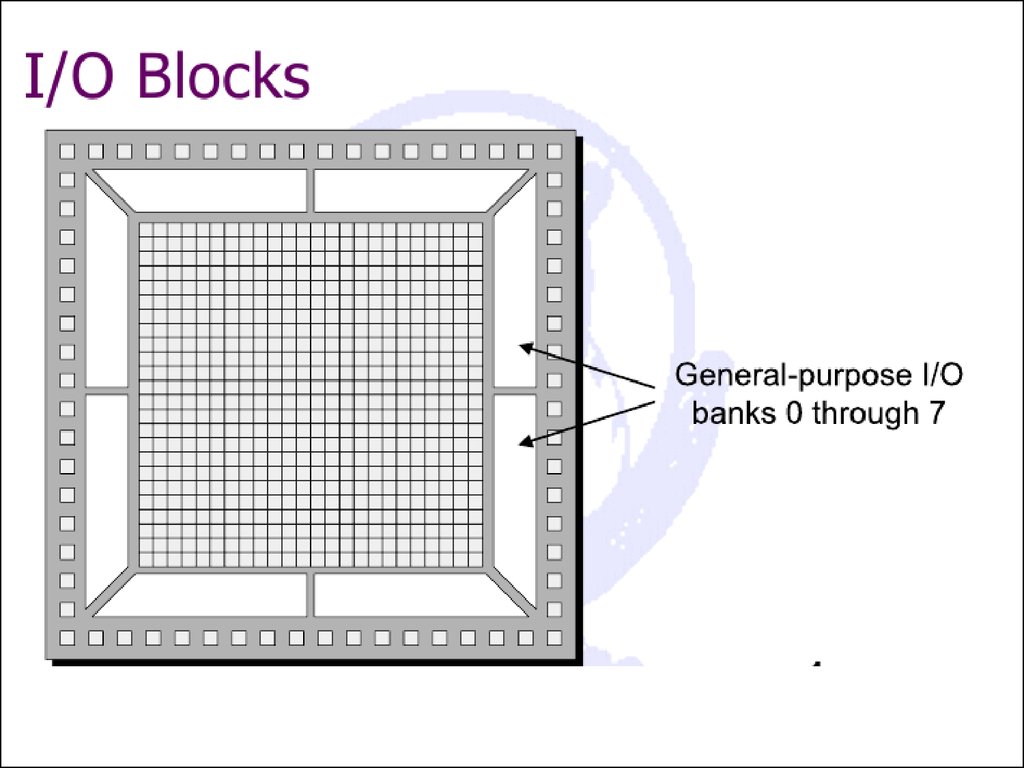

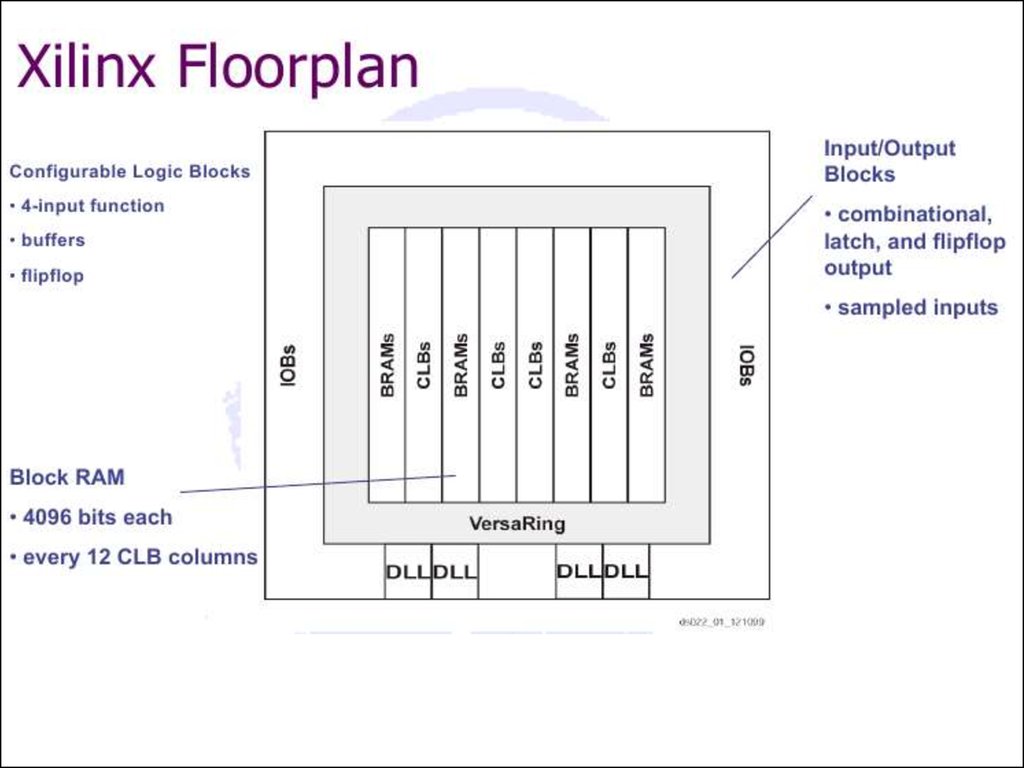

• Топологически сходны с канальными БМК• Во внутренней области размещается множество

регулярно расположенных идентичных

конфигурируемых логических блоков (КЛБ)

• Между КЛБ проходят трассировочные каналы

• На периферии кристалла расположены блоки

ввода\вывода

40.

41. Структура FPGA

42. Структура логического блока FPGA

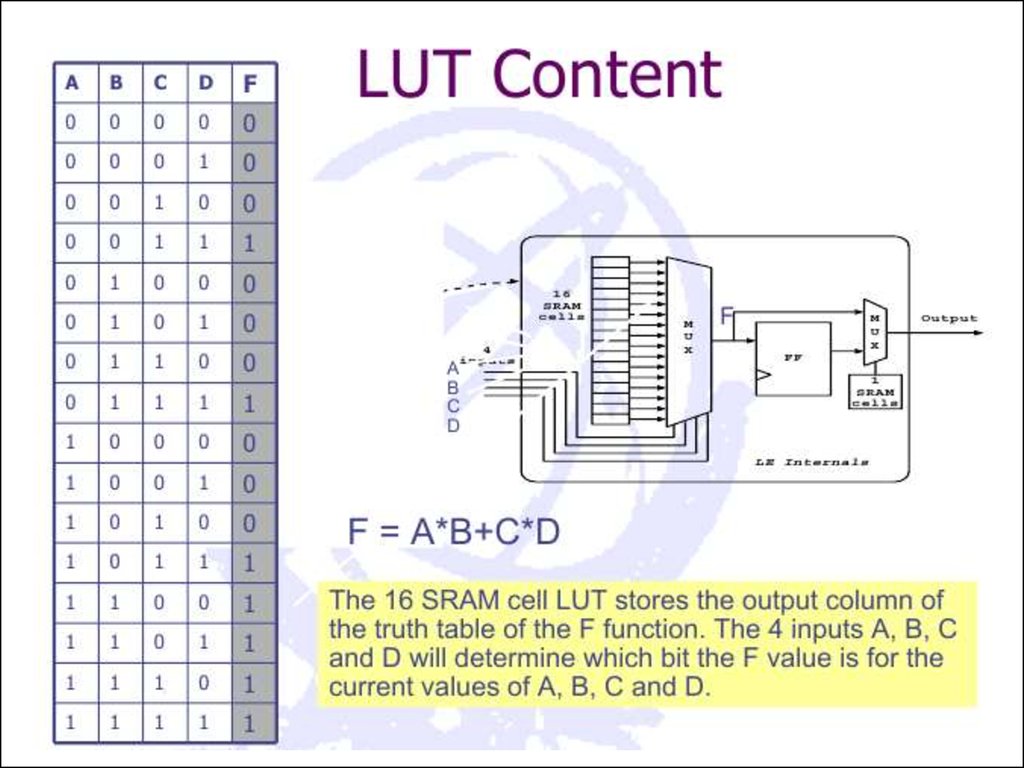

• Свойства и возможности FPGA зависят в первуюочередь от характера их КЛБ и системы

межсоединений

• В качестве КЛБ могут использоваться:

- транзисторные пары (SLC – Simple Logic Cells);

- мультиплексоры;

- программируемые ПЗУ (LUTs – Look-Up Tables)

43. Структура логического блока FPGA

• Пример логическогоблока на основе

транзисторных пар

• Реализуемая функция:

F x1 x2 x3 x4

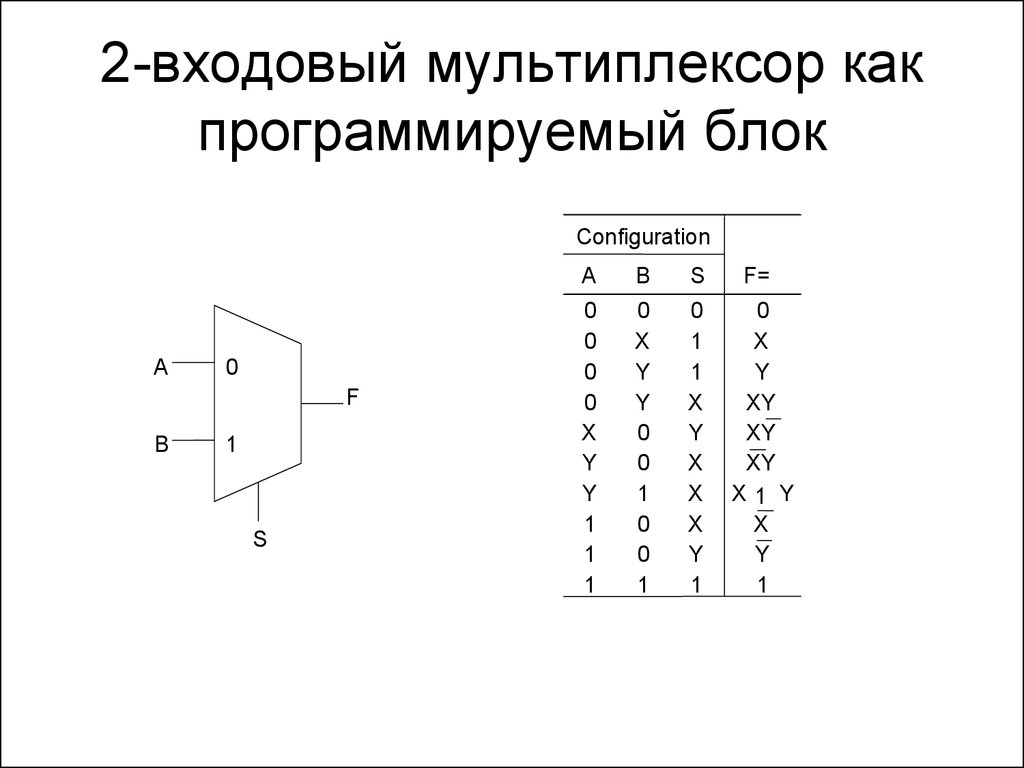

44. 2-входовый мультиплексор как программируемый блок

ConfigurationA

0

F

B

1

S

A

B

S

F=

0

0

0

0

X

Y

Y

1

1

1

0

X

Y

Y

0

0

1

0

0

1

0

1

1

X

Y

X

X

X

Y

1

0

X

Y

XY

XY

XY

X1 Y

X

Y

1

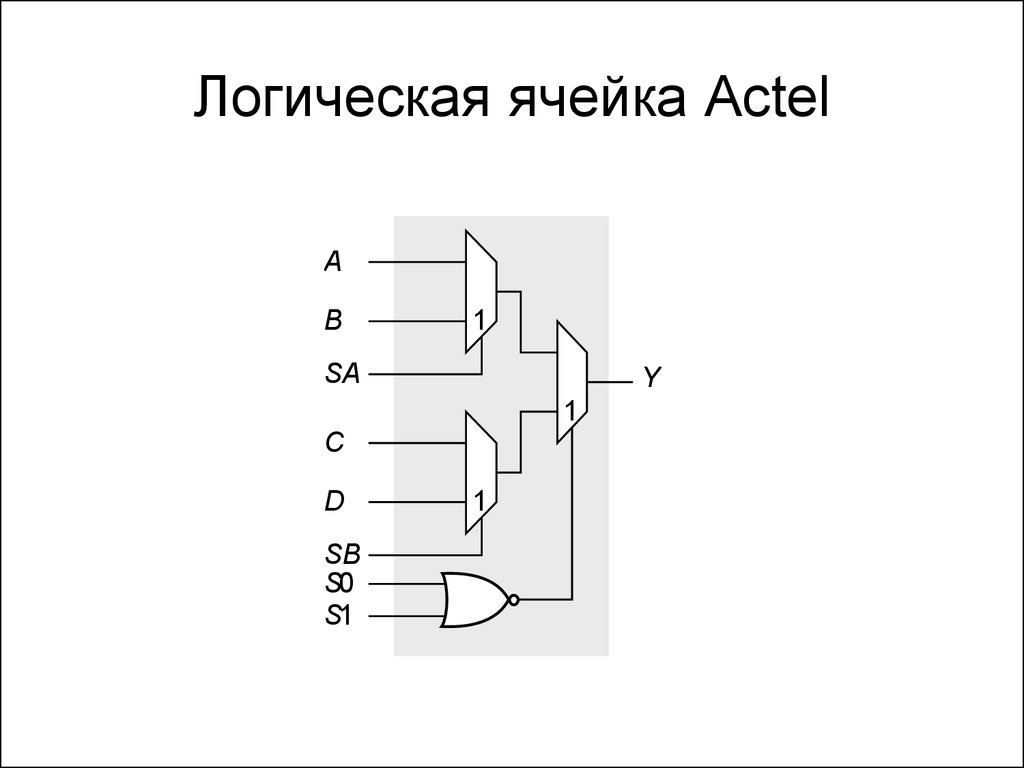

45. Логическая ячейка Actel

AB

1

SA

Y

1

C

D

SB

S0

S1

1

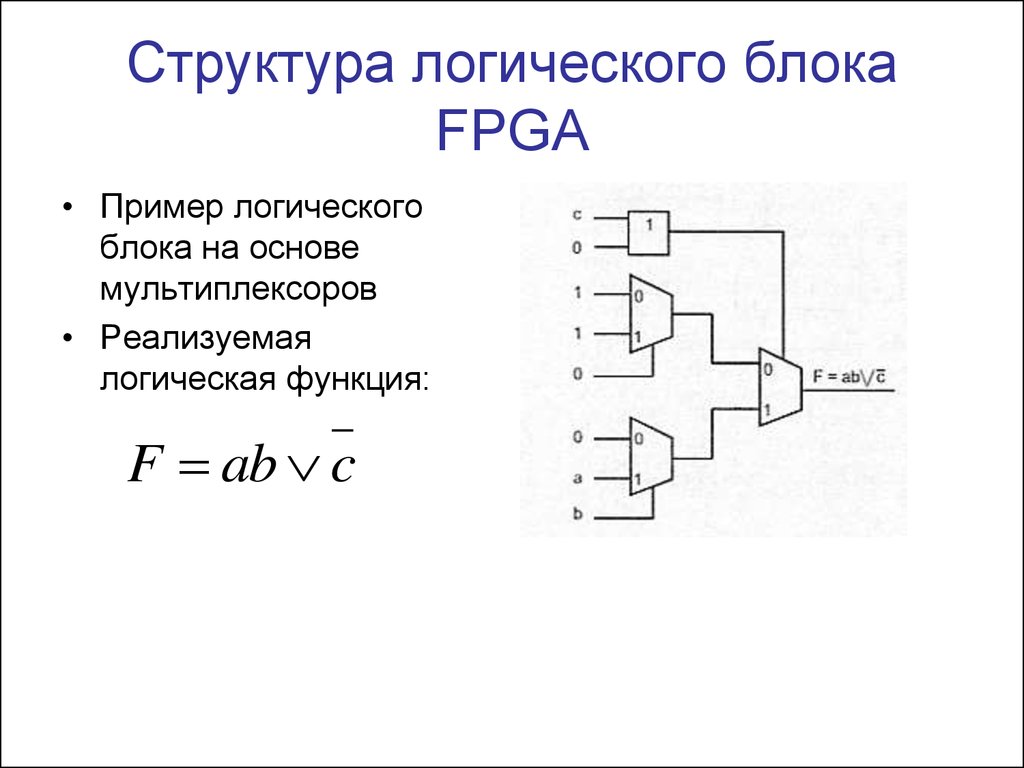

46. Структура логического блока FPGA

• Пример логическогоблока на основе

мультиплексоров

• Реализуемая

логическая функция:

F ab c

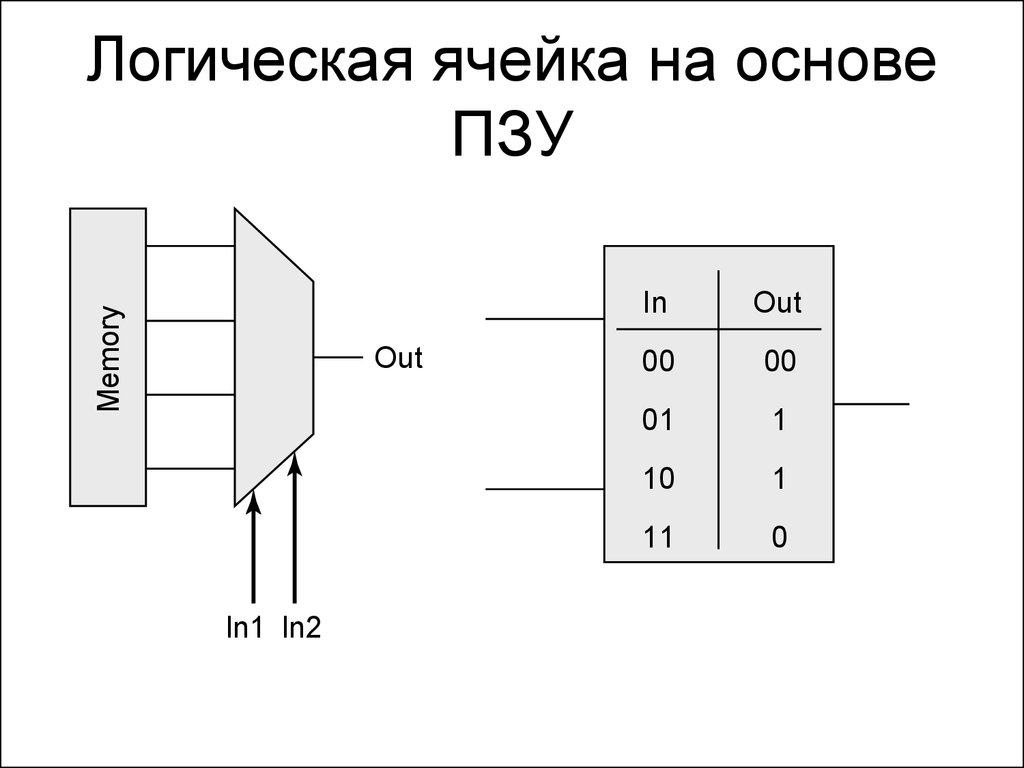

47. Логическая ячейка на основе ПЗУ

MemoryЛогическая ячейка на основе

ПЗУ

Out

ln1 ln2

In

Out

00

00

01

1

10

1

11

0

48.

49.

50.

51.

52. Структура логического блока FPGA на основе ПЗУ

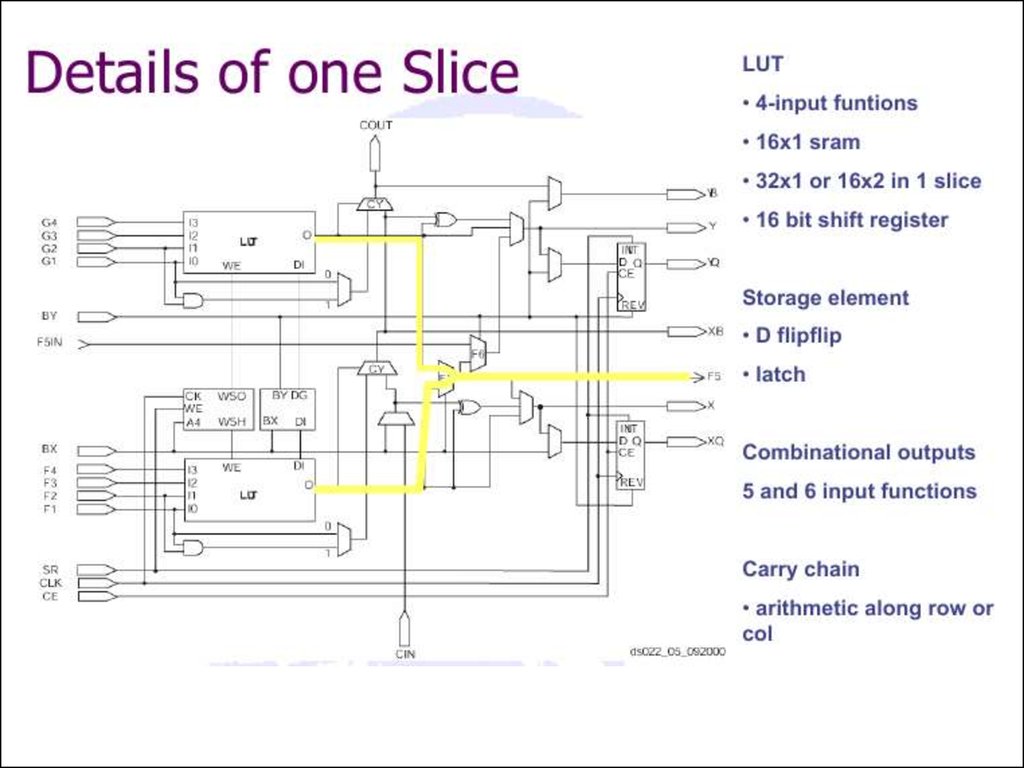

53.

54.

55. Блок ввода/вывода FPGA

56. Система соединений FPGA

57. Структура переключательного блока (PSM) FPGA

58. Пример создания связи в FPGA

59.

60.

61.

62.

63.

64. Дополнительные блоки FPGA

• Встроенные блокипамяти (небольшого

объема) – 16х1 или

32х1 бит

65. Дополнительные блоки FPGA

• Блок интерфейсаграничного

сканирования

(JTAG) – для

отладки и

конфигурирования

FPGA

66.

67. Характеристики семейства FPGA

• Микросхемы FPGA построены по SRAM-технологии итребуют загрузки управляющей (конфигурационной)

программы либо из внешнего ПЗУ, либо из другого

устройства

• Широко используются при построении

реконфигурируемых систем, при решении задач

логической эмуляции, и пр.

68. Пример кристалла FPGA

Xilinx XC4000ex69.

70.

71. Характеристики семейства FPGA

72. Системы на кристалле (SoC)

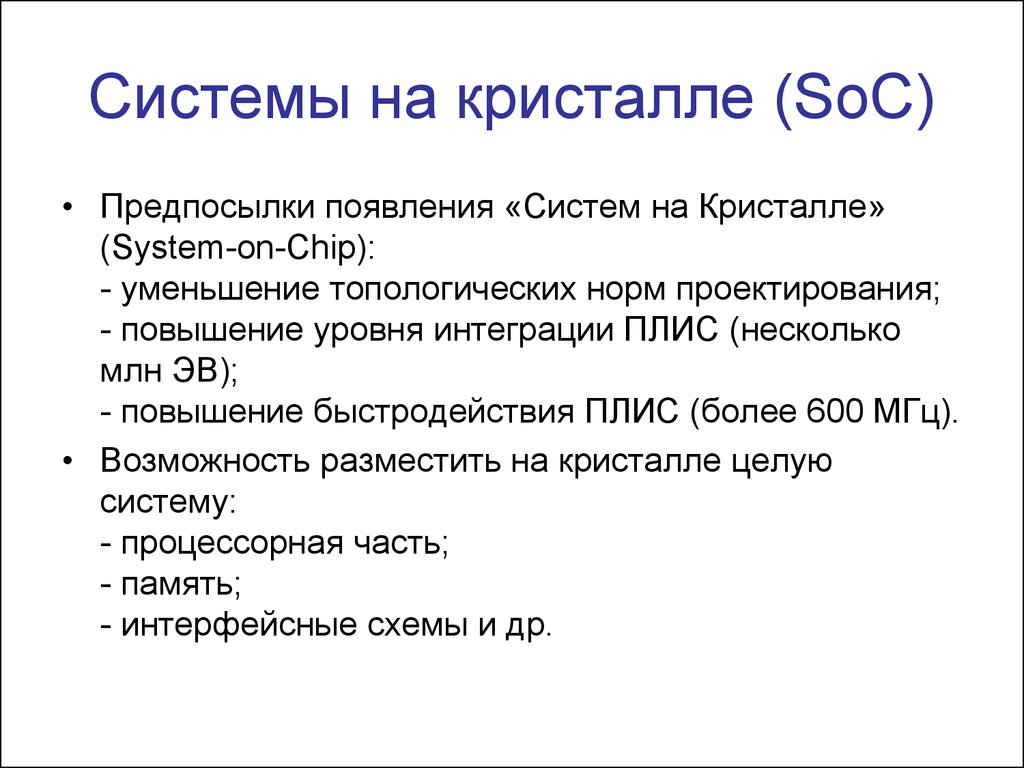

• Предпосылки появления «Систем на Кристалле»(System-on-Chip):

- уменьшение топологических норм проектирования;

- повышение уровня интеграции ПЛИС (несколько

млн ЭВ);

- повышение быстродействия ПЛИС (более 600 МГц).

• Возможность разместить на кристалле целую

систему:

- процессорная часть;

- память;

- интерфейсные схемы и др.

73. Пример системы на кристалле

74. Системы на кристалле (SoC)

• Архитектурные особенности SoC:- наличие универсальных программируемых блоков,

позволяющих реализовать любое устройство

(generic);

- наличие специализированных областей

(аппаратных ядер), выделенных на кристалле для

определенных функций (hardcores).

• Введение специализированных аппаратных ядер

сокращает площадь кристалла при реализации

сложных функций и увеличивает быстродействие.

75. Системы на кристалле (SoC)

• К специализированным ядрам относятся:- блоки ОЗУ с возможностью изменения организации

памяти, выбора асинхронного и синхронного режима

работы и др.;

- умножители;

- схемы интерфейса (JTAG, PCI и пр.);

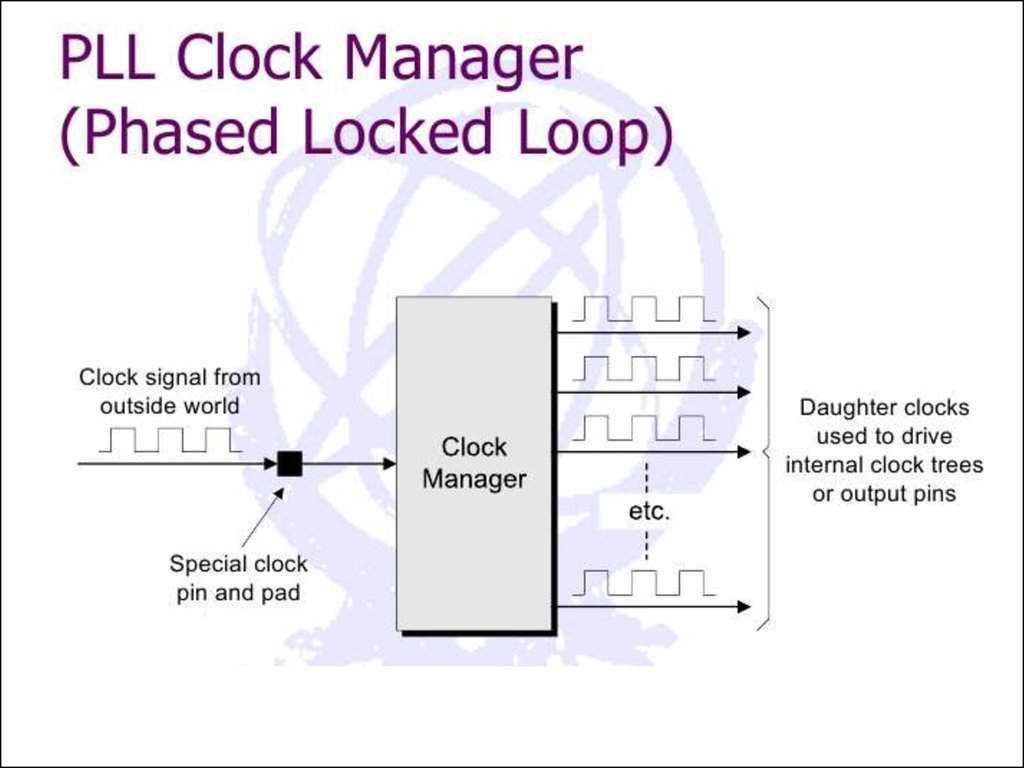

- схемы формирования тактовых сигналов (PLL, DLL).

76. Структура SoC ALTERA

77. Структура SoC XILINX

FPGA FabricEmbedded memories

Embedded PowerPc

Hardwired multipliers

Xilinx Vertex-II Pro

High-speed I/O

Courtesy Xilinx

78. Логическая ячейка SoC

79. Режимы настройки логической ячейки

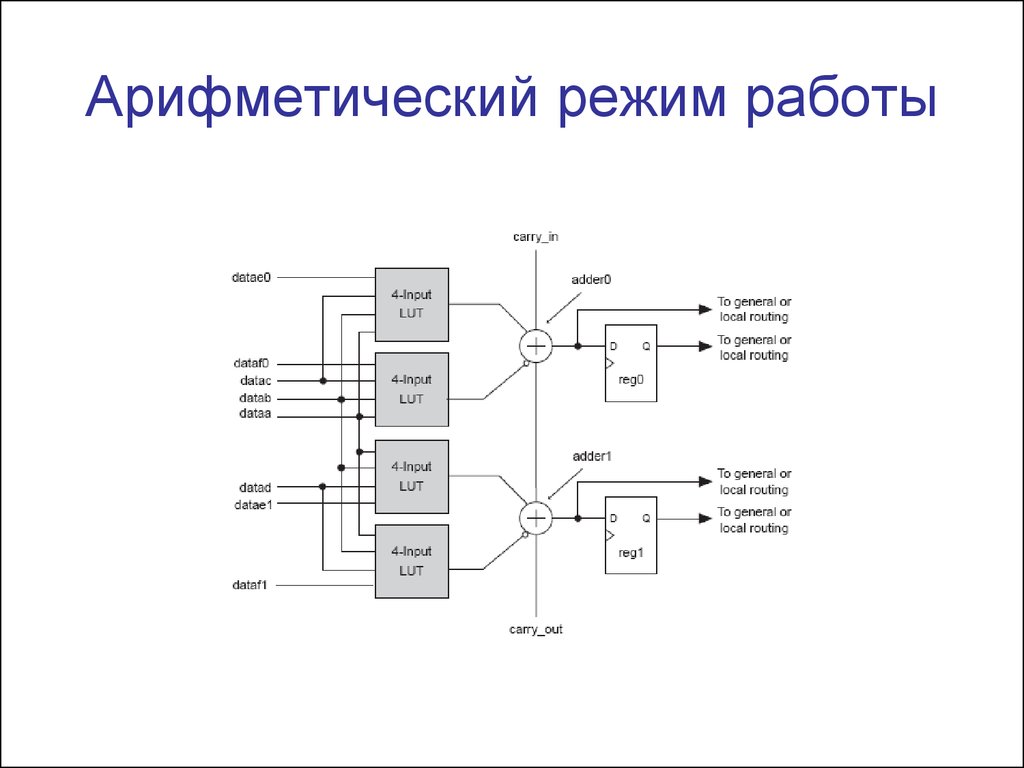

80. Арифметический режим работы

81. Организация регистровой цепочки

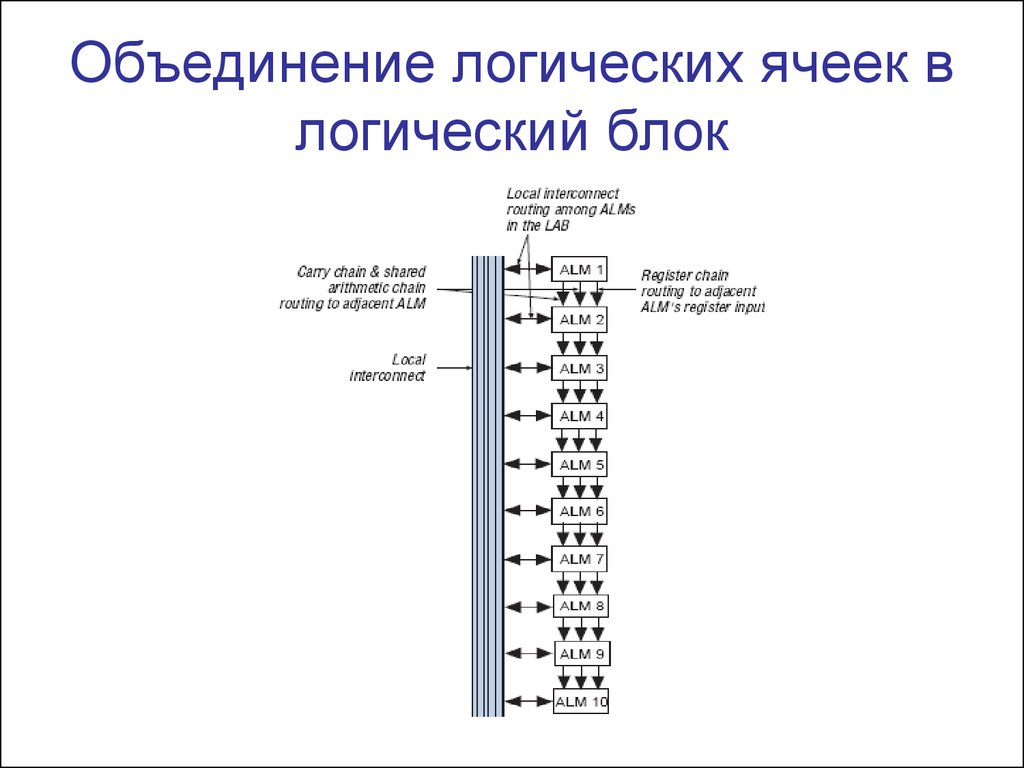

82. Объединение логических ячеек в логический блок

83. Блок памяти SoC

84. Конфигурационные возможности блока памяти

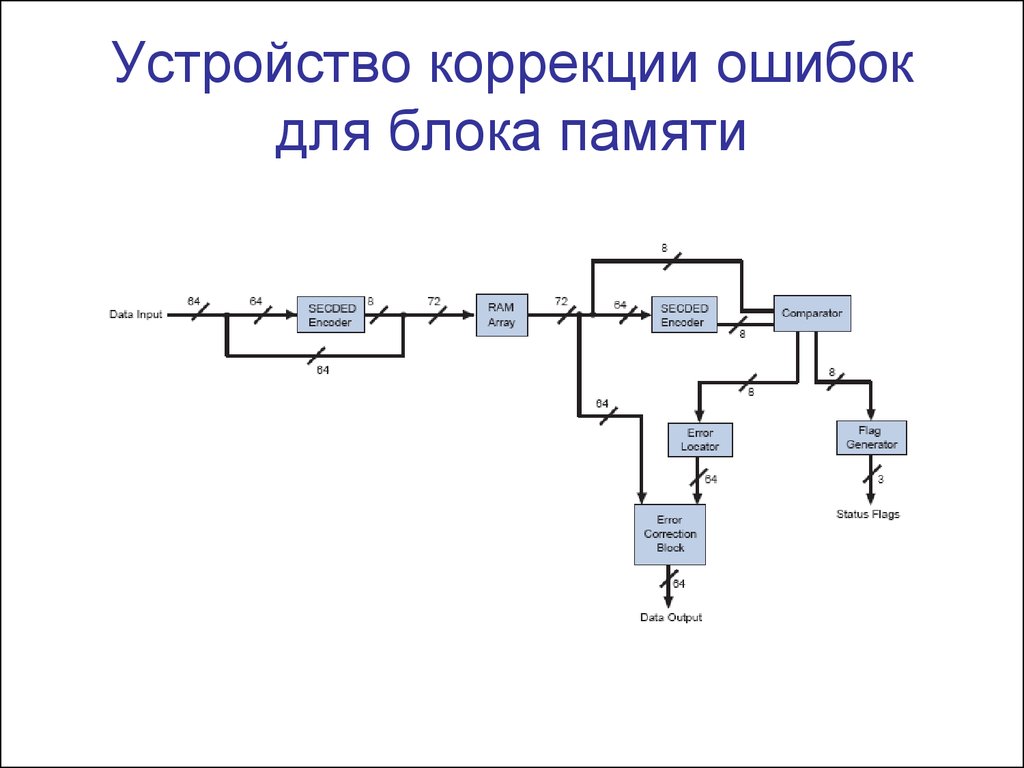

85. Устройство коррекции ошибок для блока памяти

86. Блок памяти в режиме сдвигового регистра

87. Арифметический блок SoC

88. Архитектурные особенности арифметического блока

89. Последовательная загрузка данных в арифметическом блоке

90. Формирование обратной связи в арифметическом блоке

91. Блок управления тактовыми сигналами SoC

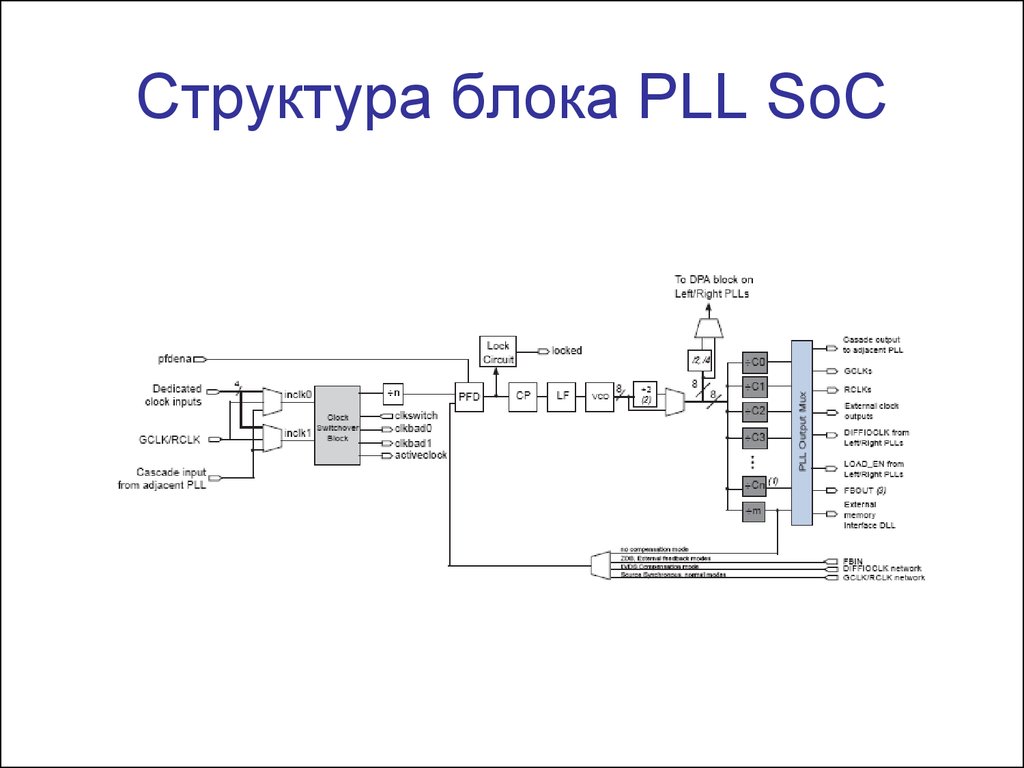

92. Структура блока PLL SoC

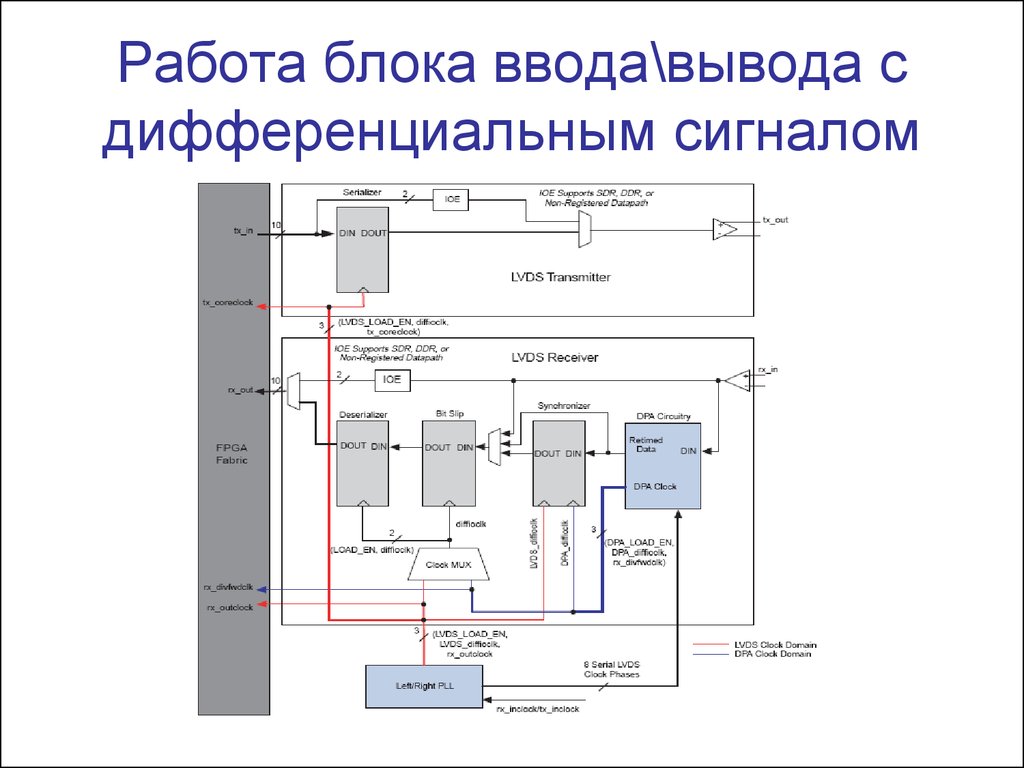

93. Блок ввода\вывода SoC

94. Работа блока ввода\вывода с дифференциальным сигналом

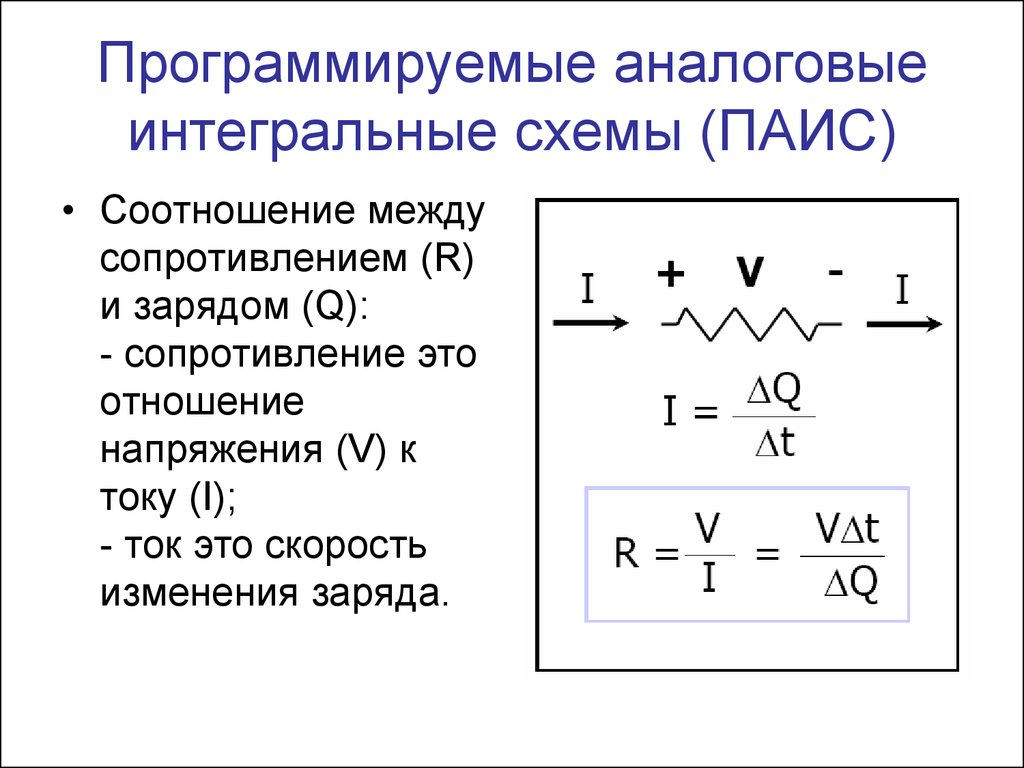

95. Программируемые аналоговые интегральные схемы (ПАИС)

• Соотношение междусопротивлением (R)

и зарядом (Q):

- сопротивление это

отношение

напряжения (V) к

току (I);

- ток это скорость

изменения заряда.

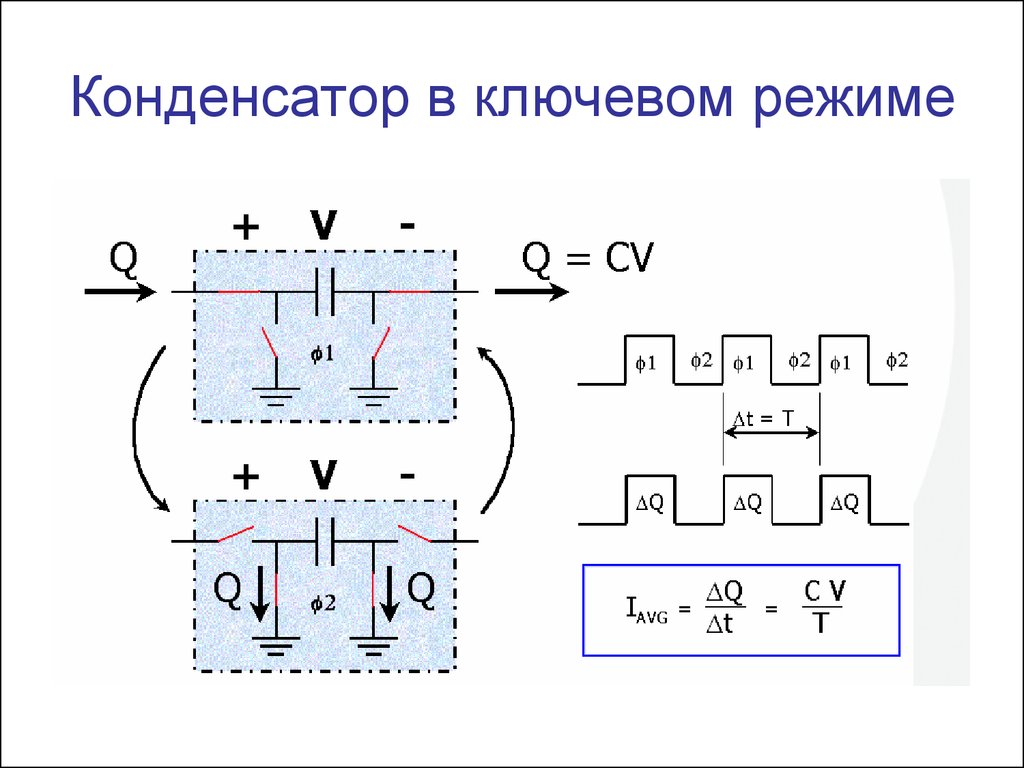

96. Конденсатор в ключевом режиме

97. Переключамый конденсатор как резистор

• Сопротивление обратнопропорционально емкости и

частоте

• Отношение сопротивлений

зависит только от отношения

емкостей

• Резистор можно заменить

конденсатором

• Особенности:

- зависимость от частоты;

- изменение фазы

98. Изменение фазы (знака сопротивления)

99. Настройка собственной частоты изменением частоты переключения

100. Дискретизация входного сигнала

• Входной и выходнойсигналы обрабатываются

в разные моменты

времени

• Удобно для создания

устройств дискретизации

(напр. – АЦП)

101. Соотношение напряжений в схеме с переключаемыми конденсаторами

102. Переключаемые конденсаторы – базовый элемент ПАИС

• Они позволяют реализовывать:- изменение коэффициента усиления

операционных усилителей;

- регулировать скорость нарастания фронта

сигнала;

- выполнять фильтрацию аналогового

сигнала;

- создавать устройства дискретизации

входного сигнала и т.д.

103. Простые ПАИС

• Схема простой ПАИСispPAC10 фирмы Lattice

Semi

• Позволяет создавать

различные усилители,

интеграторы, простые

фильтры

104. Программируемый аналоговый блок (реализация фильтра)

105. Простые ПАИС (ispPAC20)

106. Простые ПАИС

• СпециализированнаяПАИС (ispPAC80) –

предназначена для

реализации ФНЧ 5-го

порядка

107. Упрощенная схема ПАИС для реализации ФНЧ

108. Архитектура сложной конфигурируемой аналоговой матрицы фирмы Anadigm

109. Структура входной ячейки

110. Структура выходной ячейки

111. Структура конфигурируемого аналогового блока

112. Программируемые матрицы смешанной архитектуры

• В их состав обычно включают:- аппаратно реализованное

процессорное ядро;

- программируемые цифровые блоки;

- программируемые аналоговые блоки;

- специализированные блоки

Электроника

Электроника