Похожие презентации:

Архитектура ЭВМ и систем. Логические основы ЭВМ

1. Архитектура ЭВМ и систем

Лекция 62. Логические основы ЭВМ

Базовые функциональные элементыЭВМ (вентили)

Основные логические схемы

3. Вентили

Логический элемент - электронное устройство,на входах и выходах которого сигнал может

иметь только один из двух дискретных уровней

напряжения: низкий (0–2V) или высокий (3–5V).

Базовым считают элемент с наиболее простой

структурой, на основе которого легче всего

создавать другие электронные схемы.

И, ИЛИ, НЕ

И-НЕ

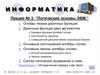

4. Инвертор

(вентиль НЕ)Обозначения

х

НЕ

x

Таблица истинности

х

x

0

1

1

0

5. Дизъюнктор

(вентиль ИЛИ)Обозначения

х1

х2

ИЛИ

y

х1

х2

V

y

Таблица истинности

X1

0

0

1

1

X2

0

1

0

1

Y

0

1

1

1

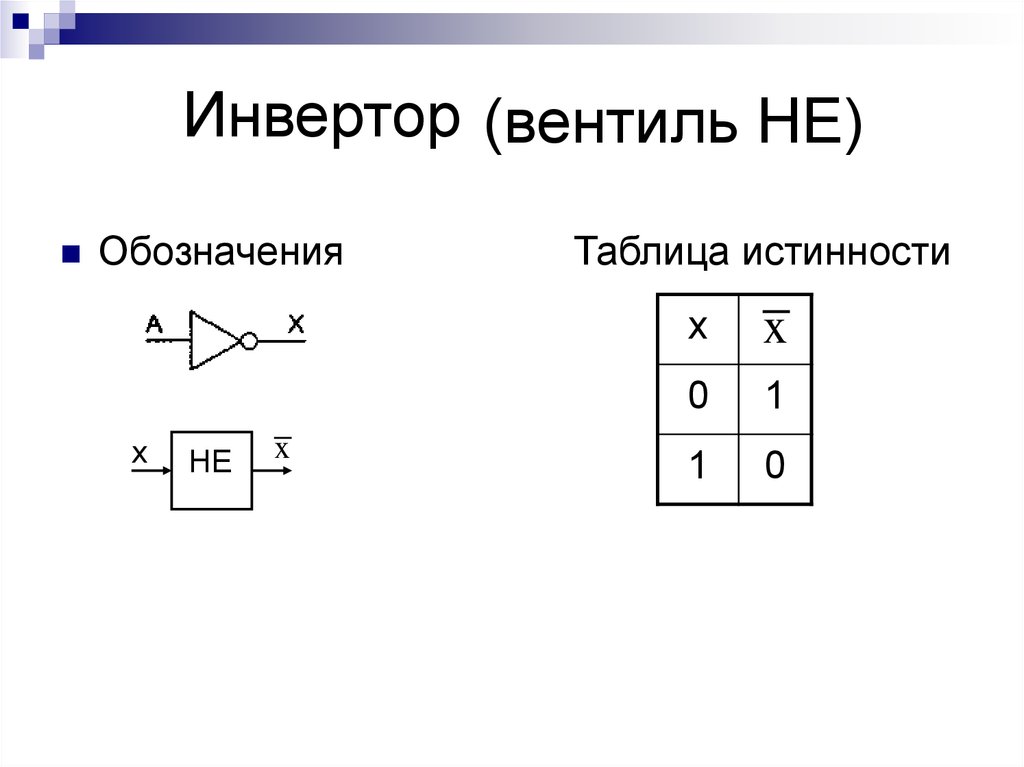

6. Конъюнктор

(вентиль И)Обозначения

х1

х2

И

y

х1

х2

&

y

Таблица истинности

X1

0

0

1

1

X2

0

1

0

1

Y

0

0

0

1

7. Вентили НЕ-И и НЕ-ИЛИ

ОбозначениеНЕ-И

НЕ-ИЛИ

Таблица истинности

X1

0

0

1

1

X2 НЕ-И НЕ-ИЛИ

0

1

1

1

1

0

0

1

0

1

0

0

8. Уровень физических устройств

Транзистор имеет три соединенияс внешним миром: коллектор, базу

и эмиттер.

Если входное напряжение Vin

низкое, то транзистор

выключается и действует как

очень большое сопротивление.

Это приводит к выходному сигналу

Vout, близкому к Vcc (обычно +5В).

Если Vin высокое, то транзистор

включается и действует как

провод, вызывая заземление

сигнала Vout (по соглашению 0 В).

На переключение с одного

состояние на другое обычно

требуется несколько наносекунд.

9. Техническая схема вентилей

И, ИЛИ - ?НЕ

НЕ-И

НЕ-ИЛИ

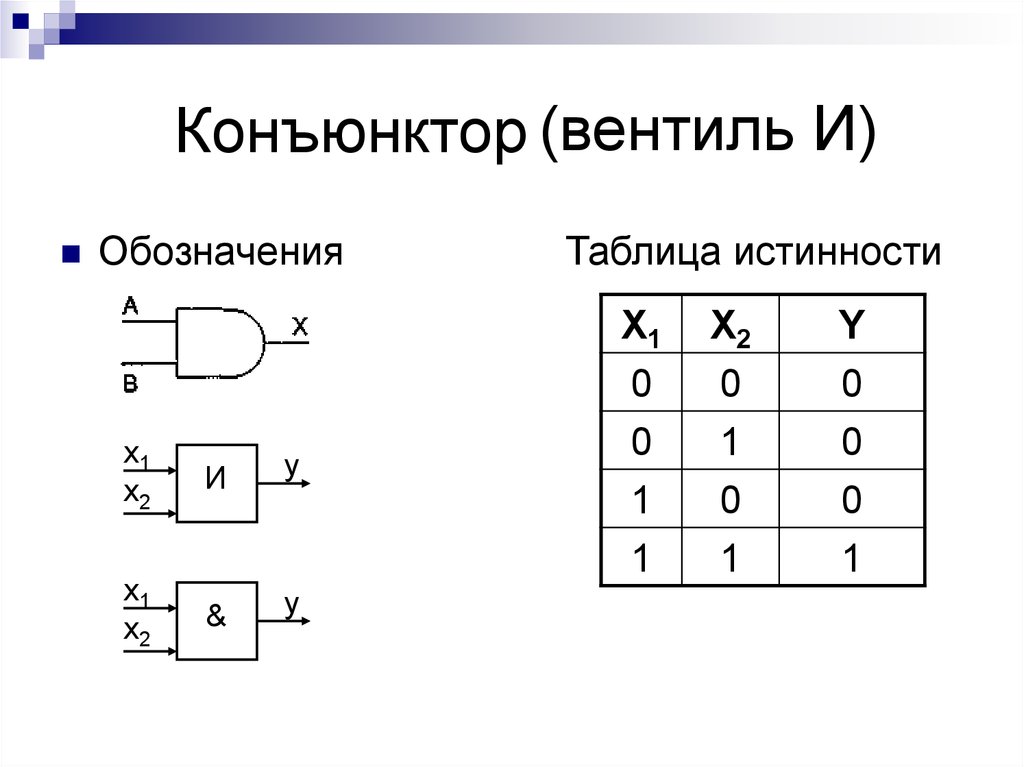

10. Конструирование вентилей НЕ, И, ИЛИ с использованием только НЕ-И

НЕИ

ИЛИ

11. Конструирование вентилей НЕ, И, ИЛИ с использованием только НЕ-ИЛИ

НЕИ

ИЛИ

12. Логический синтез схем

Одноразрядный двоичный полусумматорПолный одноразрядный сумматор

Полный многоразрядный сумматор

Дешифратор

Триггер

13. Как реализовать схему

Составить таблицу истинности для даннойфункции

Обеспечить инверторы, чтобы порождать

инверсии для каждого входного сигнала.

Нарисовать вентиль И для каждой строки

таблицы истинности с результатом 1.

Соединить вентили И с соответствующими

входными сигналами.

Вывести выходы всех вентилей И в вентиль

ИЛИ.

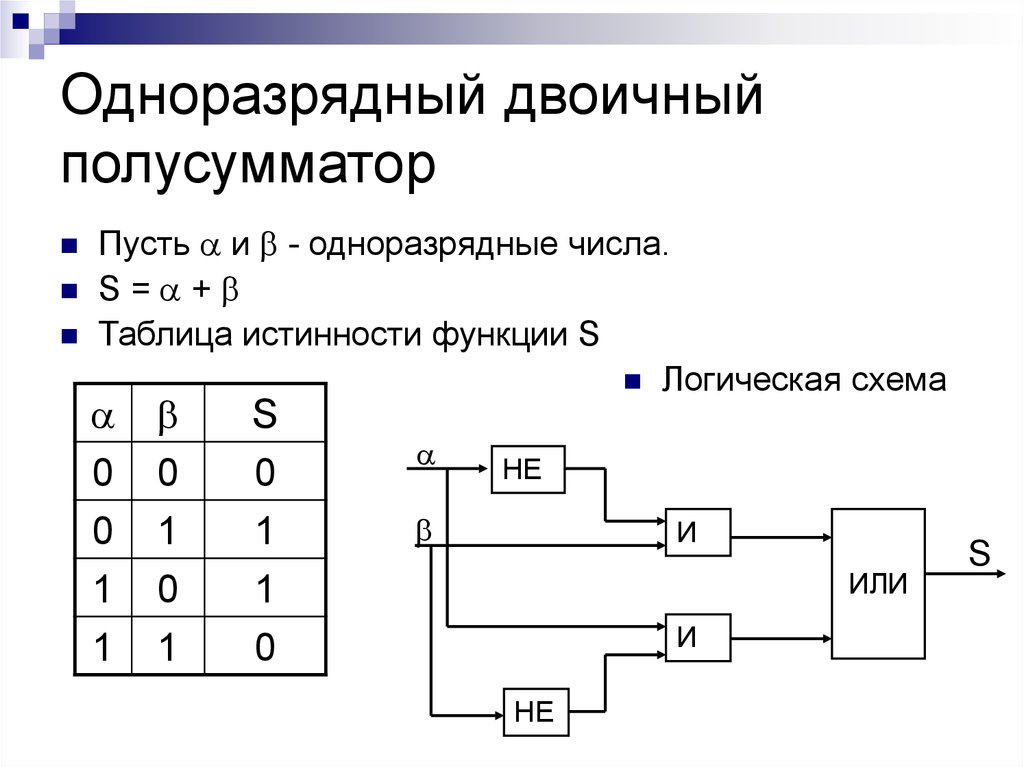

14. Одноразрядный двоичный полусумматор

Пусть и - одноразрядные числа.S= +

Таблица истинности функции S

Логическая схема

0

0

1

1

0

1

0

1

S

0

1

1

0

НЕ

И

ИЛИ

И

НЕ

S

15. Одноразрядный двоичный полусумматор (продолжение)

Добавим функцию P – цифра переноса в следующий(старший) разряд.

Таблица истинности функции Р

Логическая схема

0

0

1

1

0

1

0

1

Р

0

0

0

1

16. Полный одноразрядный сумматор

— полусумматор, дополненный третьимвходом – значением разряда переноса из

соседнего младшего разряда.

i

Si

Таблица истинности

i

i

0

0

0

0

1

1

1

1

i

0

0

1

1

0

0

1

1

Рi

0

1

0

1

0

1

0

1

Si

0

1

1

0

1

0

0

1

Рi+1

0

0

0

1

0

1

1

1

pi

Pi+1

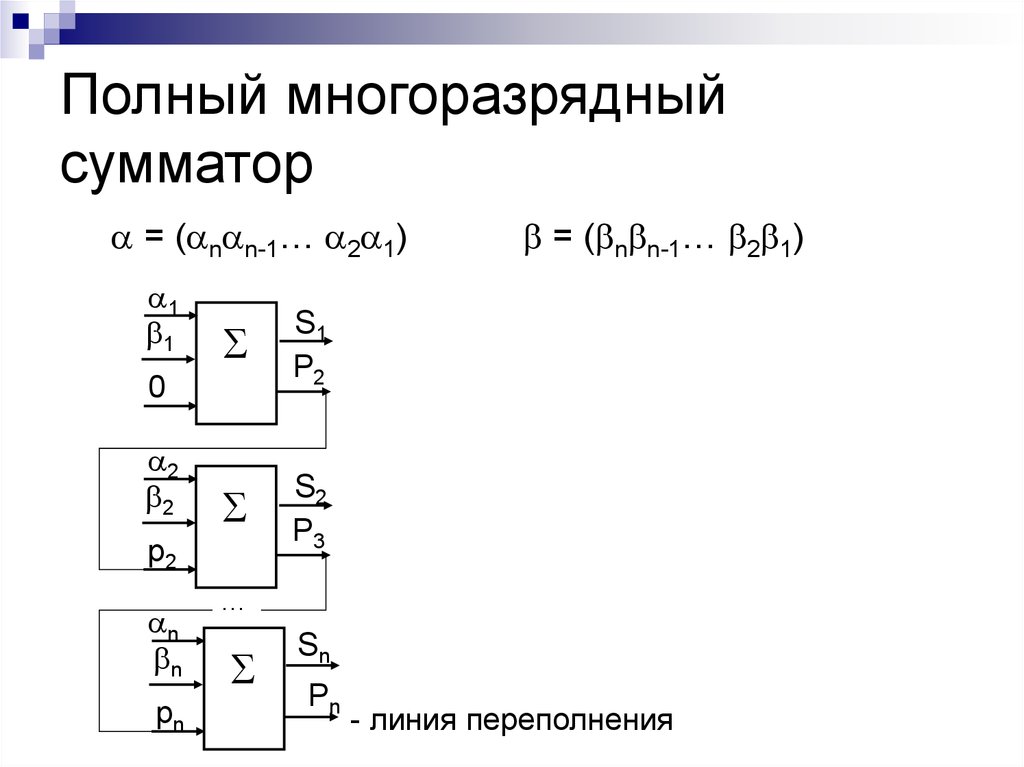

17. Полный многоразрядный сумматор

= ( n n-1… 2 1)1

1

S1

P2

S2

P3

0

2

2

p2

n

n

pn

= ( n n-1… 2 1)

…

Sn

Pn

- линия переполнения

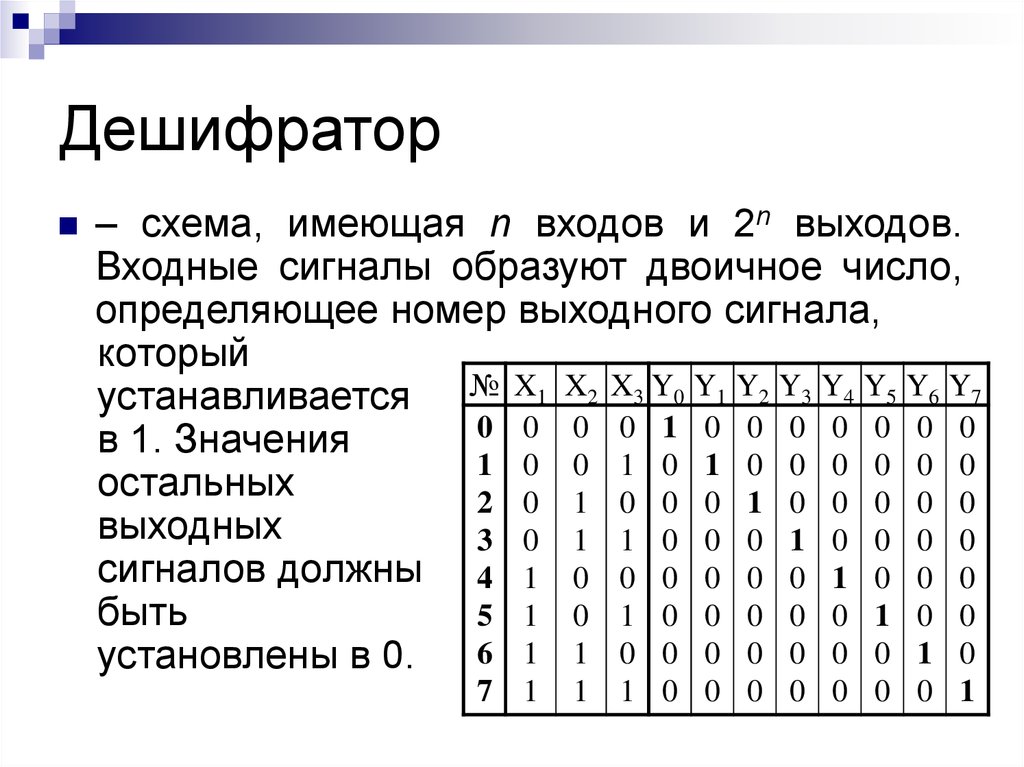

18. Дешифратор

– схема, имеющая n входов и 2n выходов.Входные сигналы образуют двоичное число,

определяющее номер выходного сигнала,

который

устанавливается № X1 X2 X3 Y0 Y1 Y2 Y3 Y4 Y5 Y6 Y7

0 0 0 0 1 0 0 0 0 0 0 0

в 1. Значения

1 0 0 1 0 1 0 0 0 0 0 0

остальных

2 0 1 0 0 0 1 0 0 0 0 0

выходных

3 0 1 1 0 0 0 1 0 0 0 0

сигналов должны 4 1 0 0 0 0 0 0 1 0 0 0

быть

5 1 0 1 0 0 0 0 0 1 0 0

6 1 1 0 0 0 0 0 0 0 1 0

установлены в 0.

7 1

1 1 0 0 0 0 0 0 0 1

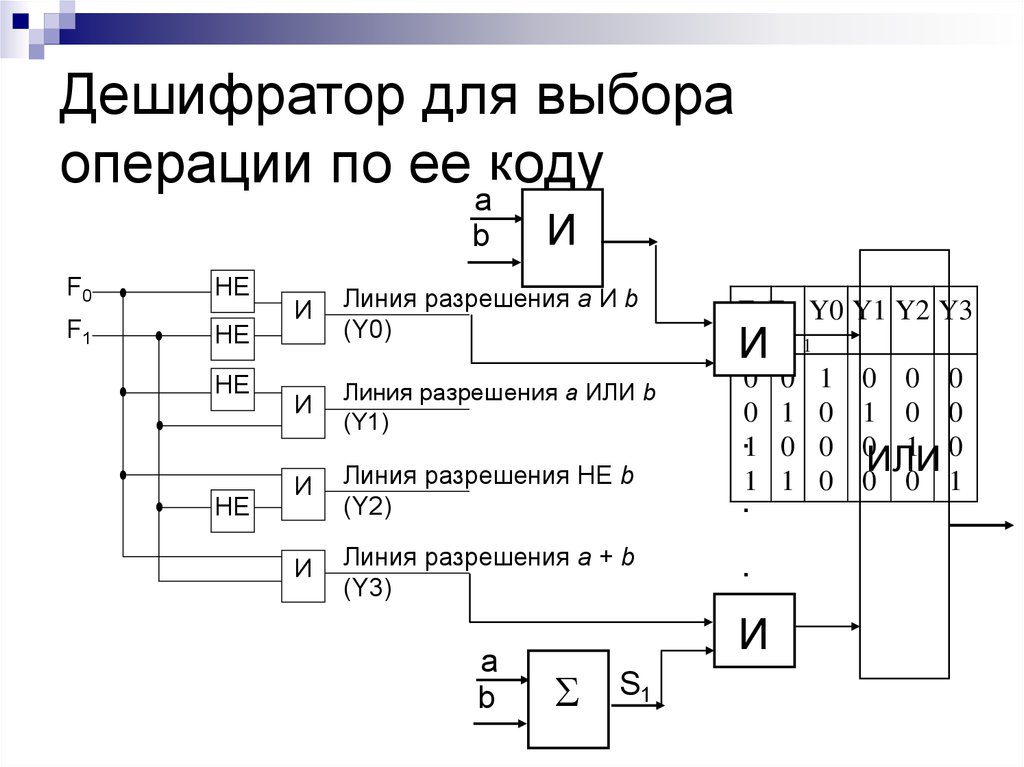

19. Дешифратор для выбора операции по ее коду

Дешифратор для выбораоперации по ее aкоду

b

F0

НЕ

F1

НЕ

НЕ

НЕ

И

И

Линия разрешения a И b

(Y0)

И

Линия разрешения a ИЛИ b

(Y1)

И

Линия разрешения НЕ b

(Y2)

И

Линия разрешения a + b

(Y3)

a

b

F0 F Y0 Y1 Y2 Y3

И

0

0

.1

1

.

.

И

S1

1

0

1

0

1

1

0

0

0

0 0 0

1 0 0

0 1 0

ИЛИ

0 0 1

20. Дешифратор для выбора ячейки памяти по ее адресу

Ад

x0

y0

y1

x1

р

.

.

.

D

.

.

.

е

с xn-1

0

1

yN-1

N-1

регистр

21. Определения

Схема называется комбинационной (схема безпамяти), если значения переменных на выходе

схемы однозначно зависят только от значения

входных переменных.

Схема называется последовательностной (схема

с памятью), если значения выходов схемы зависят

не только от значений на входах, но и от внутреннего

состояния (внутренних переменных).

Ч.С.

Схема называется схемой с обратными связями, если

в качестве внутренних переменных используются

значения выходных переменных, полученных в

предыдущий момент времени.

22. Триггер (SR-защелка)

Вход SВыход 01 0 0 1

Q*

НЕ-ИЛИ

Выход 0

1

Q

0 1 0 1

011 0

Вход R

01 1

1

НЕ-ИЛИ

x1

0

0

1

1

При S=0 R=0

Стабильные состояния Нестабильные состояния

a) Q=0 Q*=1

a) Q=1 Q*=1

б) Q=1 Q*=0

б) Q=0 Q*=0

x2 x1 НЕ-ИЛИ x2

0

1

1

0

0

0

1

0

При S=1 R=0

Q=1

При S=0 R=1

Q=0

При S=1 R=1

Q=Q*=0

Информатика

Информатика