Похожие презентации:

Архитектура процессоров. «Структура компьютерных средств» Тема №7. Занятие №2/2

1.

ВОЕННАЯ КАФЕДРАНАО «КазНИТУ имени К.И. САТПАЕВА»

ЦИКЛ

ИНФОРМАЦИОННОЙ ЗАЩИТЫ

2.

Дисциплина«Структура компьютерных

средств»

Тема №7

«Процессоры»

Занятие №2/2

«Архитектура процессоров»

3.

Учебные вопросы:1. Процессоры с различной архитектурой.

2. Архитектура многоядерных

процессоров.

Цели занятия:

Знать архитектуры процессоров;

Иметь представление об особенностях

архитектур многоядерных процессоров.

4.

Учебный вопрос №1.«Процессоры с различной архитектурой»

Основными

отличительными

характеристиками

каждой

отдельной

архитектуры являются:

• размер и функции регистров процессора

(регистрового файла);

• способ и ограничения при обращении к

памяти для чтения и записи;

• число операций, выполняемых одной

командой;

• длина

команд

(переменная

или

фиксированная);

• число типов данных.

5.

Вопрос №1. «Процессоры с различной архитектурой»Процессоры с архитектурой CISC

Основную идею CISC-архитектуры

отражает ее название - «полный

набор команд». В данной архитектуре

стремятся

иметь

отдельную

машинную команду для каждого

возможного (типового) действия по

обработке данных.

6.

Вопрос №1. «Процессоры с различной архитектурой»Черты организации CISC-процессоров:

• большое количество различных машинных

команд (сотни), каждая из которых выполняется

за несколько тактов центрального процессора;

• устройство управления с программируемой

логикой;

• небольшое количество регистров общего

назначения (РОН);

• различные форматы команд с разной длиной;

• преобладание двухадресной адресации;

• развитый механизм адресации операндов,

включающий различные методы косвенной

адресации.

7.

Вопрос №1. «Процессоры с различной архитектурой»Процессоры с архитектурой RISC

Особое

внимание

к

RISCархитектуре обусловлено тем, что в

большинстве

современных

процессоров, относимых к классу

CISC, сложные команды на стадии

декодирования сводятся к набору

простых

RISC-команд,

а

ядро

процессора реализуется как RISCпроцессор.

8.

Концепцию RISC-процессора можно свести к следующимположениям:

• выполнение почти всех (75% команд) за один цикл;

• стандартная однословная длина всех команд, равная

естественной длине слова и ширине шины данных и

допускающая унифицированную конвейерную обработку всех

команд;

• малое число команд (не более 128);

• малое количество форматов команд (не более 4);

• малое число способов адресации (не более 4);

• доступ к памяти только посредством команд «Чтение» и

«Запись»;

• все команды, за исключением «Чтения» и «Записи»,

используют

внутри

процессорные

межрегистровые

пересылки;

• устройство управления с аппаратной логикой;

• относительно большой (не менее 32) процессорный файл

РОН.

9.

Вопрос №1. «Процессоры с различной архитектурой»Преимущества RISC

Для

технологии

RISC

характерна

сравнительно простая структура УУ. Площадь,

выделяемая на кристалле микросхемы для

реализации УУ, существенно меньше. Как

следствие, появляется возможность разместить

на кристалле большое число регистров ЦП.

Кроме того, остается больше места для других

узлов ЦП и для дополнительных устройств:

кэш-памяти, блока арифметики с плавающей

запятой, части основной памяти, блока

управления памятью, портов ввода/вывода.

10.

Недостатки RISCПринципиальный недостаток - сокращенное

число команд: на выполнение ряда функций

приходится тратить несколько команд вместо одной

в CISC. Это удлиняет код программы, увеличивает

загрузку памяти и трафик команд между пам. и ЦП.

Большое число регистров усложняет схему

декодирования номера регистра, тем самым

увеличивается время доступа к регистрам.

УУ с аппаратной логикой, реализованное в

большинстве RISC-систем, менее гибко, более

склонно к ошибкам, затрудняет поиск и

исправление ошибок, уступает при выполнении

сложных команд.

11.

Вопрос №1. «Процессоры с различной архитектурой»Процессоры с архитектурой VLIW

Архитектура с командными словами

сверхбольшой

длины

или

со

сверхдлинными командами (VLIW, Very

Long Instruction Word) известна с начала

80-х из ряда университетских проектов.

Идея VLIW базируется на том, что задача

эффективного

планирования

параллельного

выполнения

команд

возлагается на «разумный» компилятор.

12.

Вопрос №1. «Процессоры с различной архитектурой»Объединение нескольких простых команд в

одну сверхдлинную производится по следующим

правилам:

• количество простых команд, объединяемых в

одну команду сверхбольшой длины, равно числу

имеющихся в процессоре функциональных

(исполнительных) блоков (ФБ);

• в сверхдлинную команду входят только такие

простые

команды,

которые

исполняются

разными

ФБ,

то

есть

обеспечивается

одновременное исполнение всех составляющих

сверхдлинной команды.

13.

Вопрос №1. «Процессоры с различной архитектурой»Рис. 7.19. Формат сверхдлинной команды и взаимосвязь полей

команды с составляющими блока исполнения

14.

Вопрос №1. «Процессоры с различной архитектурой»Двумя проблемами VLIW-архитектуры

являются:

■ усложнение регистрового файла и,

прежде всего, связей этого файла с

вычислительными устройствами;

■ трудности создания компиляторов,

способных

найти

в

программе

независимые команды, связать такие

команды в длинные строки и обеспечить

их параллельное выполнение.

15.

Вопрос №1. «Процессоры с различной архитектурой»Процессоры с архитектурой EPIC

Дальнейшим развитием идеи VLIW

стала архитектура EPIC (Explicitly Parallel

Instruction Computing) - вычисления с

явным параллелизмом команд.

В

архитектуре,

возникшей

как

совместная разработка фирм Intel и

Hewlett-Packard,

реализован

новый

подход,

являющийся

усовершенствованным вариантом технологии

VLIW.

16.

Вопрос №1. «Процессоры с различной архитектурой»В архитектуре EPIC, которая в

изделиях Intel получила название IA64

(Intel

Architecture

64),

предполагается наличие в процессоре

ста двадцати восьми 64-разрядных

регистров общего назначения (РОН) и

ста двадцати восьми 80-разрядных

регистров с плавающей запятой.

17.

Вопрос №1. «Процессоры с различной архитектурой»Рис. 7.20. Формат сверхдлинной команды

в архитектуре IA-64

18.

Вопрос №1. «Процессоры с различной архитектурой»Особенностями архитектуры EPIC являются:

• большое количество регистров;

• масштабируемость

архитектуры

до

большого

количества функциональных блоков. Это свойство

представители компаний Intel и HP называют

наследственно масштабируемой системой команд

(Inherently Scaleable Instruction Set);

• явный параллелизм в машинном коде. Поиск

зависимостей между командами осуществляет не

процессор, а компилятор;

• предикация - команды из разных ветвей условного

предложения снабжаются полями предикатов (полями

условий) и запускаются параллельно;

• предварительная загрузка - данные из медленной

основной памяти загружаются заранее.

19.

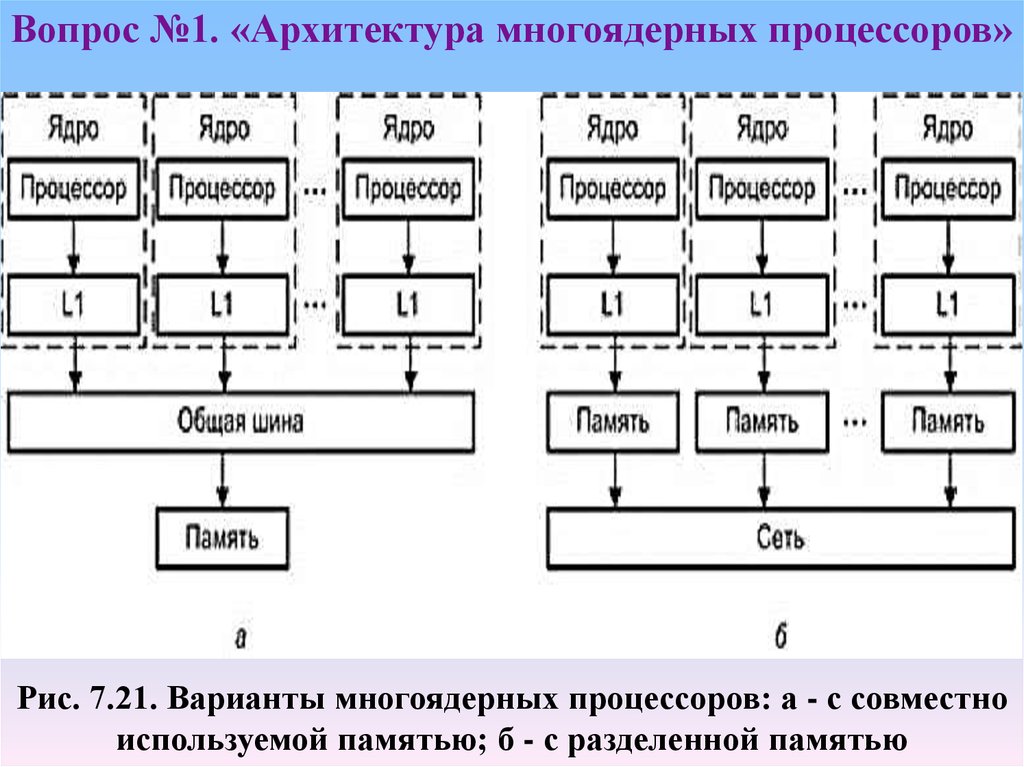

Учебный вопрос №2.«Архитектура многоядерных процессоров»

Многоядерный процессор - это

центральный

процессор,

содержащий

два

и

более

вычислительных ядра на одном

процессорном кристалле или в

одном корпусе. Под ядром принято

понимать процессор и кэш-память

(обычно первого уровня - L1).

20.

Вопрос №1. «Архитектура многоядерных процессоров»Рис. 7.21. Варианты многоядерных процессоров: а - с совместно

используемой памятью; б - с разделенной памятью

21.

Приложения, обрабатывающие большиефайлы данных:

• 2D/3D САПР;

• системы моделирования, средства работы с

анимацией;

• средства обработки цифровых изображений;

• электронные издательские системы;

• средства видеомонтажа/рендеринга;

• компьютерные игры (на клиентских

компьютерах и серверах);

• средства поиска/индексирования;

• системы потокового мультимедиа;

• средства защиты и криптографии.

Электроника

Электроника