Похожие презентации:

Теория дискретных устройств автоматики и телемеханики

1. Теория дискретных устройств автоматики и телемеханики

Материалы к курсу лекцийСоставитель –доктор техн. наук, профессор Сперанский Д.В.

2. Дискретные элементы контактного действия ( реле)

Некоторые историки науки утверждают, что реле впервые былоразработано и построено русским ученым П. Л. Шиллингом в 1830—

1832 гг. Это реле составляло основную часть вызывного устройства в

разработанном им телеграфе.

Другие историки отдают первенство известному американскому физику

Дж. Генри (его именем названа единица индуктивности — генри),

который сконструировал контактное реле в 1835 году при попытках

усовершенствовать изобретённый им в 1831 г. телеграфный аппарат. В

1837 году устройство получило применение в телеграфии. Фактически,

первое реле было изобретено американцем Джозефом Генри в 1831 г. и

базировалось на электромагнитном принципе действия. Следует

отметить, что первое реле Дж. Генри было некоммутационным.

Как самостоятельное устройство реле впервые упомянуто в патенте на

телеграф Самюэля Морзе.

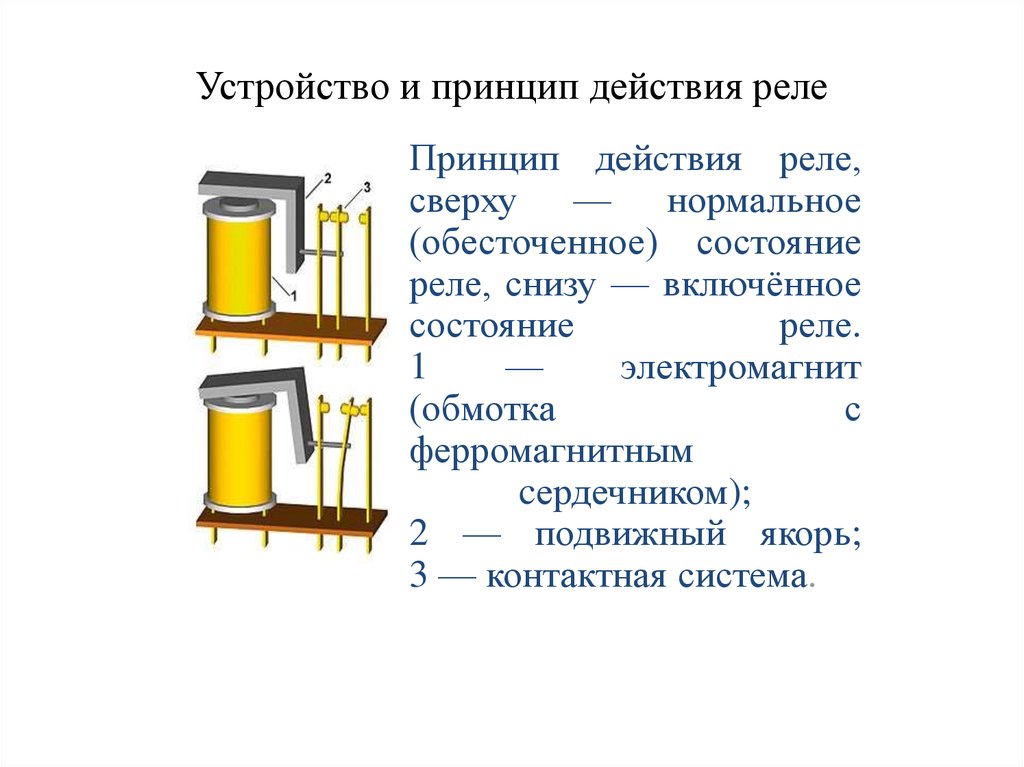

3. Устройство и принцип действия реле

Принцип действия реле,сверху — нормальное

(обесточенное) состояние

реле, снизу — включённое

состояние

реле.

1

—

электромагнит

(обмотка

с

ферромагнитным

cердечником);

2 — подвижный якорь;

3 — контактная система.

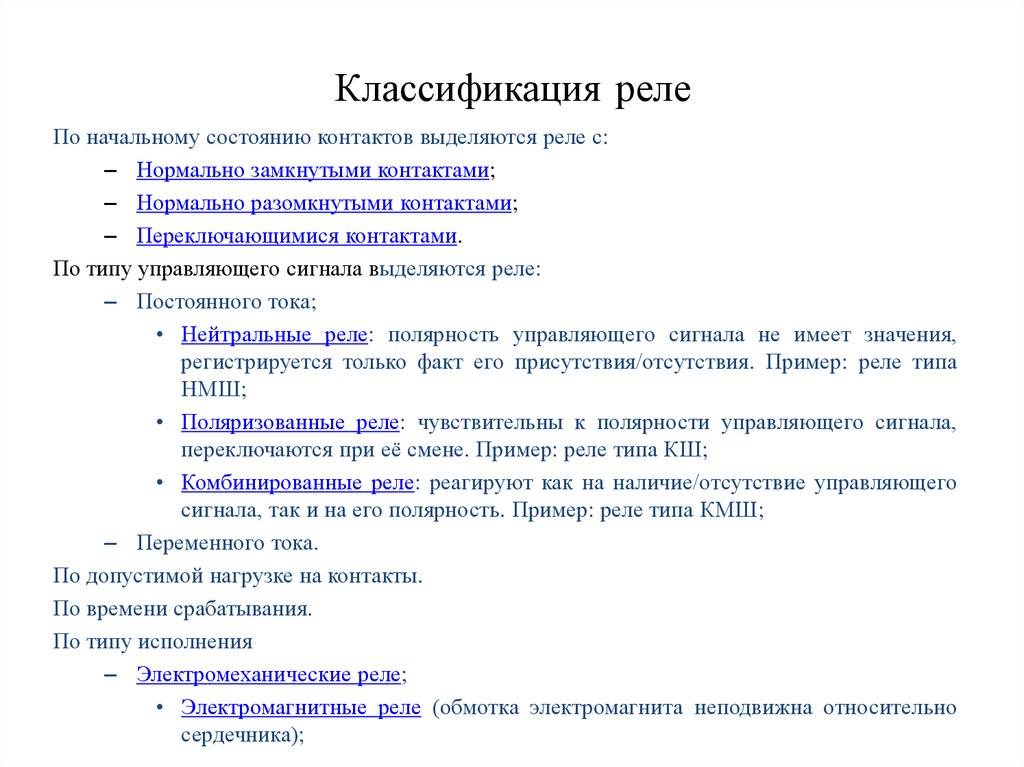

4. Классификация реле

По начальному состоянию контактов выделяются реле с:– Нормально замкнутыми контактами;

– Нормально разомкнутыми контактами;

– Переключающимися контактами.

По типу управляющего сигнала выделяются реле:

– Постоянного тока;

• Нейтральные реле: полярность управляющего сигнала не имеет значения,

регистрируется только факт его присутствия/отсутствия. Пример: реле типа

НМШ;

• Поляризованные реле: чувствительны к полярности управляющего сигнала,

переключаются при её смене. Пример: реле типа КШ;

• Комбинированные реле: реагируют как на наличие/отсутствие управляющего

сигнала, так и на его полярность. Пример: реле типа КМШ;

– Переменного тока.

По допустимой нагрузке на контакты.

По времени срабатывания.

По типу исполнения

– Электромеханические реле;

• Электромагнитные реле (обмотка электромагнита неподвижна относительно

сердечника);

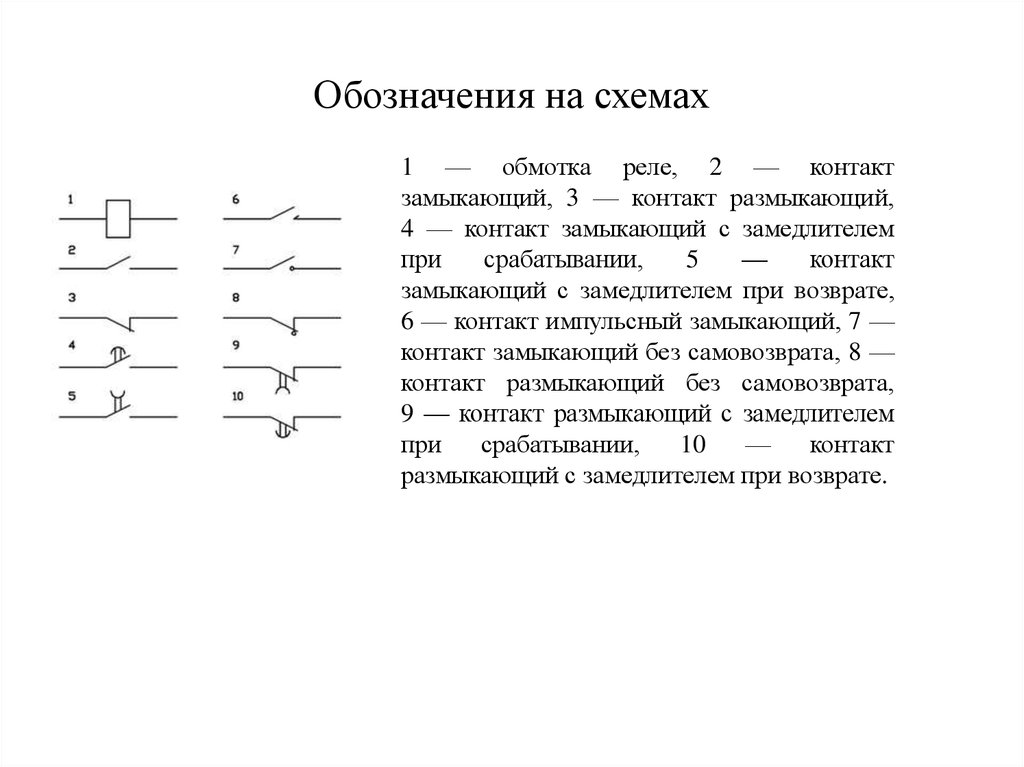

5. Обозначения на схемах

1 — обмотка реле, 2 — контактзамыкающий, 3 — контакт размыкающий,

4 — контакт замыкающий с замедлителем

при

срабатывании,

5

—

контакт

замыкающий с замедлителем при возврате,

6 — контакт импульсный замыкающий, 7 —

контакт замыкающий без самовозврата, 8 —

контакт размыкающий без самовозврата,

9 — контакт размыкающий с замедлителем

при

срабатывании,

10

—

контакт

размыкающий с замедлителем при возврате.

6. Бесконтактные дискретные элементы

Их действие основано на нелинейном изменении проводимости под влияниемнапряжения тока или магнитного поля, воздействующих на элемент. Примеры

таких элементов – диоды, транзисторы.

Полупроводниковый диод представляет из себя элемент, который пропускает

электрический ток только в одном направлении и блокирует его прохождение в

другом

направлении.

Транзи́стор — радиоэлектронный компонент из полупроводникового материала,

обычно с тремя выводами, позволяющий входным сигналом управлять током в

электрической цепи. В общем случае транзистором называют любое устройство,

которое изменяет сигнал между двумя различными состояниями при изменении

сигнала на управляющем электроде.

В полевых и биполярных транзисторах управление током в выходной цепи

осуществляется за счёт изменения входного напряжения или тока. Небольшое

изменение входных величин может приводить к существенно большему

изменению выходного напряжения и тока. В настоящее время в аналоговой

технике доминируют биполярные транзисторы (БТ). В цифровой технике

биполярные транзисторы почти полностью вытеснены полевыми.

7. Классификация дискретных устройств Дискретный автомат (ДА) - модель, отражающая только его свойства по переработке информации.

В ДА выделяются множества входов {x1 , x2 ,..., x p },

выходов {z1 , z ,..., zq } , множества внутренних состояний

2

{s1 , s2 ,..., sn }

.

По виду функций выходов ДА делятся на:

• Комбинационные (автоматы без памяти) – его выход зависит только от

входных сигналов.

• Автоматы с памятью - его выход зависит от входных сигналов и

внутреннего состояния ДА. Внутреннее состояние определяется состояниями

его элементов памяти. Функционирование его происходит в дискретные

моменты времени t1 , t2 ,...

, интервалы между которыми называются

тактами.

• По виду определения тактов, в которые рассматривается функция выходов

автомата, автоматы с памятью делятся на синхронные и асинхронные.

8. Классификация ДУ ( продолжение)

В синхронных автоматах его такты определяются синхронизирующимиимпульсами, вырабатываемыми специальным генератором. Состояния

входа, выхода и памяти этого автомата рассматриваются только в

моменты поступления синхронизирующих сигналов. Смена состояний

элементов памяти происходит только после окончания синхронизирующих

сигналов. Функция переходов состояний синхронного автомата имеет вид

s (t ) ( x(t ), s (t 1))

В зависимости от вида функции выходов в классе синхронных автоматов

выделяют :

y (t ) ( x(t ), s (t 1)),

автомат Мили, у которого функция выходов имеет вид

y (t ) ( s (t )).

автомат Мура, у которого функция выходов имеет вид

9. Классификация ДУ ( продолжение)

• В асинхронном автомате в отличие от синхронного дискретныемоменты времени определяются изменениями входных сигналов или

состоянием элементов памяти автомата, а длительность такта –

интервалом времени, в течение которого состояние автомата не

меняется.

• Переход от такта к такту в асинхронном автомате происходит

вследствие изменения входных сигналов или внутреннего состояния,

т.е. его памяти. В общем случае в течение воздействия одного

входного сигнала автомат может несколько раз изменить свое

внутреннее состояние.

10. Функции алгебры логики (ФАЛ)

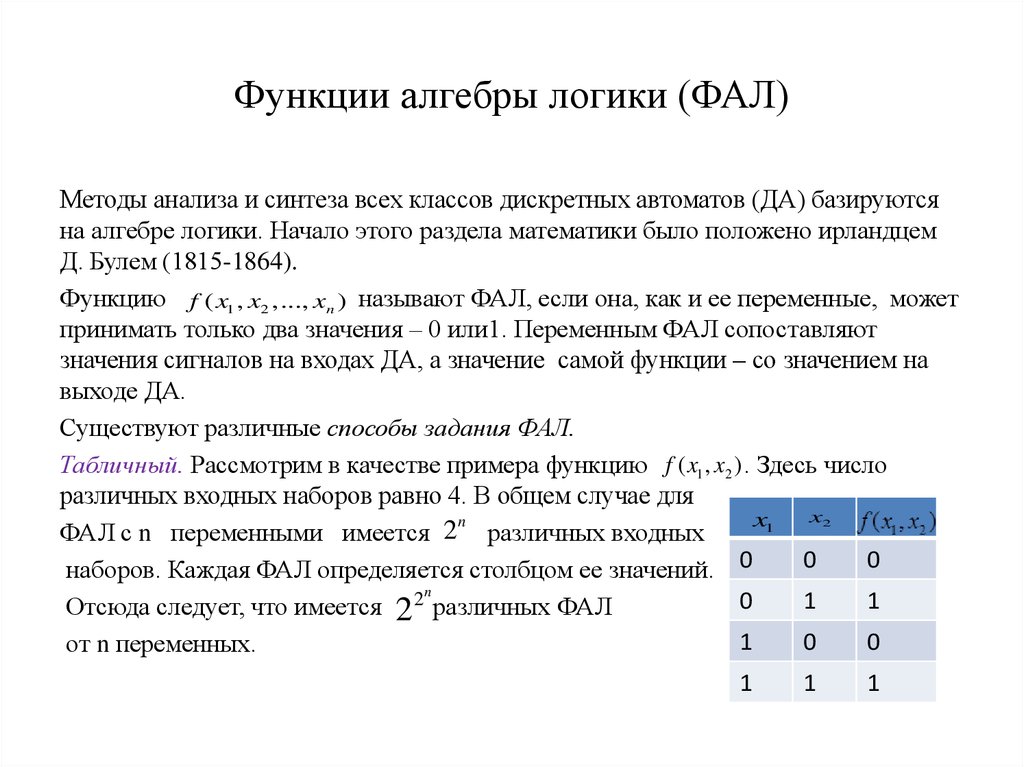

Методы анализа и синтеза всех классов дискретных автоматов (ДА) базируютсяна алгебре логики. Начало этого раздела математики было положено ирландцем

Д. Булем (1815-1864).

Функцию f ( x1 , x2 ,..., xn ) называют ФАЛ, если она, как и ее переменные, может

принимать только два значения – 0 или1. Переменным ФАЛ сопоставляют

значения сигналов на входах ДА, а значение самой функции – со значением на

выходе ДА.

Существуют различные способы задания ФАЛ.

Табличный. Рассмотрим в качестве примера функцию f ( x1 , x2 ) . Здесь число

различных входных наборов равно 4. В общем случае для

x

n

x1

2

ФАЛ с n переменными имеется

различных входных

0

0

наборов. Каждая ФАЛ определяется столбцом ее значений. 0

n

2

0

1

1

Отсюда следует, что имеется 2 различных ФАЛ

1

0

0

от n переменных.

2

1

1

1

11. ФАЛ (2)

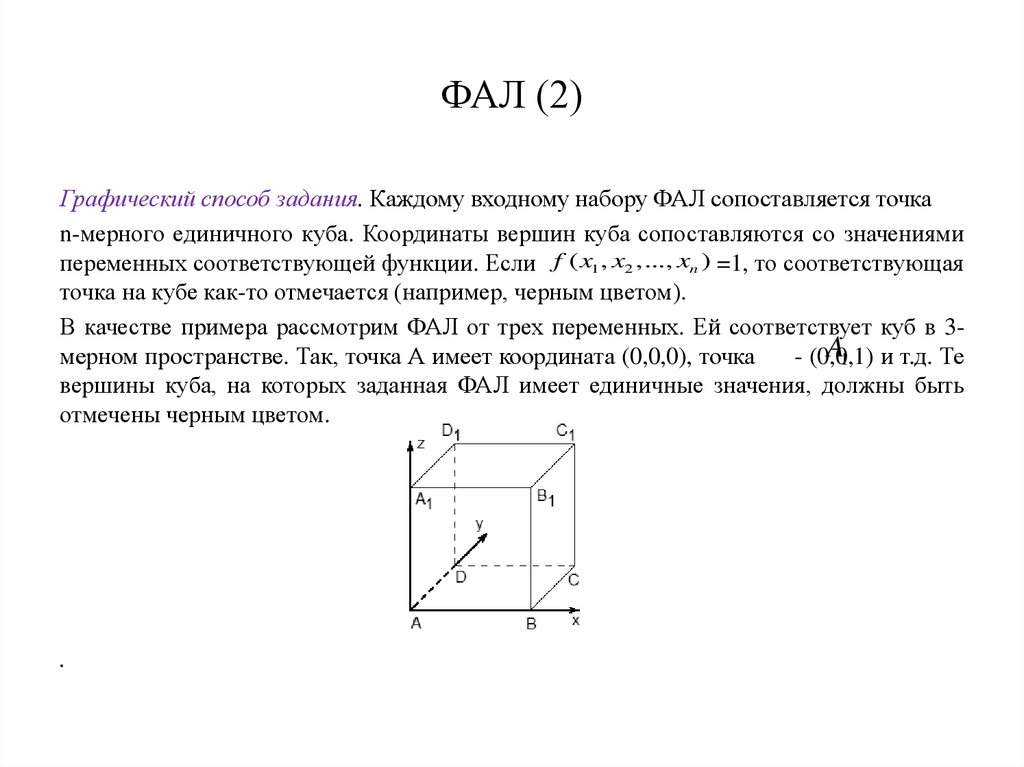

Графический способ задания. Каждому входному набору ФАЛ сопоставляется точкаn-мерного единичного куба. Координаты вершин куба сопоставляются со значениями

переменных соответствующей функции. Если f ( x1 , x2 ,..., xn ) =1, то соответствующая

точка на кубе как-то отмечается (например, черным цветом).

В качестве примера рассмотрим ФАЛ от трех переменных. Ей соответствует куб в 3A1 и т.д. Те

мерном пространстве. Так, точка А имеет координата (0,0,0), точка

- (0,0,1)

вершины куба, на которых заданная ФАЛ имеет единичные значения, должны быть

отмечены черным цветом.

.

12. ФАЛ (3)

Аналитический способ задания. Функция может быть задана в видеалгебраического выражения, показывающего, какое и в какой последовательности

должны выполняться логические операции над переменными функции (эти

операции мы введем позже).

В качестве примера рассмотрим одну и ту же функцию от трех переменных,

которая может быть задана в виде двух различных аналитических выражений:

f ( x1 , x2 , x3 ) x1 x2 x3 x1 x2 x3 x1 x2 x3 x1 x2 x3 ,

( x 1 x2 x3 )( x1 x2 x3 )( x1 x2 x3 )( x1 x2 x3 )

.

Первое выражение указывает на то, что функция принимает значение 1 на

следующих наборах переменных : (0,1,1) , (1,1,1), (0,1,0), (0,0,0). На остальных

четырех наборах функция принимает значение 0.

Второе выражение указывает на то, что функция принимает значение 0 на

следующих наборах переменных : (0,0,1) , (1,0,0), (1,0,1), (1,1,0). На остальных

четырех наборах функция принимает значение 1.

13. ФАЛ (4)

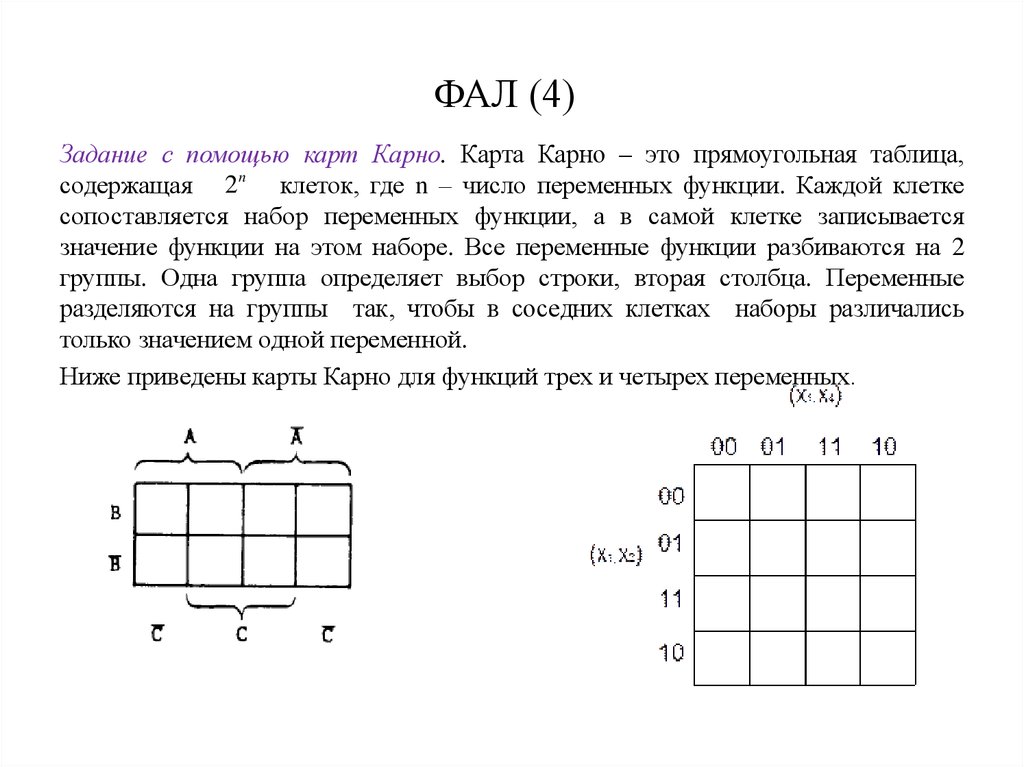

Задание с помощью карт Карно. Карта Карно – это прямоугольная таблица,содержащая 2n клеток, где n – число переменных функции. Каждой клетке

сопоставляется набор переменных функции, а в самой клетке записывается

значение функции на этом наборе. Все переменные функции разбиваются на 2

группы. Одна группа определяет выбор строки, вторая столбца. Переменные

разделяются на группы так, чтобы в соседних клетках наборы различались

только значением одной переменной.

Ниже приведены карты Карно для функций трех и четырех переменных.

14. Различные функции алгебры логики

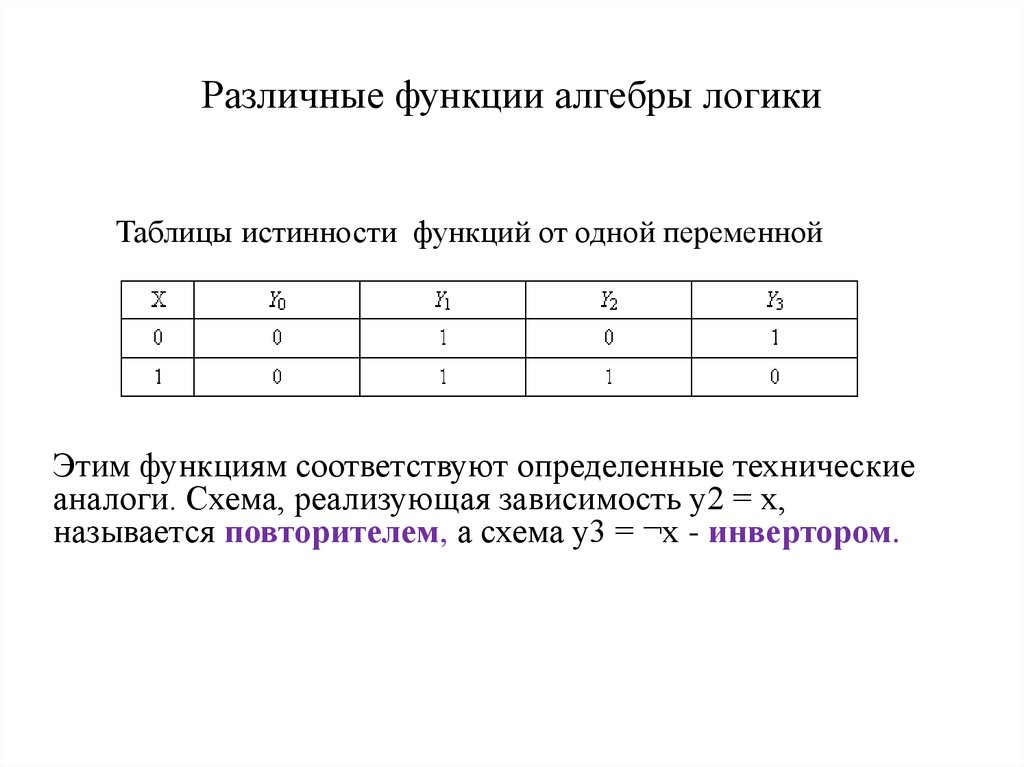

Таблицы истинности функций от одной переменнойЭтим функциям соответствуют определенные технические

аналоги. Схема, реализующая зависимость у2 = х,

называется повторителем, а схема у3 = ¬х - инвертором.

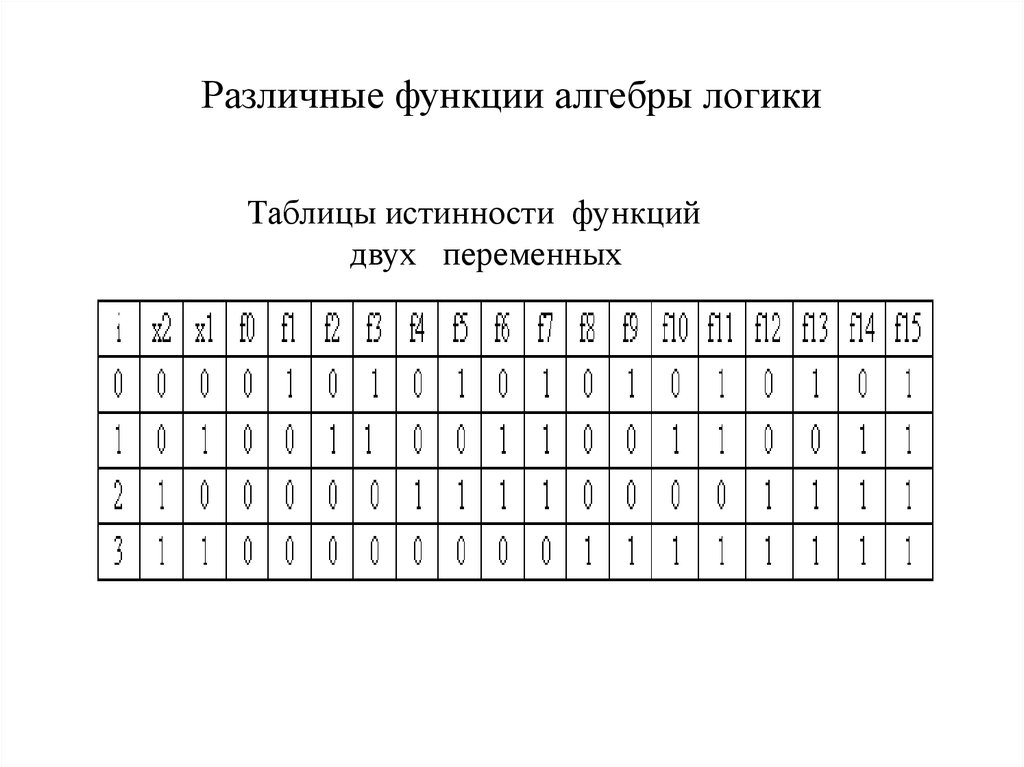

15. Различные функции алгебры логики

Таблицы истинности функцийдвух переменных

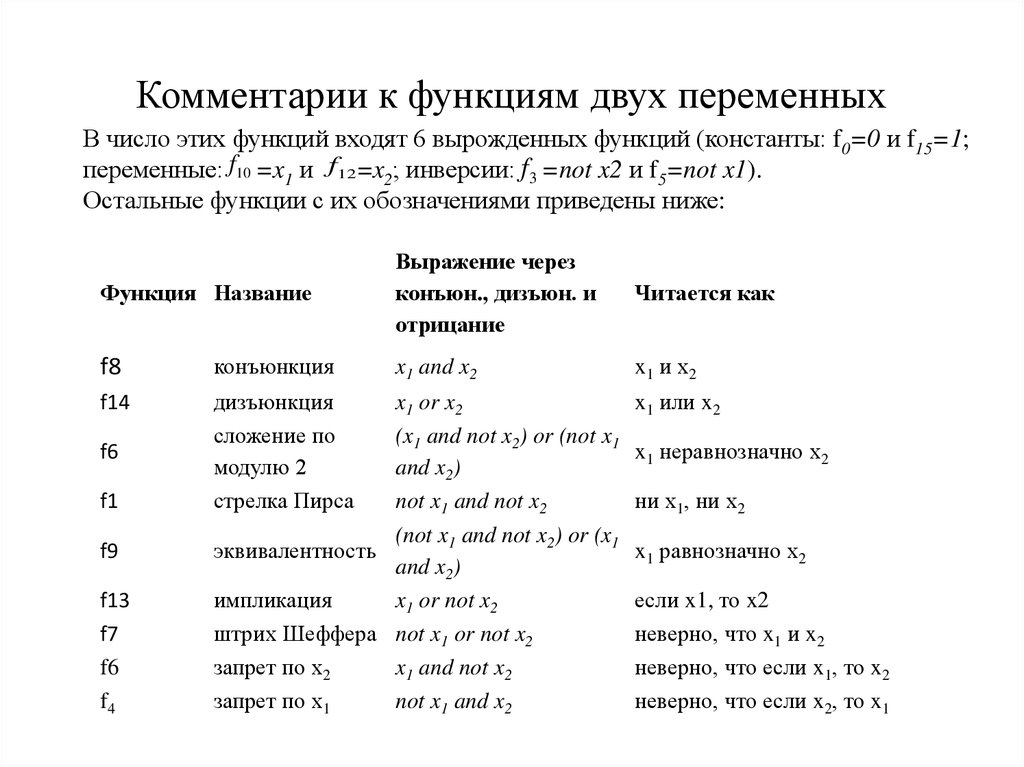

16. Комментарии к функциям двух переменных

В число этих функций входят 6 вырожденных функций (константы: f0=0 и f15=1;переменные: f10 =x1 и f12 =x2; инверсии: f 3 =not x2 и f5=not x1).

Остальные функции с их обозначениями приведены ниже:

Функция Название

f8

конъюнкция

f14

дизъюнкция

сложение по

модулю 2

стрелка Пирса

f6

f1

f9

f13

f7

f6

f4

Выражение через

конъюн., дизъюн. и

отрицание

Читается как

x1 and x2

x1 и x 2

x1 or x2

(x1 and not x2) or (not x1

and x2)

not x1 and not x2

(not x1 and not x2) or (x1

эквивалентность

and x2)

импликация

x1 or not x2

штрих Шеффера not x1 or not x2

запрет по x2

x1 and not x2

запрет по x1

not x1 and x2

x1 или x2

x1 неравнозначно x2

ни x1, ни x2

x1 равнозначно x2

если x1, то x2

неверно, что x1 и x2

неверно, что если x1, то x2

неверно, что если x2, то x1

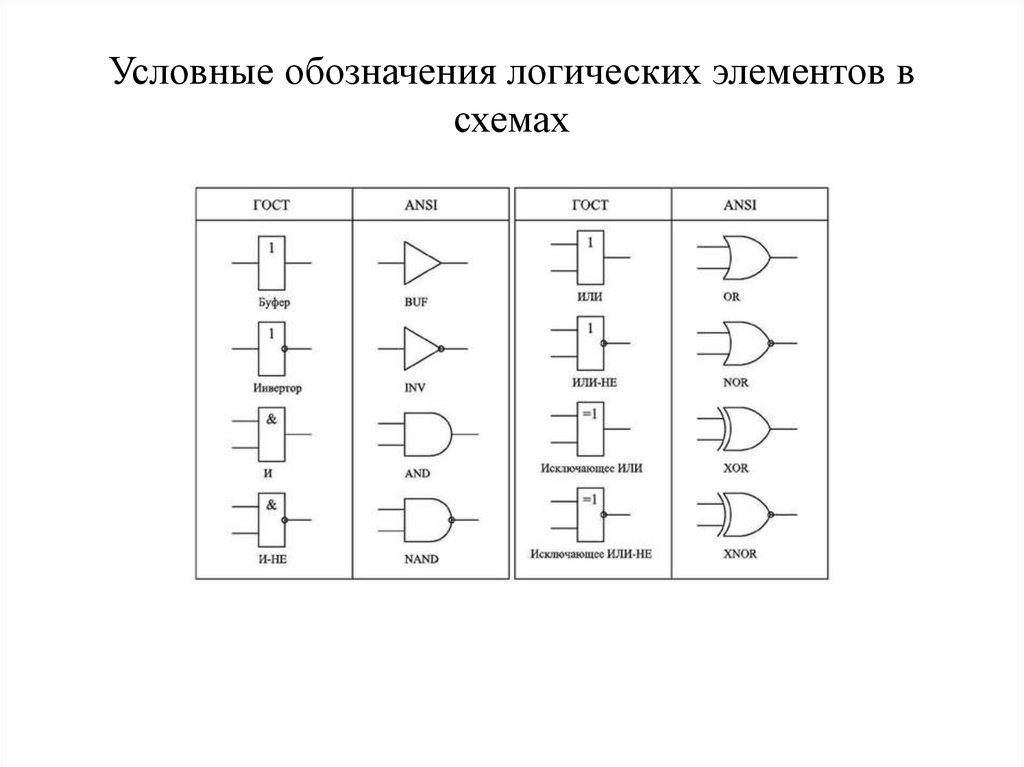

17. Условные обозначения логических элементов в схемах

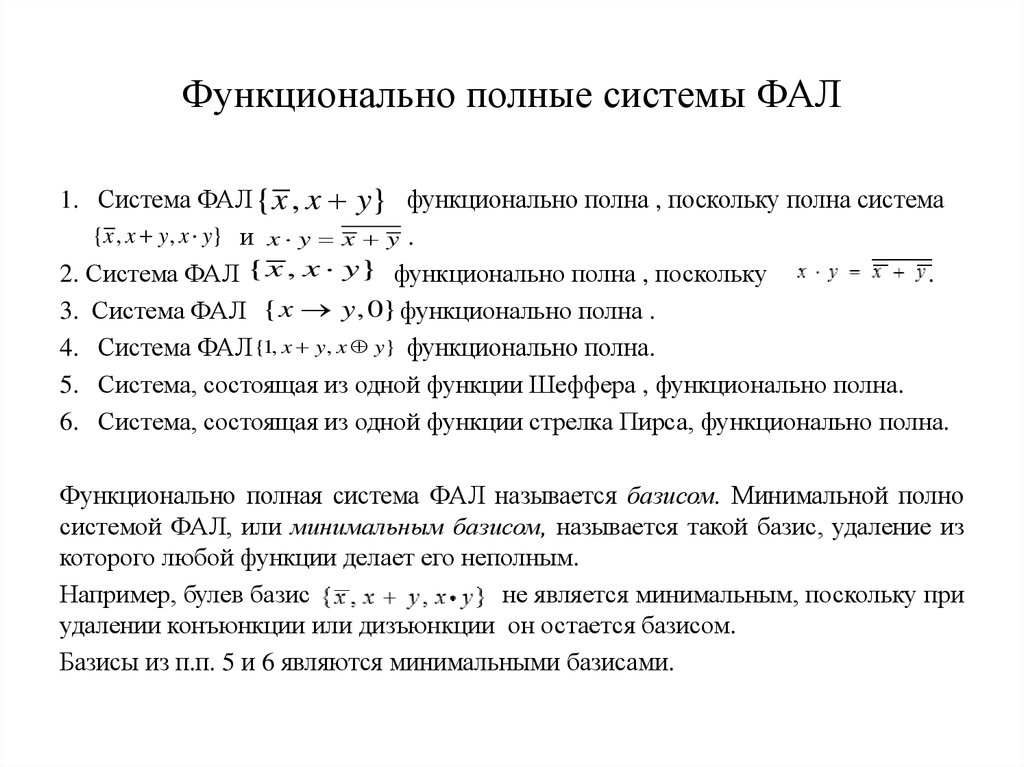

18. Функционально полные системы ФАЛ

Рассмотрим задачу определения множества таких ФАЛ, используя которые можнополучить любую сложную ФАЛ.

Систему функций ФАЛ { f1 , f 2 ,..., f n }

называют функционально полной, если

любая ФАЛ может быть выражена суперпозицией функций f1 , f 2 ,..., f n

и

логических переменных.

Суперпозицией называют подстановку в функцию вместо ее аргументов других

функций.

Справедливо следующее утверждение: если все функции функционально полной

системы представимы через функции другой системы, то последняя система

также функционально полна. Доказано также, что система функций {x , x y , x y}

функционально полна.

На основании двух приведенных утверждений можно установить

функциональную полноту ряда других систем ФАЛ.

19. Функционально полные системы ФАЛ

1. Система ФАЛ {x , x y} функционально полна , поскольку полна система{x , x y, x y} и x y x y .

2. Система ФАЛ { x , x y} функционально полна , поскольку

.

3. Система ФАЛ {x y , 0} функционально полна .

4. Система ФАЛ {1, x y, x y} функционально полна.

5. Система, состоящая из одной функции Шеффера , функционально полна.

6. Система, состоящая из одной функции стрелка Пирса, функционально полна.

Функционально полная система ФАЛ называется базисом. Минимальной полно

системой ФАЛ, или минимальным базисом, называется такой базис, удаление из

которого любой функции делает его неполным.

Например, булев базис

не является минимальным, поскольку при

удалении конъюнкции или дизъюнкции он остается базисом.

Базисы из п.п. 5 и 6 являются минимальными базисами.

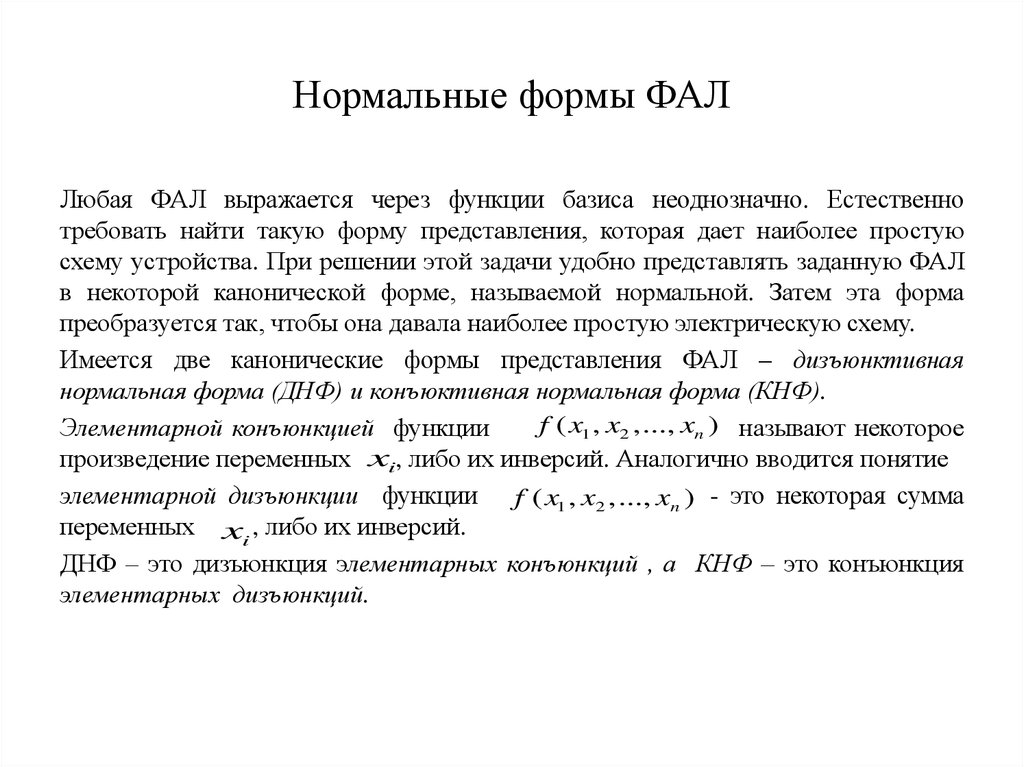

20. Нормальные формы ФАЛ

Любая ФАЛ выражается через функции базиса неоднозначно. Естественнотребовать найти такую форму представления, которая дает наиболее простую

схему устройства. При решении этой задачи удобно представлять заданную ФАЛ

в некоторой канонической форме, называемой нормальной. Затем эта форма

преобразуется так, чтобы она давала наиболее простую электрическую схему.

Имеется две канонические формы представления ФАЛ – дизъюнктивная

нормальная форма (ДНФ) и конъюктивная нормальная форма (КНФ).

f ( x1 , x2 ,..., xn ) называют некоторое

Элементарной конъюнкцией функции

произведение переменных xi, либо их инверсий. Аналогично вводится понятие

элементарной дизъюнкции функции f ( x1 , x2 ,..., xn ) - это некоторая сумма

переменных xi , либо их инверсий.

ДНФ – это дизъюнкция элементарных конъюнкций , а КНФ – это конъюнкция

элементарных дизъюнкций.

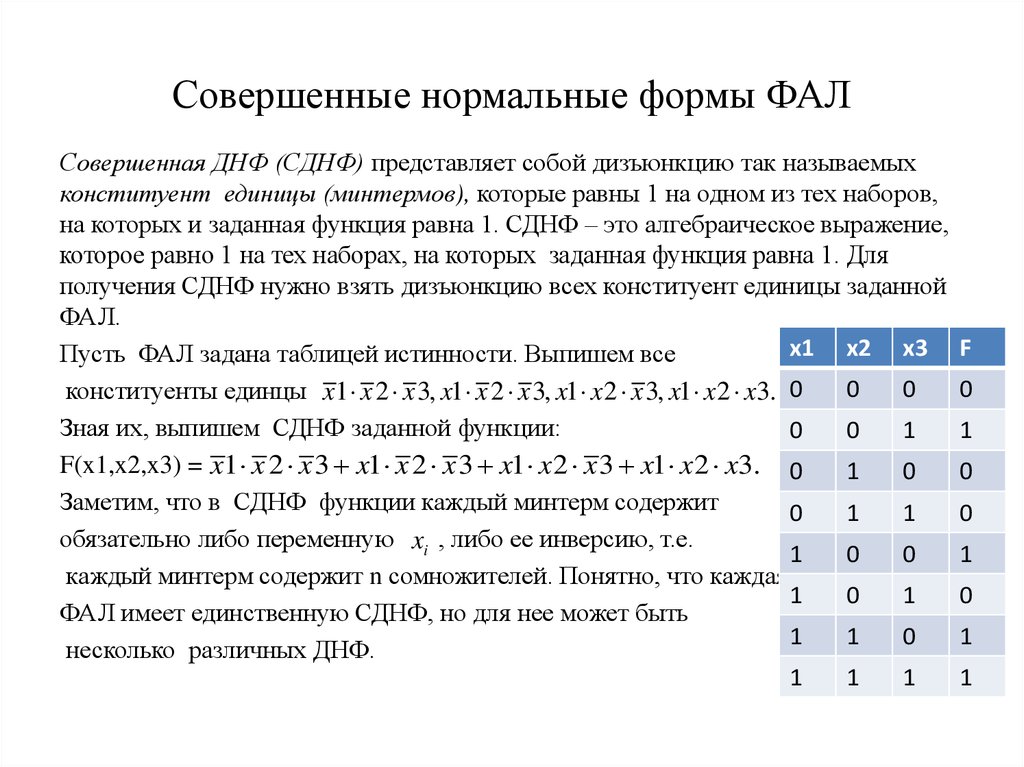

21. Совершенные нормальные формы ФАЛ

Совершенная ДНФ (СДНФ) представляет собой дизъюнкцию так называемыхконституент единицы (минтермов), которые равны 1 на одном из тех наборов,

на которых и заданная функция равна 1. СДНФ – это алгебраическое выражение,

которое равно 1 на тех наборах, на которых заданная функция равна 1. Для

получения СДНФ нужно взять дизъюнкцию всех конституент единицы заданной

ФАЛ.

х1 х2 х3

Пусть ФАЛ задана таблицей истинности. Выпишем все

0

0

конституенты единцы x1 x 2 x 3, x1 x 2 x 3, x1 x 2 x 3, x1 x 2 x3. 0

Зная их, выпишем СДНФ заданной функции:

0

0

1

F(x1,x2,x3) = x1 x 2 x 3 x1 x 2 x 3 x1 x 2 x 3 x1 x 2 x3. 0

1

0

Заметим, что в СДНФ функции каждый минтерм содержит

0

1

1

обязательно либо переменную xi , либо ее инверсию, т.е.

1

0

0

каждый минтерм содержит n сомножителей. Понятно, что каждая

1

0

1

ФАЛ имеет единственную СДНФ, но для нее может быть

1

1

0

несколько различных ДНФ.

1

1

1

F

0

1

0

0

1

0

1

1

22. Совершенные нормальные формы ФАЛ

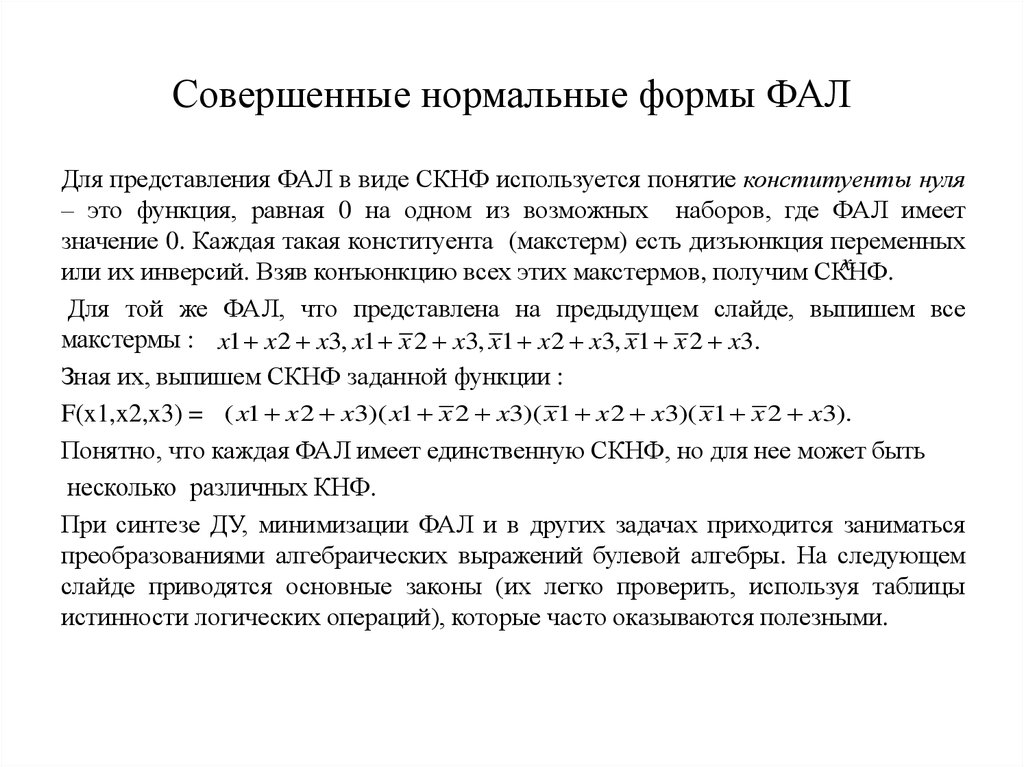

Для представления ФАЛ в виде СКНФ используется понятие конституенты нуля– это функция, равная 0 на одном из возможных наборов, где ФАЛ имеет

значение 0. Каждая такая конституента (макстерм) есть дизъюнкция переменных

xi

или их инверсий. Взяв конъюнкцию всех этих макстермов, получим СКНФ.

Для той же ФАЛ, что представлена на предыдущем слайде, выпишем все

макстермы : x1 x 2 x3, x1 x 2 x3, x1 x 2 x3, x1 x 2 x3.

Зная их, выпишем СКНФ заданной функции :

F(x1,x2,x3) = ( x1 x 2 x3)( x1 x 2 x3)( x1 x 2 x3)( x1 x 2 x3).

Понятно, что каждая ФАЛ имеет единственную СКНФ, но для нее может быть

несколько различных КНФ.

При синтезе ДУ, минимизации ФАЛ и в других задачах приходится заниматься

преобразованиями алгебраических выражений булевой алгебры. На следующем

слайде приводятся основные законы (их легко проверить, используя таблицы

истинности логических операций), которые часто оказываются полезными.

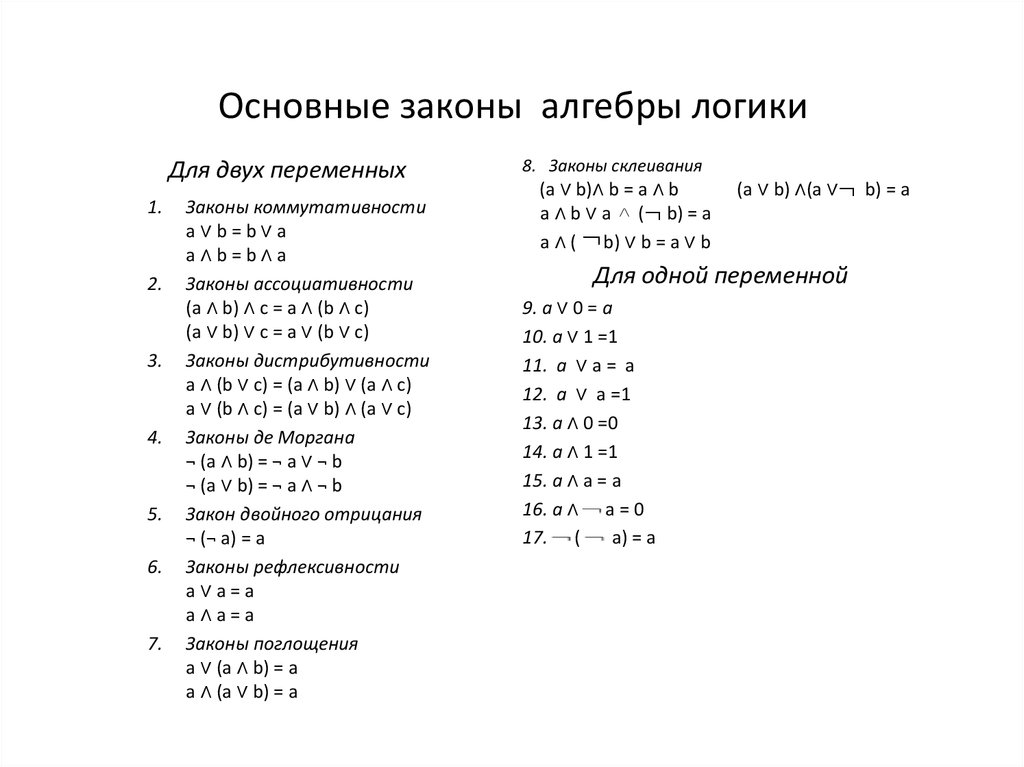

23. Основные законы алгебры логики

Для двух переменных1.

2.

3.

4.

5.

6.

7.

Законы коммутативности

a∨b=b∨a

a∧b=b∧a

Законы ассоциативности

(a ∧ b) ∧ c = a ∧ (b ∧ c)

(a ∨ b) ∨ c = a ∨ (b ∨ c)

Законы дистрибутивности

a ∧ (b ∨ c) = (a ∧ b) ∨ (a ∧ c)

a ∨ (b ∧ c) = (a ∨ b) ∧ (a ∨ c)

Законы де Моргана

¬ (a ∧ b) = ¬ a ∨ ¬ b

¬ (a ∨ b) = ¬ a ∧ ¬ b

Закон двойного отрицания

¬ (¬ a) = a

Законы рефлексивности

a∨a=a

a∧a=a

Законы поглощения

a ∨ (a ∧ b) = a

a ∧ (a ∨ b) = a

8. Законы склеивания

(a ∨ b)∧ b = a ∧ b

a ∧ b ∨ a ( b) = a

a ∧ ( b) ∨ b = a ∨ b

(a ∨ b) ∧(a ∨ b) = a

Для одной переменной

9. a ∨ 0 = a

10. a ∨ 1 =1

11. a ∨ a = a

12. a ∨ a =1

13. a ∧ 0 =0

14. a ∧ 1 =1

15. a ∧ a = a

16. a ∧ a = 0

17. (

a) = a

24. Методы минимизации ФАЛ

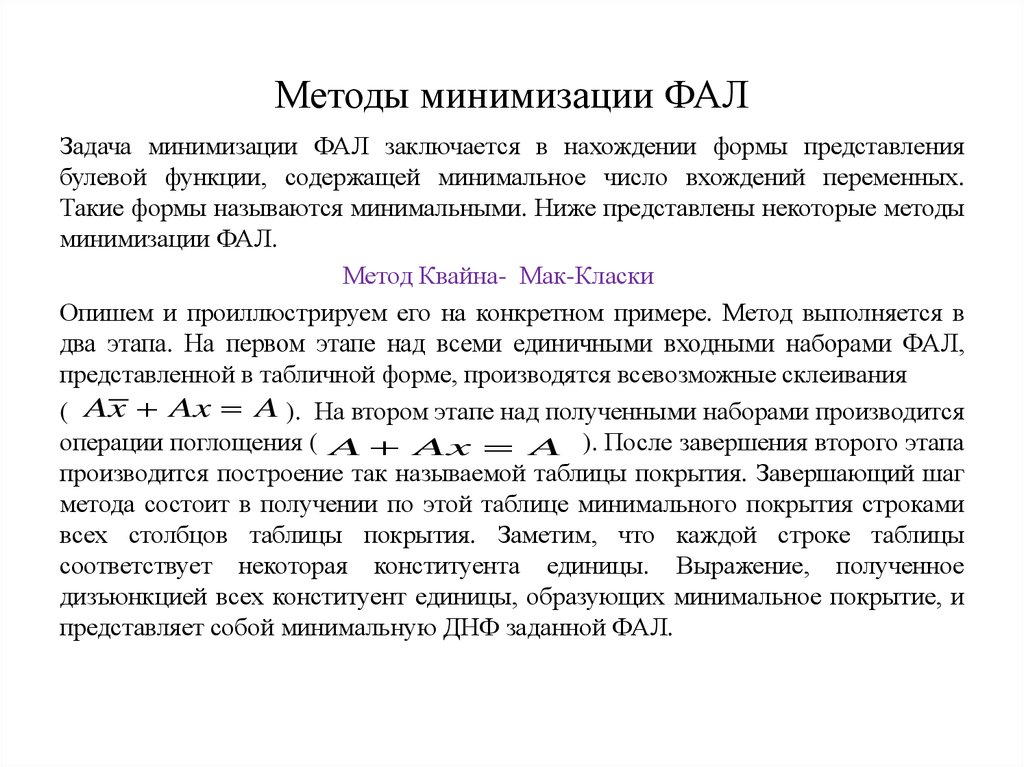

Задача минимизации ФАЛ заключается в нахождении формы представлениябулевой функции, содержащей минимальное число вхождений переменных.

Такие формы называются минимальными. Ниже представлены некоторые методы

минимизации ФАЛ.

Метод Квайна- Мак-Класки

Опишем и проиллюстрируем его на конкретном примере. Метод выполняется в

два этапа. На первом этапе над всеми единичными входными наборами ФАЛ,

представленной в табличной форме, производятся всевозможные склеивания

( Ax Ax A ). На втором этапе над полученными наборами производится

операции поглощения ( A Ax A ). После завершения второго этапа

производится построение так называемой таблицы покрытия. Завершающий шаг

метода состоит в получении по этой таблице минимального покрытия строками

всех столбцов таблицы покрытия. Заметим, что каждой строке таблицы

соответствует некоторая конституента единицы. Выражение, полученное

дизъюнкцией всех конституент единицы, образующих минимальное покрытие, и

представляет собой минимальную ДНФ заданной ФАЛ.

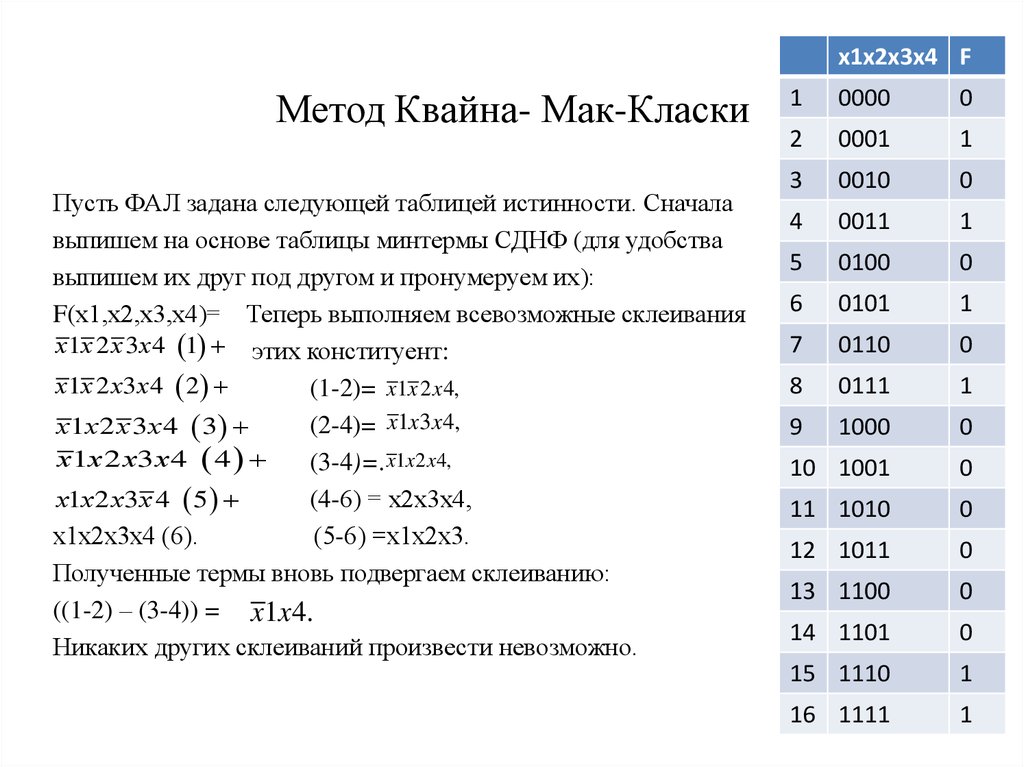

25. Метод Квайна- Мак-Класки

х1х2х3х4 FМетод Квайна- Мак-Класки

Пусть ФАЛ задана следующей таблицей истинности. Сначала

выпишем на основе таблицы минтермы СДНФ (для удобства

выпишем их друг под другом и пронумеруем их):

F(х1,х2,х3,х4)= Теперь выполняем всевозможные склеивания

х1х 2 х 3 х 4 1 этих конституент:

х1х 2 х3 х 4 2

(1-2)= x1x 2 x 4,

(2-4)= x1x3x 4,

х1х 2 х 3 х 4 3

х1х 2 х3 х 4 4

(3-4)=. x1x 2 x 4,

х1х 2 х3 х 4 5

(4-6) = х2х3х4,

х1х2х3х4 (6).

(5-6) =х1х2х3.

Полученные термы вновь подвергаем склеиванию:

((1-2) – (3-4)) = x1x 4.

Никаких других склеиваний произвести невозможно.

1

0000

0

2

0001

1

3

0010

0

4

0011

1

5

0100

0

6

0101

1

7

0110

0

8

0111

1

9

1000

0

10 1001

0

11 1010

0

12 1011

0

13 1100

0

14 1101

0

15 1110

1

16 1111

1

26. Метод Квайна- Мак-Класки

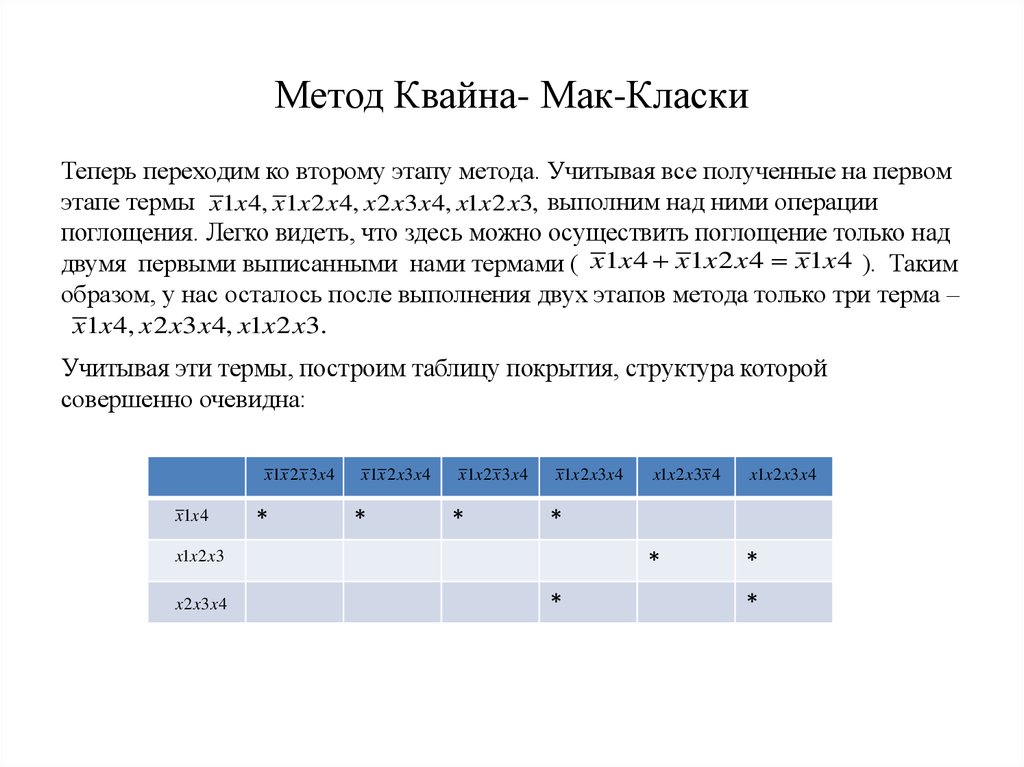

Теперь переходим ко второму этапу метода. Учитывая все полученные на первомэтапе термы x1x 4, x1x 2 x 4, x 2 x3 x 4, x1x 2 x3, выполним над ними операции

поглощения. Легко видеть, что здесь можно осуществить поглощение только над

двумя первыми выписанными нами термами ( x1x 4 x1x 2 x 4 x1x 4 ). Таким

образом, у нас осталось после выполнения двух этапов метода только три терма –

x1x 4, x 2 x3 x 4, x1x 2 x3.

Учитывая эти термы, построим таблицу покрытия, структура которой

совершенно очевидна:

x1x 2 x 3x 4

x1x 4

*

x1x 2 x3 x 4

*

x1x 2 x 3 x 4

*

x1x 2 x3x 4

x1x 2 x3 x 4

*

x1x 2 x3

x 2 x3 x 4

x1x 2 x3x 4

*

*

*

*

27. Метод Квайна – Мак-Класки

В заголовках столбцов, стоящих в первой строке таблицы, выписываются всеминтермы СДНФ заданной ФАЛ. В позиции первого столбца таблицы

вставляются термы, полученные после выполнения двух первых этапов метода.

Содержимое клеток таблицы заполняются так: на пересечении строки А и

столбца В ставится звездочка, если терм (он стоит в первом слева столбце),

соответствующий строке А, входит в состав терма (он стоит в заголовке столбца с

именем В), соответствующего столбцу В. Все остальные клетки таблицы

покрытия остаются пустыми.

Так, в нашем примере звездочки во второй строке (она соответствует терму

)

поставлены в столбцах 2 – 5, т.к. названный терм входит в состав

соответствующих минтермов СДНФ заданной ФАЛ. Остальные позиции таблицы

покрытия заполняются аналогично.

Завершающий шаг метода – нахождения минимального числа строк таблицы,

термы которых «покрывают» все минтермы СДНФ заданной ФАЛ. В нашем

примере , как легко убедиться, два первых сверху терма (две первых строки)

покрывают все минтермы СДНФ ( все столбцы таблицы). Отсюда получаем

искомую минимальную форму ФАЛ : F(x1,x2,x3,x4)=

+

.

28. Минимизация ФАЛ путем алгебраических преобразований

Этот метод предполагает использование основных законов алгебры логики.Продемонстрируем его на следующем примере:

F(x1,x2,x3) = ( x1 x 2 x3) x1 x3 x1x 2 x1 x 2

(используем закон де Моргана)

x1x 2 x 3 x1 x3 x1x 2 x1 x 2

=

( выполним группировку слагаемых)

= ( x1x 2 x 3 x1x 2) ( x1 x1) x 2 x3

( выполняем поглощение)

= ( x1x 2 x1) x3 x 2

( выполняем группировку и поглощение)=

= x1 x 2 x3.

В результате преобразований получена минимальная ДНФ исходной ФАЛ.

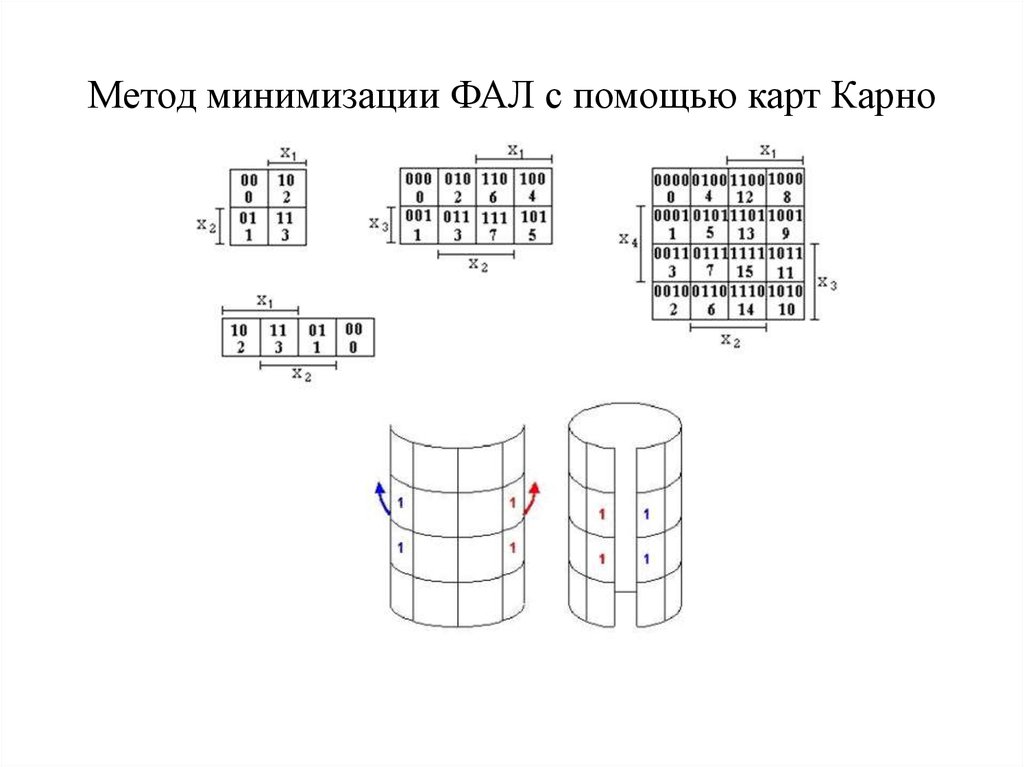

29. Метод минимизации ФАЛ с помощью карт Карно

Карта Карно булевой функции есть перестроенная соответствующим образомтаблица истинности этой функции. Графически она представляет собой плоскую

таблицу. На следующем слайде представлены карты Карно для функций 2-х, 3-х и

4-х переменных. Заметим, что карта Карно для одной и той же функции может

иметь разную структуру. Так, на следующем слайде для функции двух переменных

представлены две разные по структуре карты Карно. Эти карты строятся так,

чтобы две любые соседние его клетки отличались только одной координатой. Карту

Карно можно «свернуть» в цилиндр (это изображено на слайде), соединив самый

левый и самый правый столбцы таблицы, либо соединив самую верхнюю и самую

нижнюю строки таблицы, что обобщает понятие соседства клеток таблицы. В

качестве примера рассмотрим клетку таблицы для функции 4-х переменных, в

которой стоит число 1011 (11). Это число условно означает, что данная клетка

соответствует минтерму x1x 2 x3 x 4 . Соседними для нее сверху и снизу являются

клетки 1001 и 1010, а также слева по строке 1111 и 0011 справа по строке после

свертки в цилиндр. В эту клетку карты Карно необходимо записать значение ( 0

или 1), которое принимает ФАЛ на упомянутом минтерме. Все остальные клетки

карты Карно заполняются значениями 0 или 1 аналогичным образом.

30. Метод минимизации ФАЛ с помощью карт Карно

31. Метод минимизации ФАЛ с помощью карт Карно

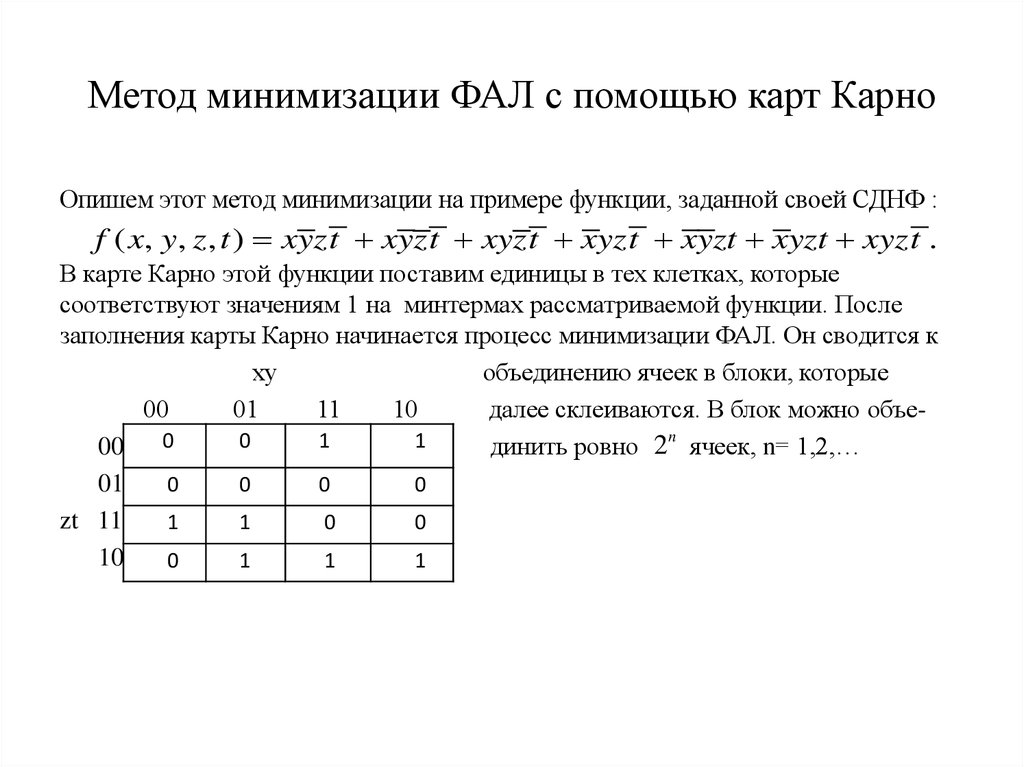

Опишем этот метод минимизации на примере функции, заданной своей СДНФ :f ( x, y , z , t ) xyzt xyzt xyzt xyzt xyzt xyzt xyzt .

В карте Карно этой функции поставим единицы в тех клетках, которые

соответствуют значениям 1 на минтермах рассматриваемой функции. После

заполнения карты Карно начинается процесс минимизации ФАЛ. Он сводится к

ху

объединению ячеек в блоки, которые

00

01

11

10

далее склеиваются. В блок можно объеn

0

1

1

00 0

динить ровно 2 ячеек, n= 1,2,…

0

0

0

0

01

zt 11

1

1

0

0

10

0

1

1

1

32. Метод минимизации ФАЛ с помощью карт Карно

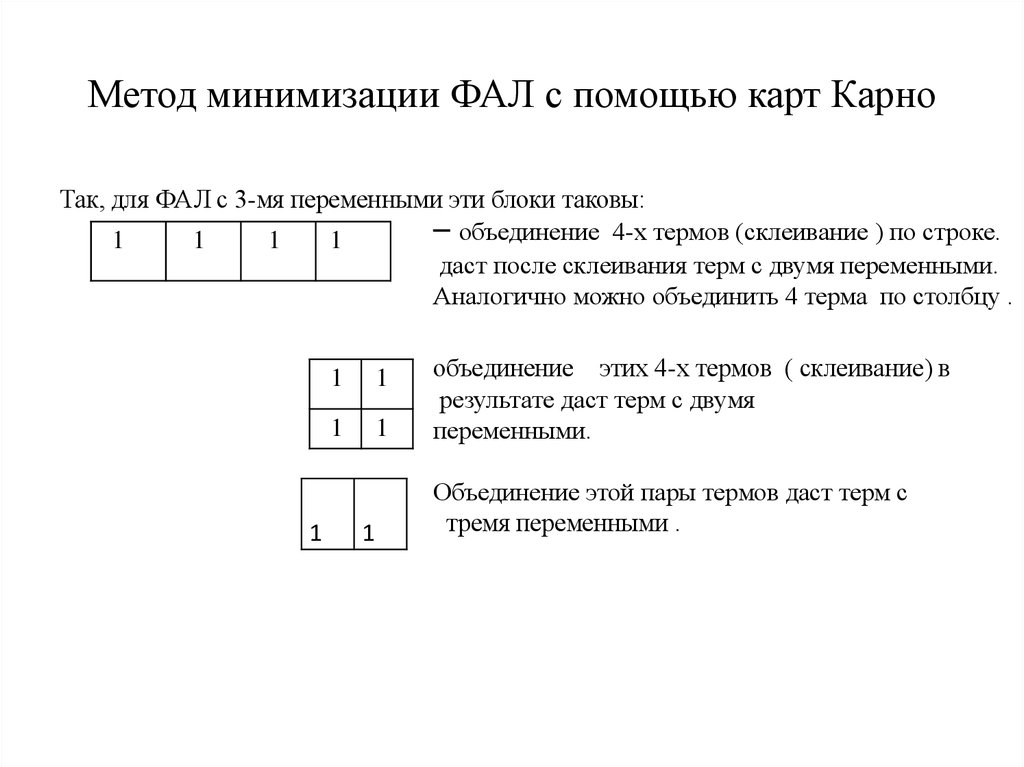

Так, для ФАЛ с 3-мя переменными эти блоки таковы:– объединение 4-х термов (склеивание ) по строке.

1

1

1

1

даст после склеивания терм с двумя переменными.

Аналогично можно объединить 4 терма по столбцу .

1

1

1

1

1

1

объединение этих 4-х термов ( склеивание) в

результате даст терм с двумя

переменными.

Объединение этой пары термов даст терм с

тремя переменными .

33. Метод минимизации ФАЛ с помощью карт Карно

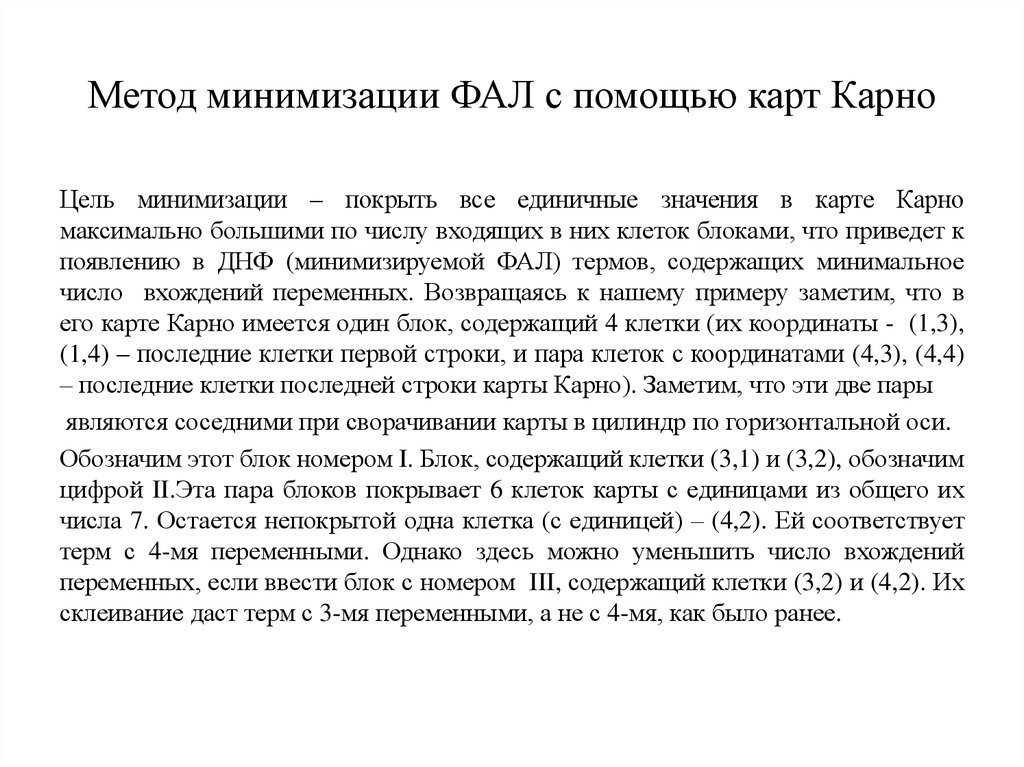

Цель минимизации – покрыть все единичные значения в карте Карномаксимально большими по числу входящих в них клеток блоками, что приведет к

появлению в ДНФ (минимизируемой ФАЛ) термов, содержащих минимальное

число вхождений переменных. Возвращаясь к нашему примеру заметим, что в

его карте Карно имеется один блок, содержащий 4 клетки (их координаты - (1,3),

(1,4) – последние клетки первой строки, и пара клеток с координатами (4,3), (4,4)

– последние клетки последней строки карты Карно). Заметим, что эти две пары

являются соседними при сворачивании карты в цилиндр по горизонтальной оси.

Обозначим этот блок номером I. Блок, содержащий клетки (3,1) и (3,2), обозначим

цифрой II.Эта пара блоков покрывает 6 клеток карты с единицами из общего их

числа 7. Остается непокрытой одна клетка (с единицей) – (4,2). Ей соответствует

терм с 4-мя переменными. Однако здесь можно уменьшить число вхождений

переменных, если ввести блок с номером III, содержащий клетки (3,2) и (4,2). Их

склеивание даст терм с 3-мя переменными, а не с 4-мя, как было ранее.

34. Метод минимизации ФАЛ с помощью карт Карно

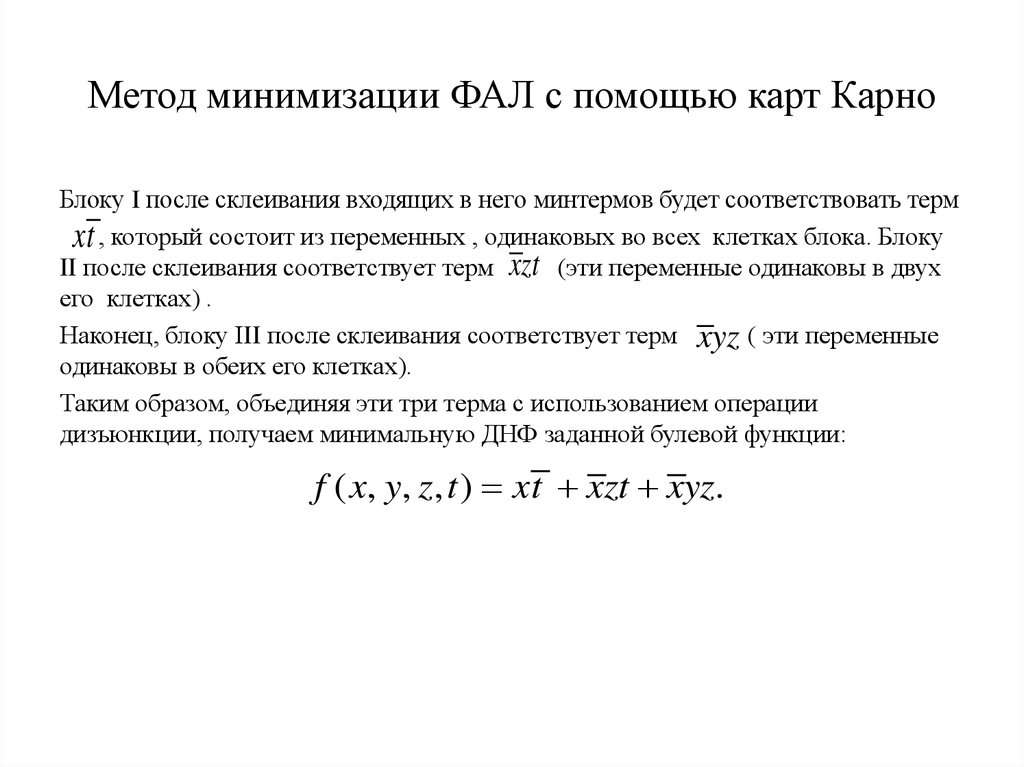

Блоку I после склеивания входящих в него минтермов будет соответствовать термxt , который состоит из переменных , одинаковых во всех клетках блока. Блоку

II после склеивания соответствует терм xzt (эти переменные одинаковы в двух

его клетках) .

Наконец, блоку III после склеивания соответствует терм xyz ( эти переменные

одинаковы в обеих его клетках).

Таким образом, объединяя эти три терма с использованием операции

дизъюнкции, получаем минимальную ДНФ заданной булевой функции:

f ( x, y, z , t ) xt xzt xyz.

35. Полный одноразрядный двоичный сумматор

Он имеет три входа: a, b — для двух слагаемых и p — для переноса из предыдущего (болеемладшего) разряда и два выхода: S — сумма, P — перенос в следующий (более старший)

разряд. Обозначением полного двоичного сумматора служат буквы SM. Работу его отражает

следующая таблица истинности:

№

наб.

a

b

p

P

S

0

0

0

0

0

0

1

0

0

1

0

1

2

0

1

0

0

1

3

0

1

1

1

0

4

1

0

0

0

1

5

1

0

1

1

0

6

1

1

0

1

0

7

1

1

1

1

1

36. Полный одноразрядный двоичный сумматор (ПРОДОЛЖЕНИЕ)

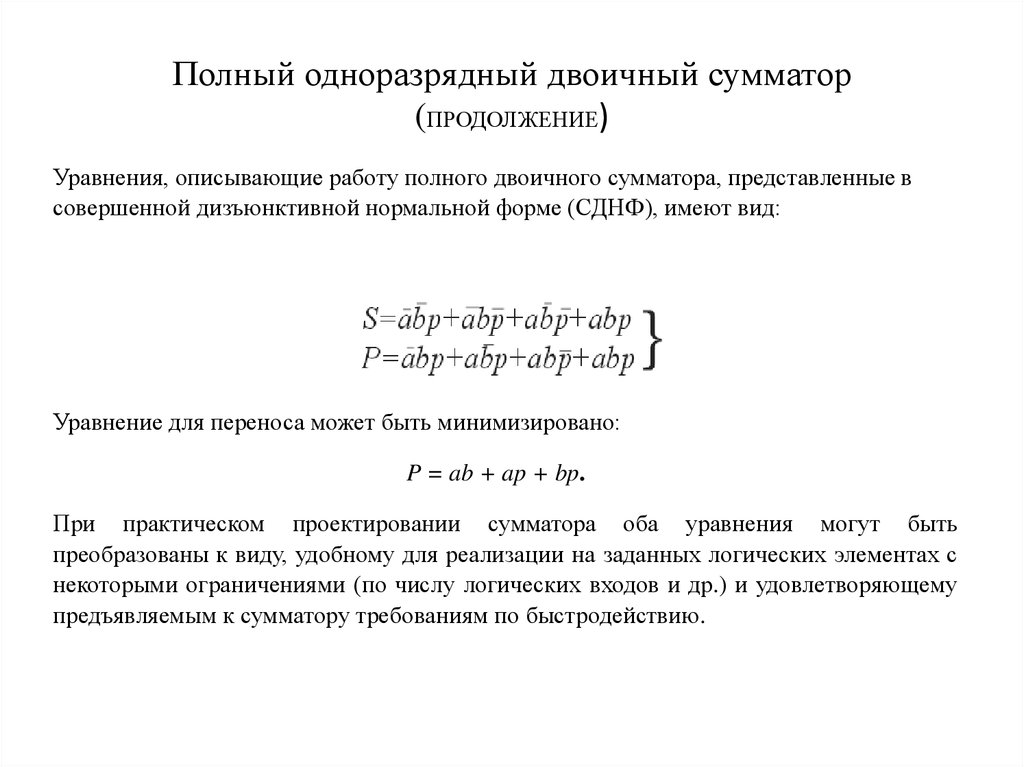

Уравнения, описывающие работу полного двоичного сумматора, представленные всовершенной дизъюнктивной нормальной форме (СДНФ), имеют вид:

Уравнение для переноса может быть минимизировано:

P = ab + ap + bp.

При практическом проектировании сумматора оба уравнения могут быть

преобразованы к виду, удобному для реализации на заданных логических элементах с

некоторыми ограничениями (по числу логических входов и др.) и удовлетворяющему

предъявляемым к сумматору требованиям по быстродействию.

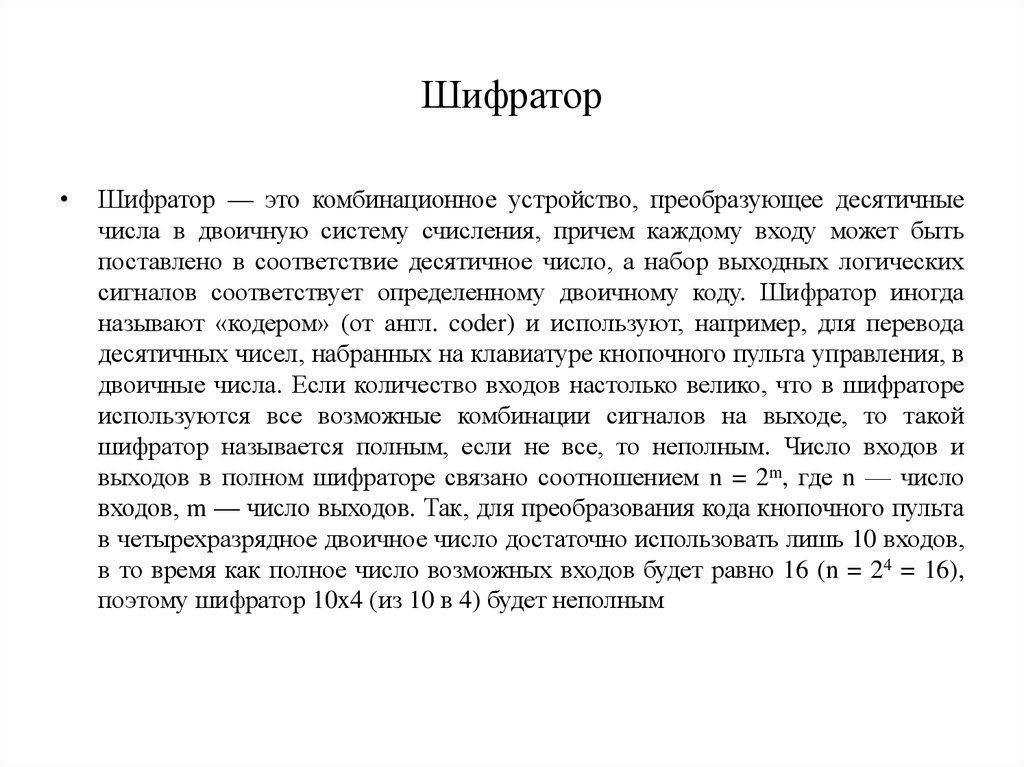

37. Шифратор

Шифратор — это комбинационное устройство, преобразующее десятичные

числа в двоичную систему счисления, причем каждому входу может быть

поставлено в соответствие десятичное число, а набор выходных логических

сигналов соответствует определенному двоичному коду. Шифратор иногда

называют «кодером» (от англ. coder) и используют, например, для перевода

десятичных чисел, набранных на клавиатуре кнопочного пульта управления, в

двоичные числа. Если количество входов настолько велико, что в шифраторе

используются все возможные комбинации сигналов на выходе, то такой

шифратор называется полным, если не все, то неполным. Число входов и

выходов в полном шифраторе связано соотношением n = 2m, где n — число

входов, m — число выходов. Так, для преобразования кода кнопочного пульта

в четырехразрядное двоичное число достаточно использовать лишь 10 входов,

в то время как полное число возможных входов будет равно 16 (n = 24 = 16),

поэтому шифратор 10x4 (из 10 в 4) будет неполным

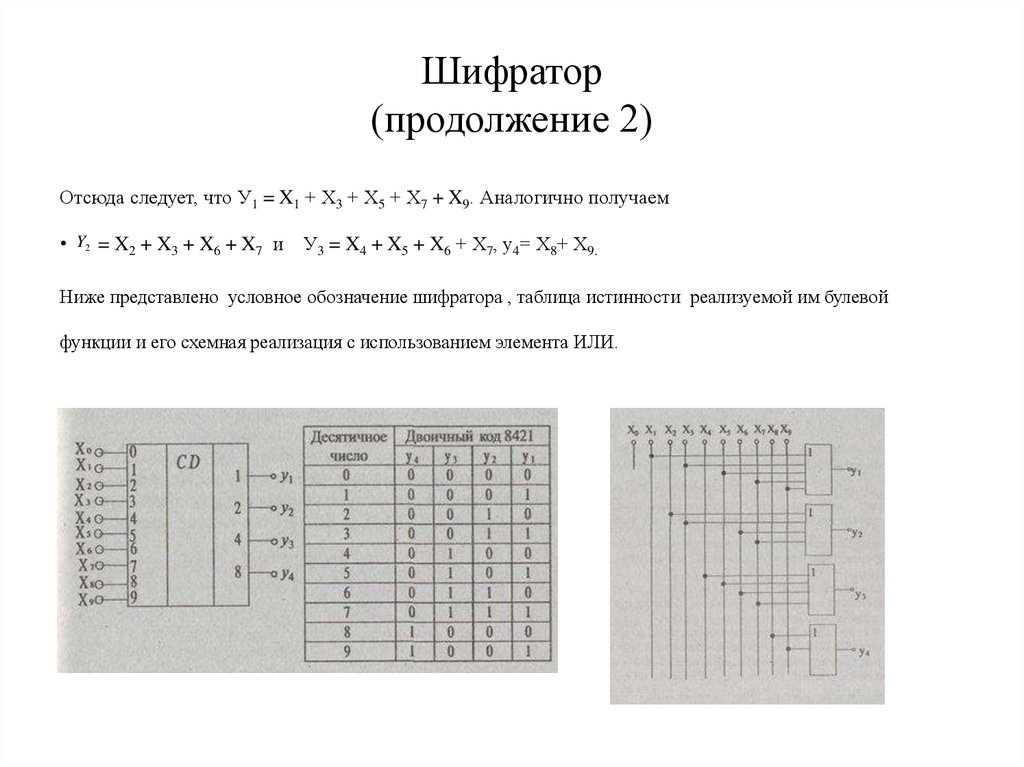

38. Шифратор (продолжение 1)

Рассмотрим пример построения шифратора для преобразованиядесятиразрядного единичного кода (десятичных чисел от 0 до 9) в

двоичный код. При этом предполагается, что сигнал,

соответствующий логической единице, в каждый момент времени

подается только на один вход. Условное обозначение такого

шифратора и таблица соответствия кода приведены наследующем

слайде. Используя данную таблицу соответствия, запишем

логические выражения, включая в логическую сумму те входные

переменные, которые соответствуют единице некоторой выходной

переменной. Так, на выходе у, будет логическая «1»тогда, когда

логическая «1» будет или на входе X1, или Х3, или Х5, или Х7,

или X9.

39. Шифратор (продолжение 2)

Отсюда следует, что У1 = X1 + Х3 + Х5 + Х7 + X9. Аналогично получаем• Y2 = X2 + X3 + X6 + X7 и У3 = X4 + X5 + X6 + Х7, у4= Х8+ Х9.

Ниже представлено условное обозначение шифратора , таблица истинности реализуемой им булевой

функции и его схемная реализация с использованием элемента ИЛИ.

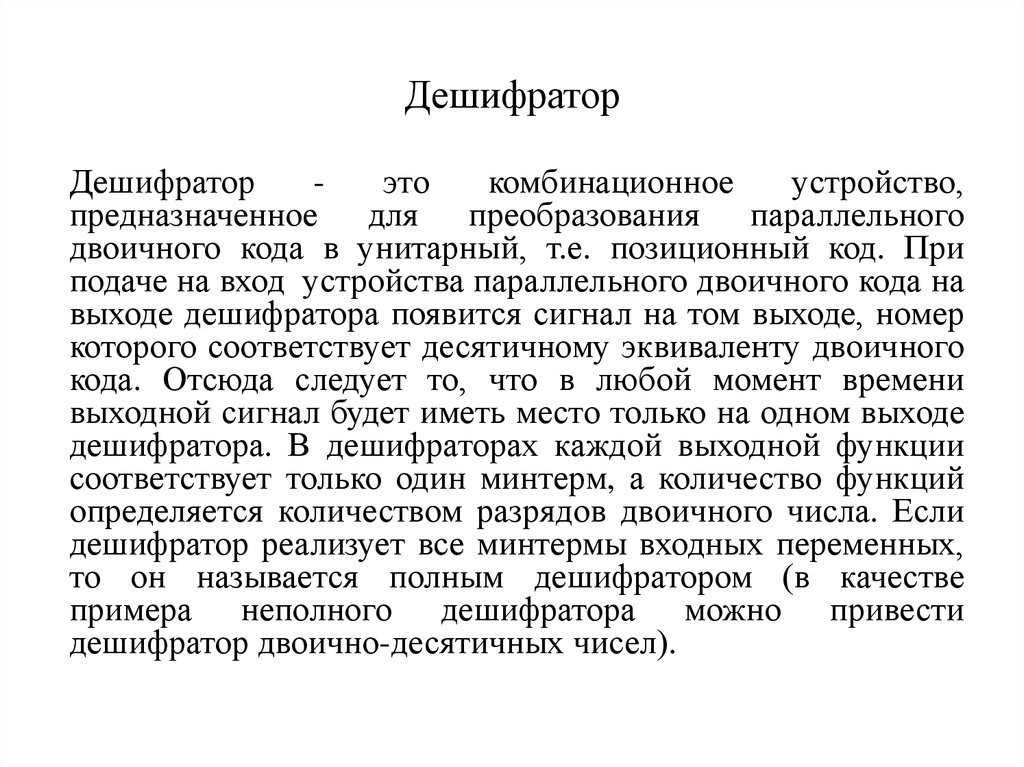

40. Дешифратор

Дешифраторэто

комбинационное

устройство,

предназначенное для преобразования параллельного

двоичного кода в унитарный, т.е. позиционный код. При

подаче на вход устройства параллельного двоичного кода на

выходе дешифратора появится сигнал на том выходе, номер

которого соответствует десятичному эквиваленту двоичного

кода. Отсюда следует то, что в любой момент времени

выходной сигнал будет иметь место только на одном выходе

дешифратора. В дешифраторах каждой выходной функции

соответствует только один минтерм, а количество функций

определяется количеством разрядов двоичного числа. Если

дешифратор реализует все минтермы входных переменных,

то он называется полным дешифратором (в качестве

примера неполного дешифратора можно привести

дешифратор двоично-десятичных чисел).

41. Дешифратор (продолжение 1)

Например, двухразрядный дешифратор должен иметь 4 выхода. Для каждого выхода

записываем логическое выражение на основе СДНФ, построенной по таблице

истинности

Таблица истинности двухразрядного дешифратора

x1

x2

y0

y1

y2

y3

0

0

1

0

0

0

0

1

0

1

0

0

1

0

0

0

1

0

1

1

0

0

0

1

Логические выражения для выходов имеют следующий вид:

у 0 x1·x2 у1 x1·x2

у 2 x1·x2

у3 x1·x2

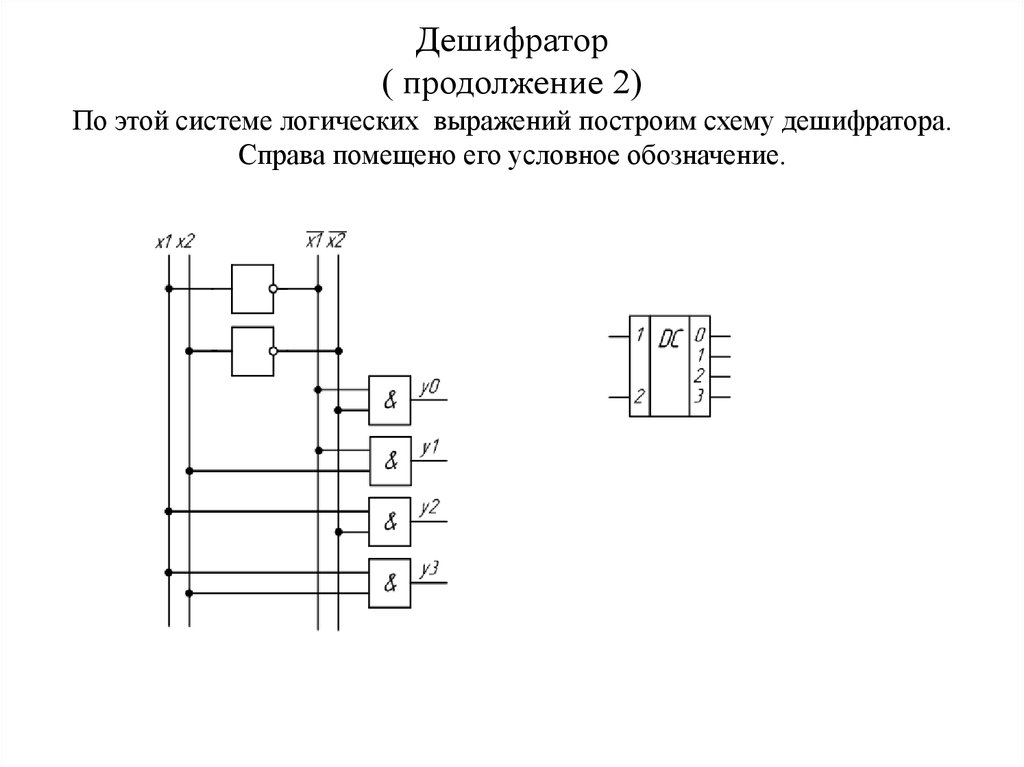

42. Дешифратор ( продолжение 2) По этой системе логических выражений построим схему дешифратора. Справа помещено его условное

обозначение.43. Мультиплексоры и демультиплексоры

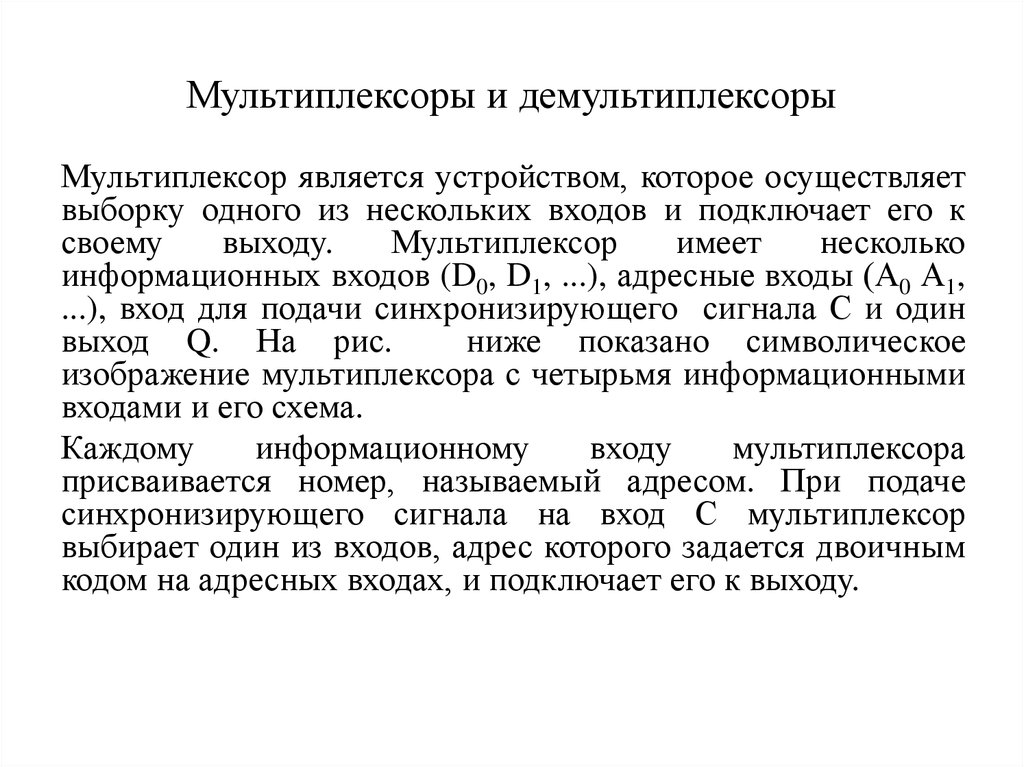

Мультиплексор является устройством, которое осуществляетвыборку одного из нескольких входов и подключает его к

своему

выходу.

Мультиплексор

имеет

несколько

информационных входов (D0, D1, ...), адресные входы (А0 А1,

...), вход для подачи синхронизирующего сигнала С и один

выход Q. На рис.

ниже показано символическое

изображение мультиплексора с четырьмя информационными

входами и его схема.

Каждому

информационному

входу

мультиплексора

присваивается номер, называемый адресом. При подаче

синхронизирующего сигнала на вход С мультиплексор

выбирает один из входов, адрес которого задается двоичным

кодом на адресных входах, и подключает его к выходу.

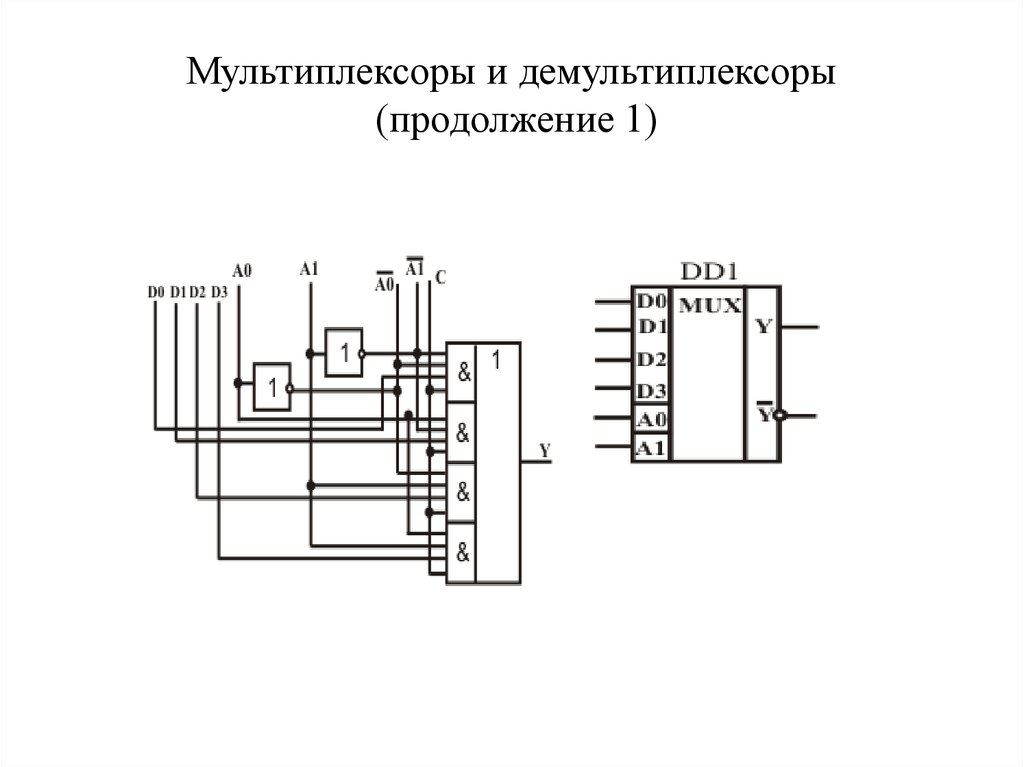

44. Мультиплексоры и демультиплексоры (продолжение 1)

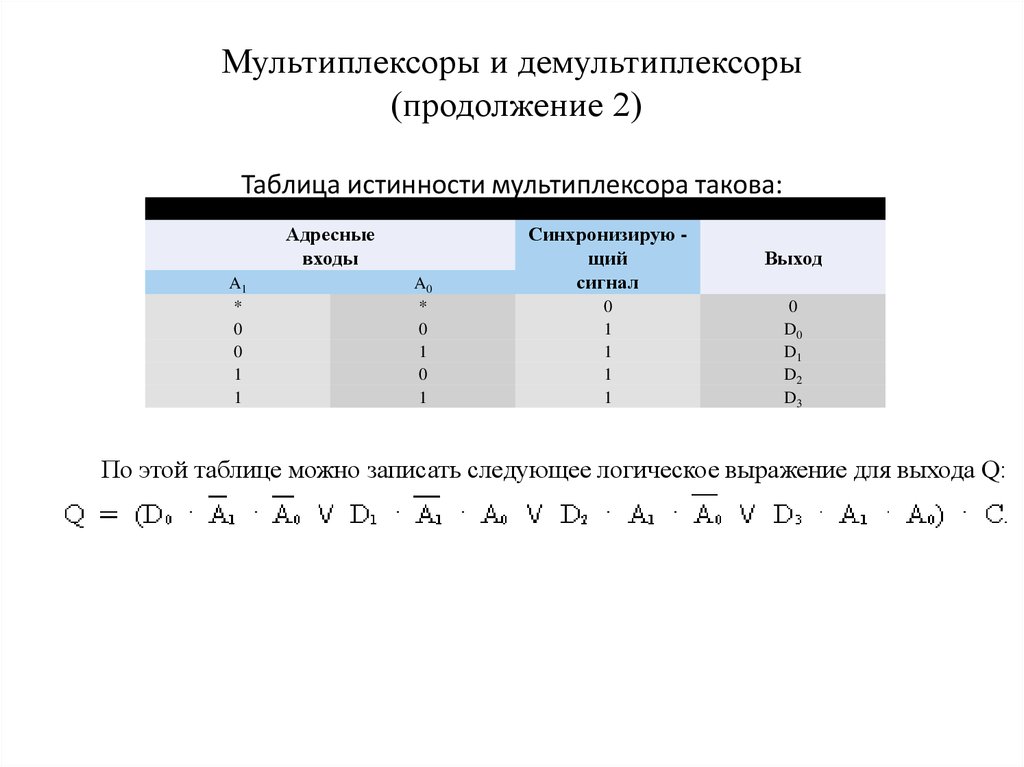

45. Мультиплексоры и демультиплексоры (продолжение 2) Таблица истинности мультиплексора такова:

Адресныевходы

A1

*

0

0

1

1

A0

*

0

1

0

1

Синхронизирую щий

сигнал

Выход

0

1

1

1

1

0

D0

D1

D2

D3

По этой таблице можно записать следующее логическое выражение для выхода Q:

46. Мультиплексоры и демультиплексоры (продолжение 3)

ДемультиплексорыДемультиплексор имеет один информационный вход и несколько выходов. Он

представляет собой устройство, которое осуществляет коммутацию входа к

одному из выходов, имеющему заданный адрес (номер). На следующем слайде

показано символическое изображение демультиплексора с четырьмя выходами и

таблица истинности, определяющая его функционирование.

Объединяя мультиплексор с демультиплексором, можно построить устройство, в

котором по заданным адресам один из входов подключается к одному из выходов

.Таким образом, может быть выполнена любая комбинация соединений входов с

выходами.

Например, при комбинации значений адресных переменных xl = l, x2 = 0, x3 = 0, x4

= 0 вход D2 окажется подключенным к выходу Y0.

Использование демультиплексора может существенно упростить построение

логического устройства, имеющего несколько выходов, на которых формируются

различные логические функции одних и тех же переменных.

Заметим, что если на вход демультиплексора подавать константу D = 1, то на

выбранном в соответствии с заданным адресом выходе будет лог. 1, на остальных

выходах - лог. 0. При этом по выполняемой функции демультиплексор

превращается в дешифратор.

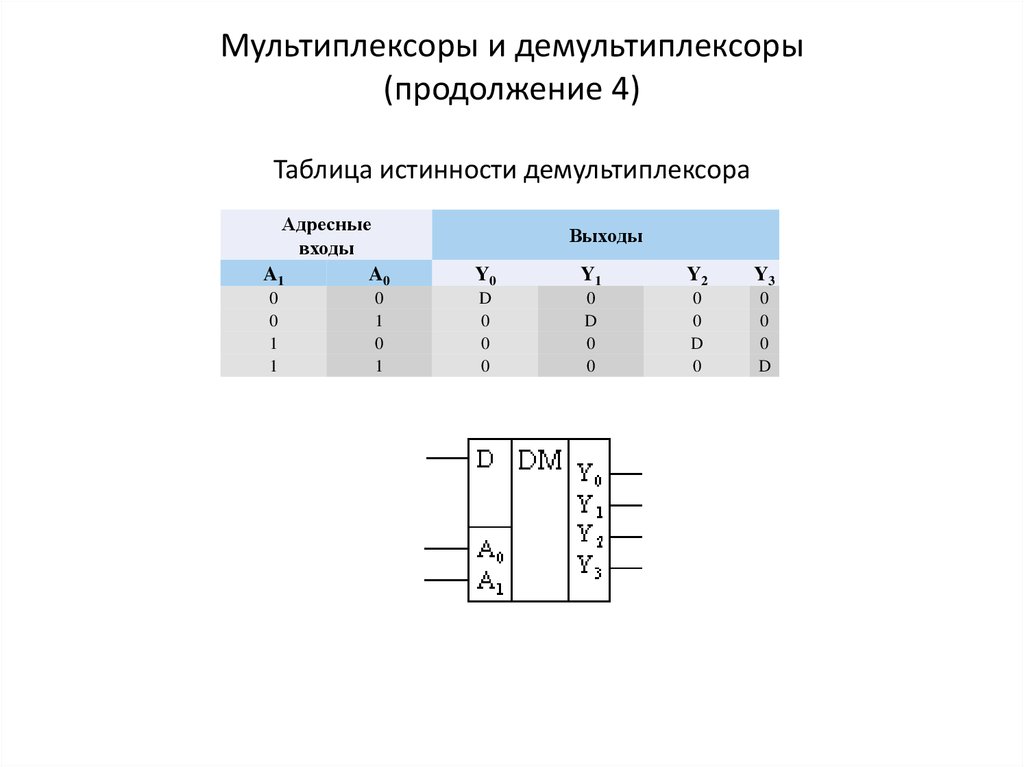

47. Мультиплексоры и демультиплексоры (продолжение 4) Таблица истинности демультиплексора

Адресныевходы

A1

A0

0

0

1

1

0

1

0

1

Выходы

Y0

Y1

Y2

Y3

D

0

0

0

0

D

0

0

0

0

D

0

0

0

0

D

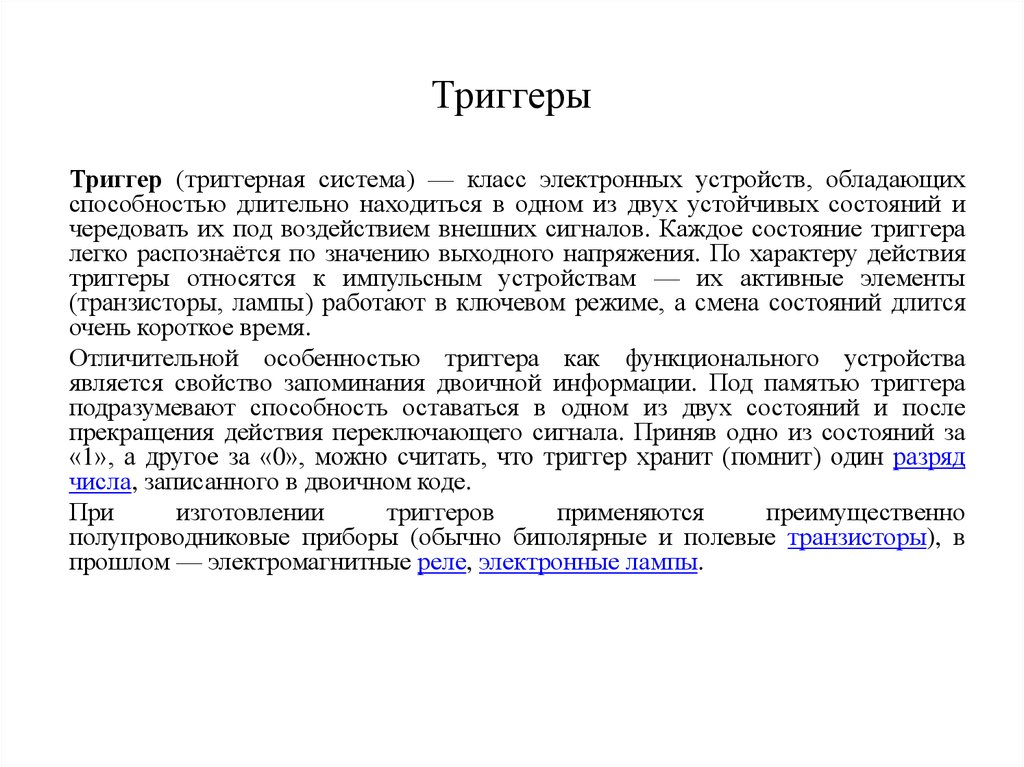

48. Триггеры

Триггер (триггерная система) — класс электронных устройств, обладающихспособностью длительно находиться в одном из двух устойчивых состояний и

чередовать их под воздействием внешних сигналов. Каждое состояние триггера

легко распознаётся по значению выходного напряжения. По характеру действия

триггеры относятся к импульсным устройствам — их активные элементы

(транзисторы, лампы) работают в ключевом режиме, а смена состояний длится

очень короткое время.

Отличительной особенностью триггера как функционального устройства

является свойство запоминания двоичной информации. Под памятью триггера

подразумевают способность оставаться в одном из двух состояний и после

прекращения действия переключающего сигнала. Приняв одно из состояний за

«1», а другое за «0», можно считать, что триггер хранит (помнит) один разряд

числа, записанного в двоичном коде.

При

изготовлении

триггеров

применяются

преимущественно

полупроводниковые приборы (обычно биполярные и полевые транзисторы), в

прошлом — электромагнитные реле, электронные лампы.

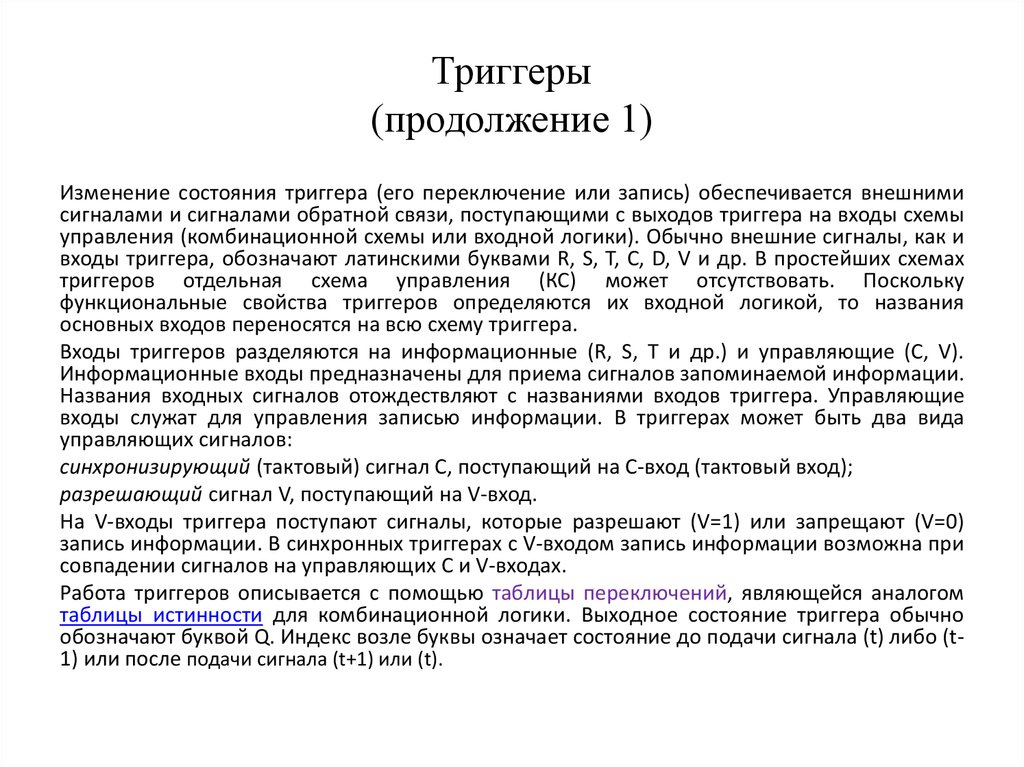

49. Триггеры (продолжение 1)

Изменение состояния триггера (его переключение или запись) обеспечивается внешнимисигналами и сигналами обратной связи, поступающими с выходов триггера на входы схемы

управления (комбинационной схемы или входной логики). Обычно внешние сигналы, как и

входы триггера, обозначают латинскими буквами R, S, T, C, D, V и др. В простейших схемах

триггеров отдельная схема управления (КС) может отсутствовать. Поскольку

функциональные свойства триггеров определяются их входной логикой, то названия

основных входов переносятся на всю схему триггера.

Входы триггеров разделяются на информационные (R, S, T и др.) и управляющие (С, V).

Информационные входы предназначены для приема сигналов запоминаемой информации.

Названия входных сигналов отождествляют с названиями входов триггера. Управляющие

входы служат для управления записью информации. В триггерах может быть два вида

управляющих сигналов:

синхронизирующий (тактовый) сигнал С, поступающий на С-вход (тактовый вход);

разрешающий сигнал V, поступающий на V-вход.

На V-входы триггера поступают сигналы, которые разрешают (V=1) или запрещают (V=0)

запись информации. В синхронных триггерах с V-входом запись информации возможна при

совпадении сигналов на управляющих С и V-входах.

Работа триггеров описывается с помощью таблицы переключений, являющейся аналогом

таблицы истинности для комбинационной логики. Выходное состояние триггера обычно

обозначают буквой Q. Индекс возле буквы означает состояние до подачи сигнала (t) либо (t1) или после подачи сигнала (t+1) или (t).

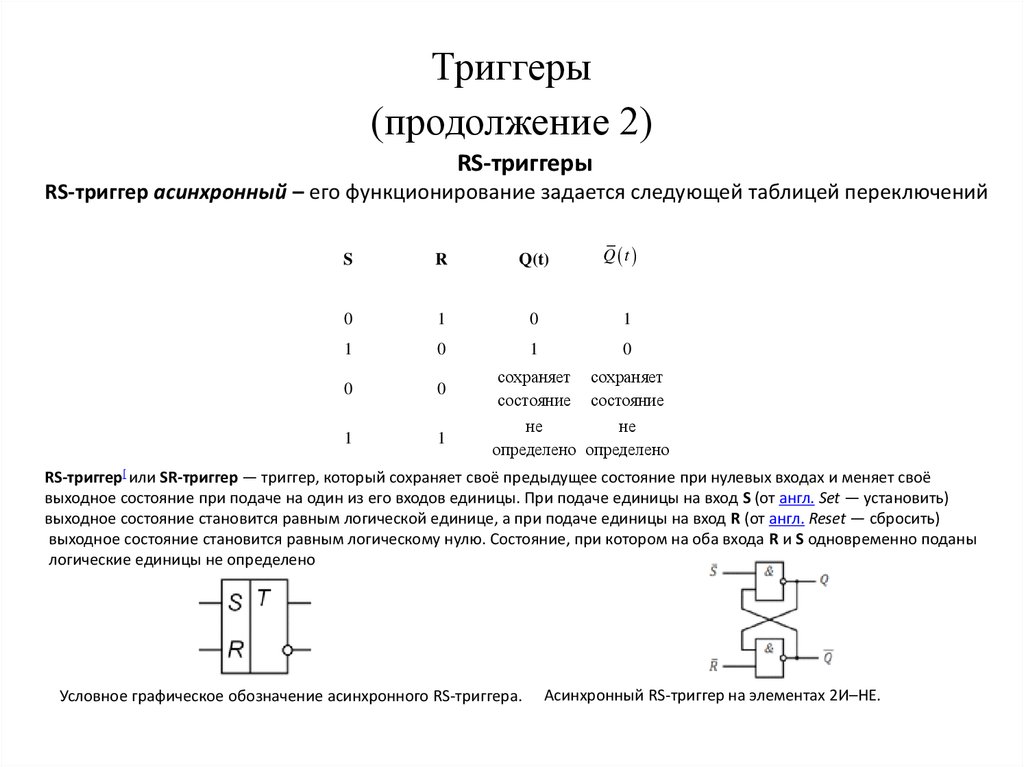

50. Триггеры (продолжение 2)

RS-триггерыRS-триггер асинхронный – его функционирование задается следующей таблицей переключений

Q t

S

R

Q(t)

0

1

0

1

1

0

1

0

0

0

сохраняет

состояние

сохраняет

состояние

1

1

не

не

определено определено

RS-триггер[ или SR-триггер — триггер, который сохраняет своё предыдущее состояние при нулевых входах и меняет своё

выходное состояние при подаче на один из его входов единицы. При подаче единицы на вход S (от англ. Set — установить)

выходное состояние становится равным логической единице, а при подаче единицы на вход R (от англ. Reset — сбросить)

выходное состояние становится равным логическому нулю. Состояние, при котором на оба входа R и S одновременно поданы

логические единицы не определено

Условное графическое обозначение асинхронного RS-триггера.

Асинхронный RS-триггер на элементах 2И–НЕ.

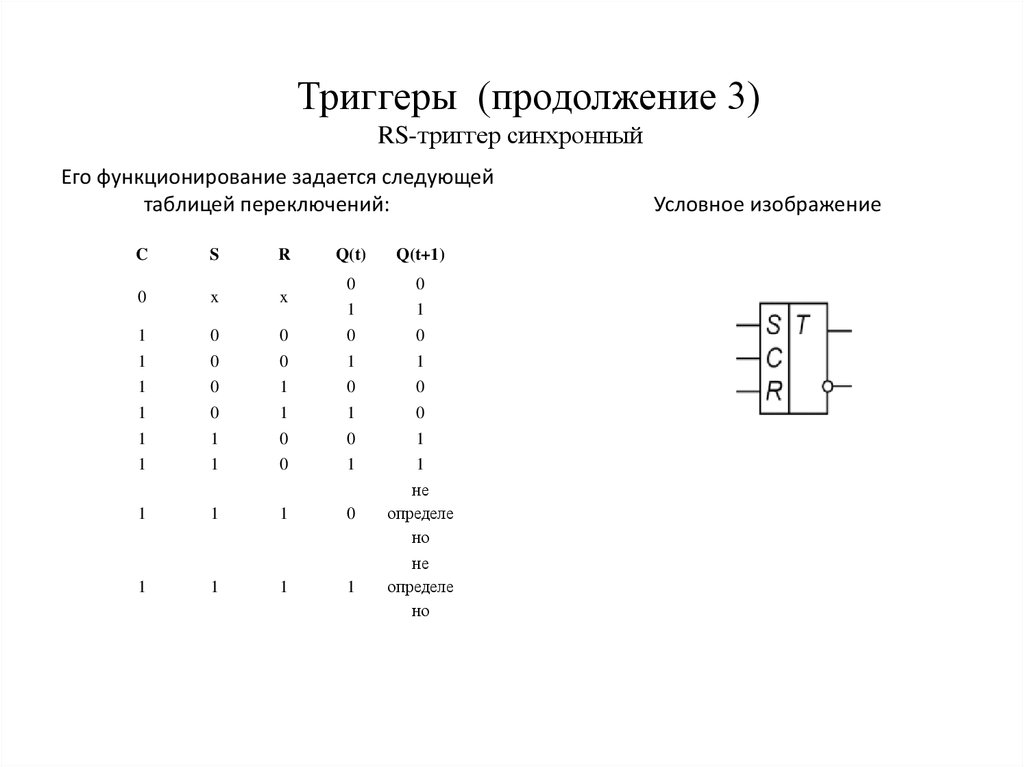

51. Его функционирование задается следующей таблицей переключений: Условное изображение

Триггеры (продолжение 3)RS-триггер синхронный

Его функционирование задается следующей

таблицей переключений:

C

S

R

Q(t)

Q(t+1)

0

x

x

0

0

1

1

1

0

0

0

0

1

0

0

1

1

1

0

1

0

0

1

0

1

1

0

1

1

0

0

1

1

1

0

1

1

0

не

определе

но

1

не

определе

но

1

1

1

1

1

1

Условное изображение

52. Триггеры (продолжение 4)

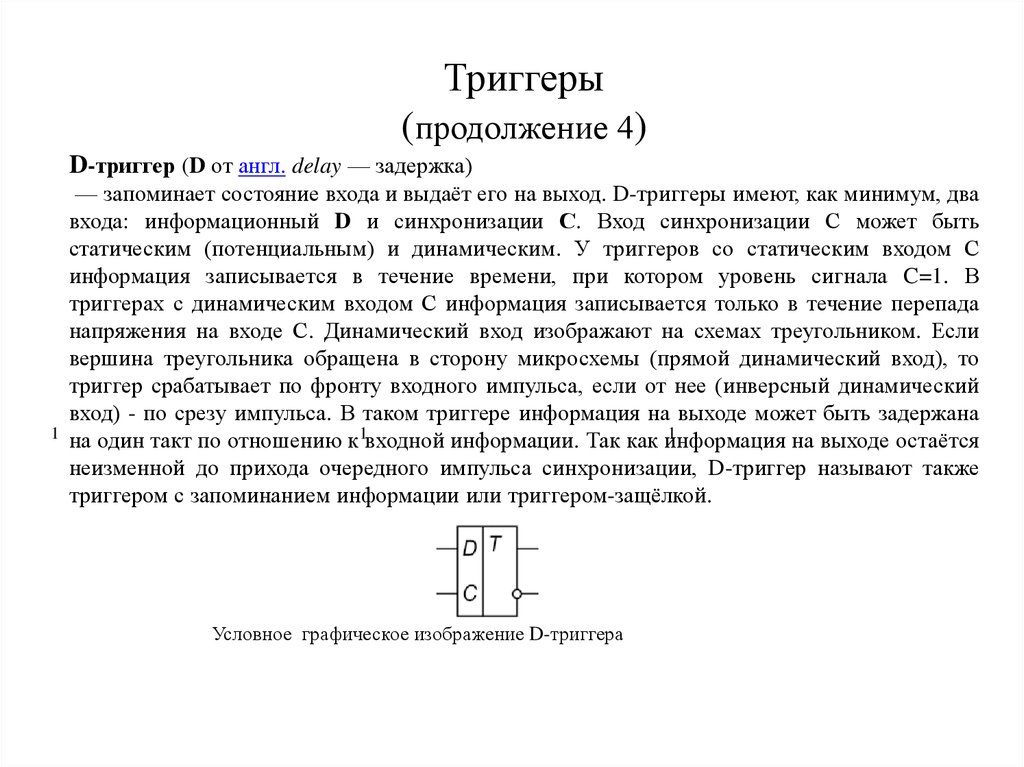

D-триггер (D от англ. delay — задержка)1

— запоминает состояние входа и выдаёт его на выход. D-триггеры имеют, как минимум, два

входа: информационный D и синхронизации С. Вход синхронизации С может быть

статическим (потенциальным) и динамическим. У триггеров со статическим входом С

информация записывается в течение времени, при котором уровень сигнала C=1. В

триггерах с динамическим входом С информация записывается только в течение перепада

напряжения на входе С. Динамический вход изображают на схемах треугольником. Если

вершина треугольника обращена в сторону микросхемы (прямой динамический вход), то

триггер срабатывает по фронту входного импульса, если от нее (инверсный динамический

вход) - по срезу импульса. В таком триггере информация на выходе может быть задержана

1

на один такт по отношению к1входной информации. Так как информация

на выходе остаётся

неизменной до прихода очередного импульса синхронизации, D-триггер называют также

триггером с запоминанием информации или триггером-защёлкой.

Условное графическое изображение D-триггера

53. Триггер ( продолжение 5)

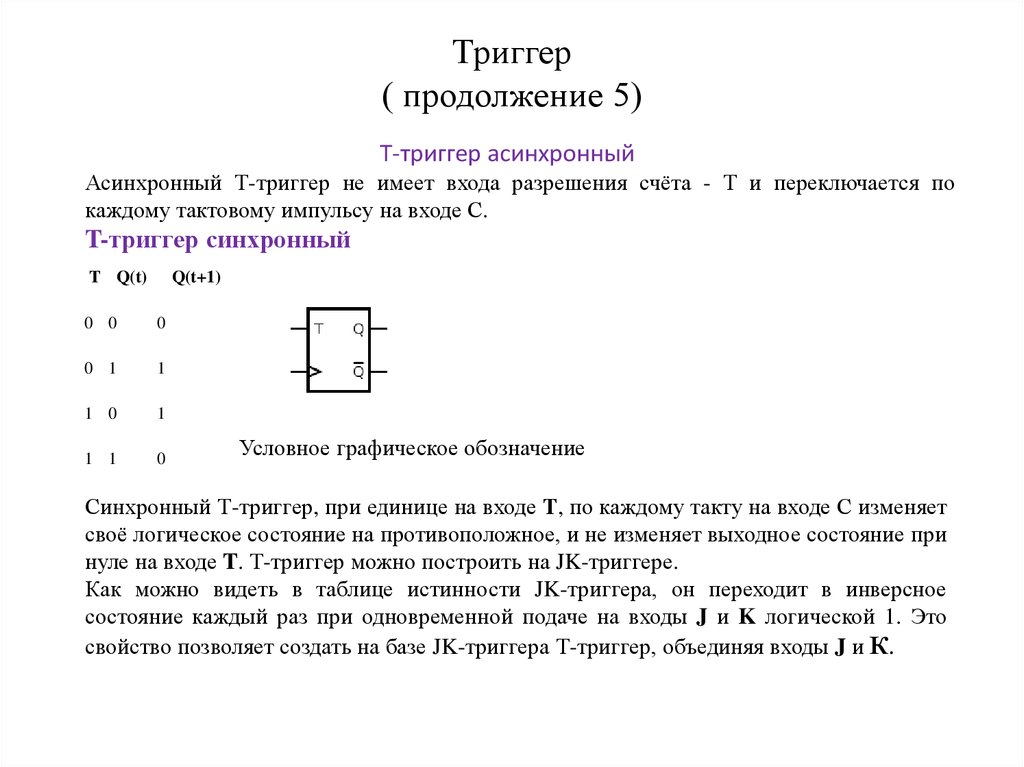

Т-триггер асинхронныйАсинхронный Т-триггер не имеет входа разрешения счёта - Т и переключается по

каждому тактовому импульсу на входе С.

T-триггер синхронный

T Q(t)

Q(t+1)

0 0

0

0 1

1

1 0

1

1 1

0

Условное графическое обозначение

Синхронный Т-триггер, при единице на входе Т, по каждому такту на входе С изменяет

своё логическое состояние на противоположное, и не изменяет выходное состояние при

нуле на входе T. Т-триггер можно построить на JK-триггере.

Как можно видеть в таблице истинности JK-триггера, он переходит в инверсное

состояние каждый раз при одновременной подаче на входы J и K логической 1. Это

свойство позволяет создать на базе JK-триггера Т-триггер, объединяя входы J и К.

54. Триггеры (продолжение 6)

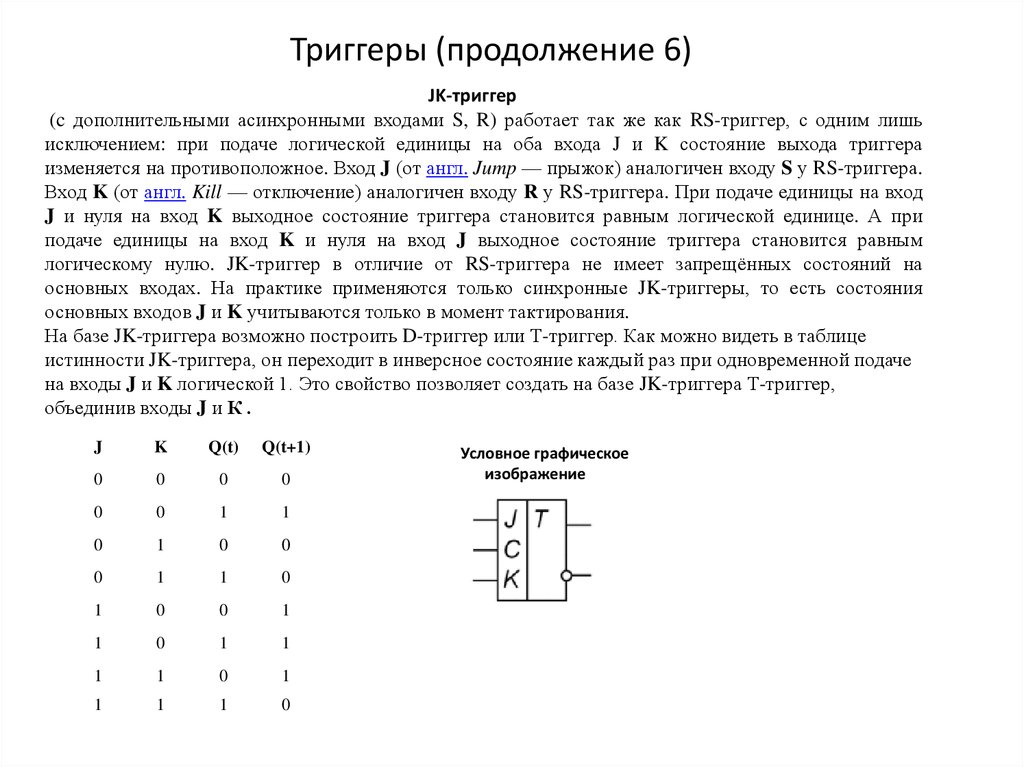

JK-триггер(c дополнительными асинхронными входами S, R) работает так же как RS-триггер, с одним лишь

исключением: при подаче логической единицы на оба входа J и K состояние выхода триггера

изменяется на противоположное. Вход J (от англ. Jump — прыжок) аналогичен входу S у RS-триггера.

Вход K (от англ. Kill — отключение) аналогичен входу R у RS-триггера. При подаче единицы на вход

J и нуля на вход K выходное состояние триггера становится равным логической единице. А при

подаче единицы на вход K и нуля на вход J выходное состояние триггера становится равным

логическому нулю. JK-триггер в отличие от RS-триггера не имеет запрещённых состояний на

основных входах. На практике применяются только синхронные JK-триггеры, то есть состояния

основных входов J и K учитываются только в момент тактирования.

На базе JK-триггера возможно построить D-триггер или Т-триггер. Как можно видеть в таблице

истинности JK-триггера, он переходит в инверсное состояние каждый раз при одновременной подаче

на входы J и K логической 1. Это свойство позволяет создать на базе JK-триггера Т-триггер,

объединив входы J и К .

J

K

Q(t)

Q(t+1)

0

0

0

0

0

0

1

1

0

1

0

0

0

1

1

0

1

0

0

1

1

0

1

1

1

1

0

1

1

1

1

0

Условное графическое

изображение

55. Счетчики и делители частоты

Cчетчики позволяют вести подсчет электрических импульсов,количество которых (поступивших на вход счетчика) представляется,

обычно, в параллельном коде. Счетчики могут отличаться модулем счета

и типом счетной последовательности (двоичной, двоично-десятичной и

т.п). Цифровые устройства, выполненные по схеме счетчика, но имеющие

один счетный вход и один выход, называются делителями частоты.

Таким образом, любой счетчик может служить в качестве делителя

частоты, если используется информация только одного из его выходов.

Счетчики и делители подразделяются на асинхронные и синхронные. У

синхронных счетчиков все разрядные триггеры синхронизируются

параллельно одними и теми же синхроимпульсами. Асинхронные

счетчики имеют последовательную синхронизацию, т.е. каждый

последующий разрядный триггер синхронизируется выходными

импульсами триггера предыдущего разряда.

56. Счетчики и делители частоты (2)

Счетчики, независимо от способа синхронизации, подразделяются на счетчики прямогосчета (суммирующие) и на счетчики обратного счета (вычитающие). В интегральном

исполнении выпускаются также реверсивные счетчики, в которых имеется специальный

вход для переключения режима работы, т.е. направления счета. В качестве разрядных

триггеров счетчиков и делителей могут быть использованы двухступенчатые D-триггеры, Ти JK-триггеры.

Счетчики относятся к последовательностным устройствам с циклически повторяющейся

последовательностью состояний. Число, соответствующее количеству импульсов

поступивших на вход счетчика, при котором счетчик “возвращается” в исходное состояние,

называется модулем или коэффициентом счета. Модуль счета, обычно, обозначают буквой

М или Ксч.. В общем случае для n - разрядного счетчика - М = 2n. Модуль счета счетчика

численно совпадает с модулем деления делителя частоты. Счетчик по модулю 8 позволяет

реализовать (без дополнительных схемных затрат) делитель частоты на 8. Это значит, что

данный делитель делит частоту входной импульсной последовательности на 8.

57. Счетчики и делители частоты (3)

Асинхронный двоичный счетчик. Асинхронный двоичный счетчикпредставляет собой совокупность последовательно соединенных триггеров (D или JK ), каждый из которых ассоциируется с битом в двоичном представлении

числа. Если в счетчике m триггеров, то число возможных состояний счетчика

равно 2m, и, следовательно, модуль счета М также равен 2m. Счетная

последовательность в двоичном суммирующем счетчике начинается с нуля и

доходит до максимального числа 2m - 1, после чего снова проходит через нуль и

повторяется. В вычитающем двоичном счетчике последовательные двоичные

числа перебираются в обратном порядке, и при повторении последовательности

максимальное число следует за нулем.

Устройство двоичного суммирующего счетчика по модулю М=16, выполненного

на базе JK-триггеров, представлено на следующем слайде (рис. а) – схема, б)

таблица состояний триггеров, в) временные диаграммы работы 4-разрядного

счетчика на JK- триггерах) .

Как видно из рис. схемы, синхронизирующие входы всех триггеров, кроме

крайнего левого (Т1), соединены с выходами предыдущего.

58.

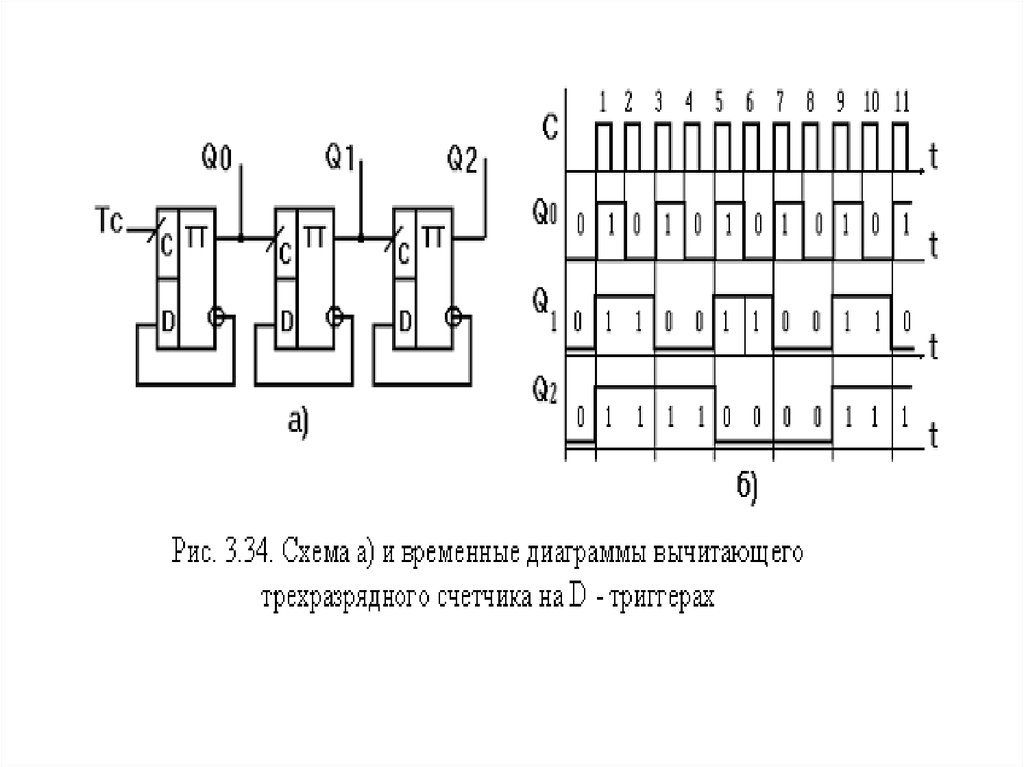

59. Счетчики и делители частоты (4)

Счетчики обратного счета (вычитающие счетчики)Схема (а) асинхронного 3-разрядного двоичного вычитающего счетчика,

построенного на базе D-триггеров, дана на следующем слайде.. Отметим, что

условия для изменения состояний триггеров вычитающих счетчиков аналогичны

условиям для суммирующих счетчиков с той лишь разницей, что они должны

“опираться” на значения инверсных, а не прямых выходов триггеров.

Следовательно, рассмотренный выше счетчик можно превратить в вычитающий,

просто переключив входы “С” триггеров с выходов Q на выходы .

Работа асинхронного вычитающего 3-разрядного счетчика на D-триггерах

иллюстрируется на следующем слайде (б). Из рис. следует, что после нулевого

состояния всех триггеров, с приходом первого синхроимпульса они

устанавливаются в состояние “1”. Поступление второго синхроимпульса

приводит к уменьшению этого числа на одну единицу и т.д. После поступления

восьмого импульса, снова, все триггеры обнуляются и цикл счета повторяется,

что соответствует модулю М=8.

60.

61. Счетчики и делители частоты (5)

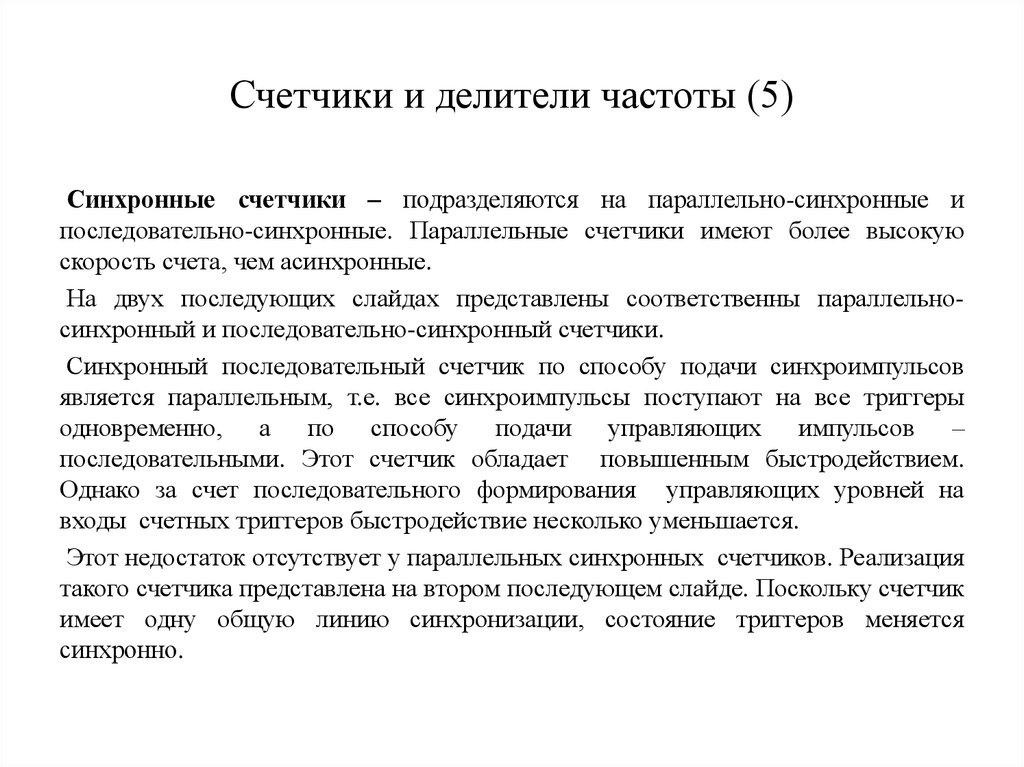

Синхронные счетчики – подразделяются на параллельно-синхронные ипоследовательно-синхронные. Параллельные счетчики имеют более высокую

скорость счета, чем асинхронные.

На двух последующих слайдах представлены соответственны параллельносинхронный и последовательно-синхронный счетчики.

Синхронный последовательный счетчик по способу подачи синхроимпульсов

является параллельным, т.е. все синхроимпульсы поступают на все триггеры

одновременно, а по способу подачи управляющих импульсов –

последовательными. Этот счетчик обладает повышенным быстродействием.

Однако за счет последовательного формирования управляющих уровней на

входы счетных триггеров быстродействие несколько уменьшается.

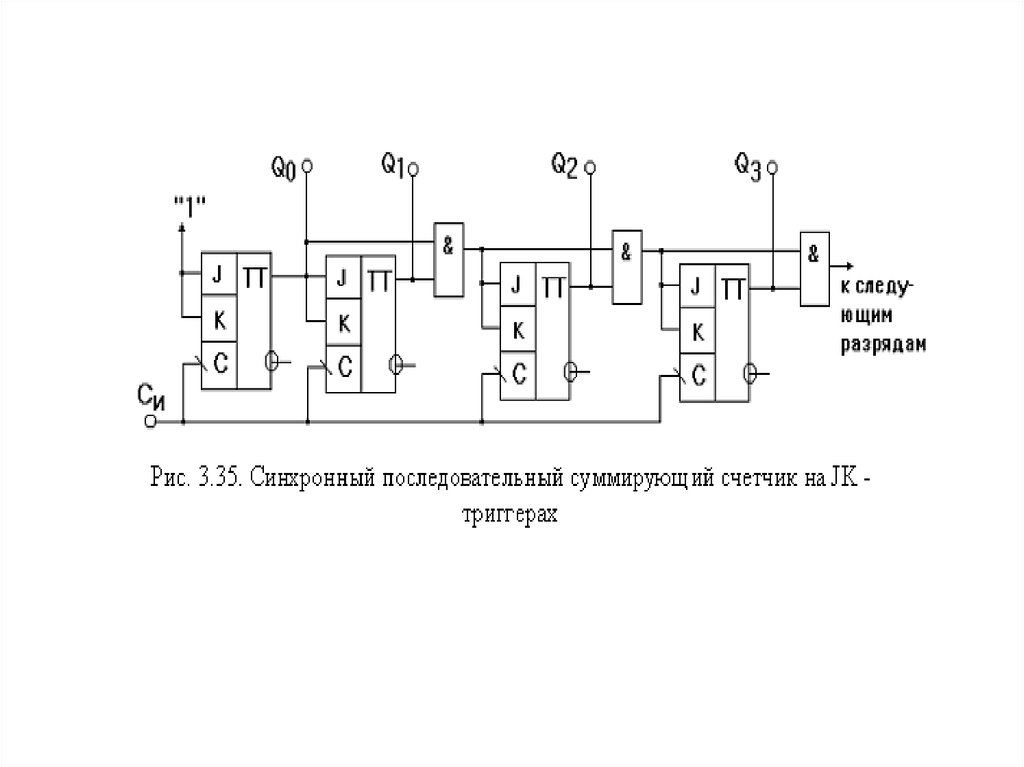

Этот недостаток отсутствует у параллельных синхронных счетчиков. Реализация

такого счетчика представлена на втором последующем слайде. Поскольку счетчик

имеет одну общую линию синхронизации, состояние триггеров меняется

синхронно.

62.

63.

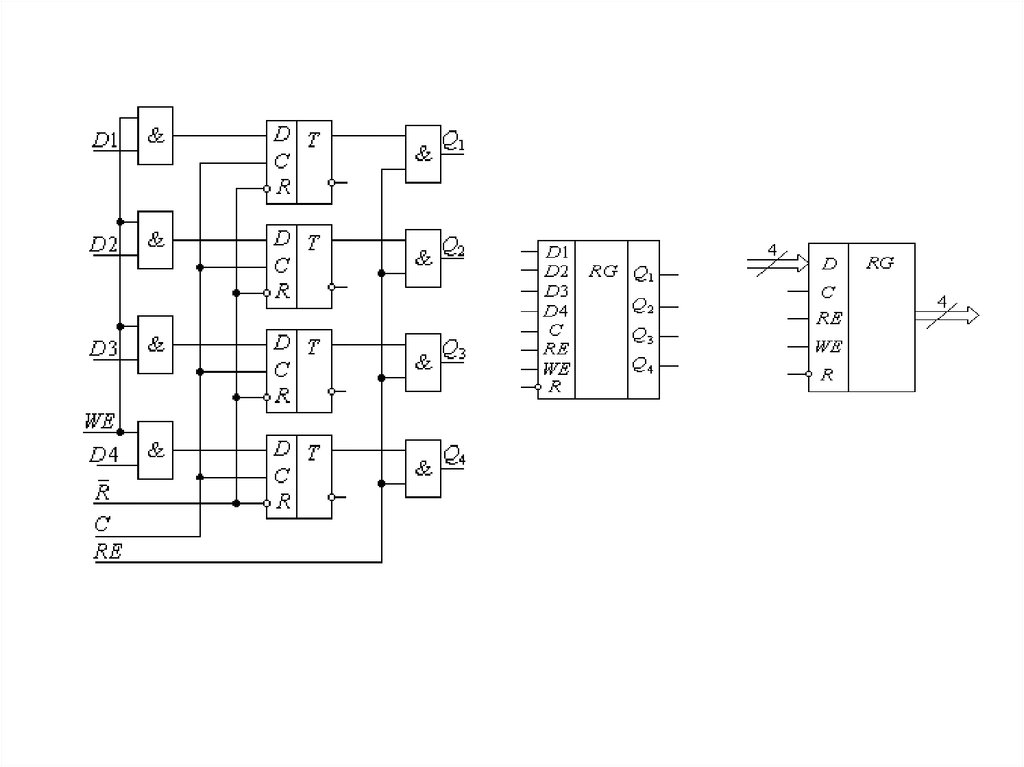

64. Регистры памяти

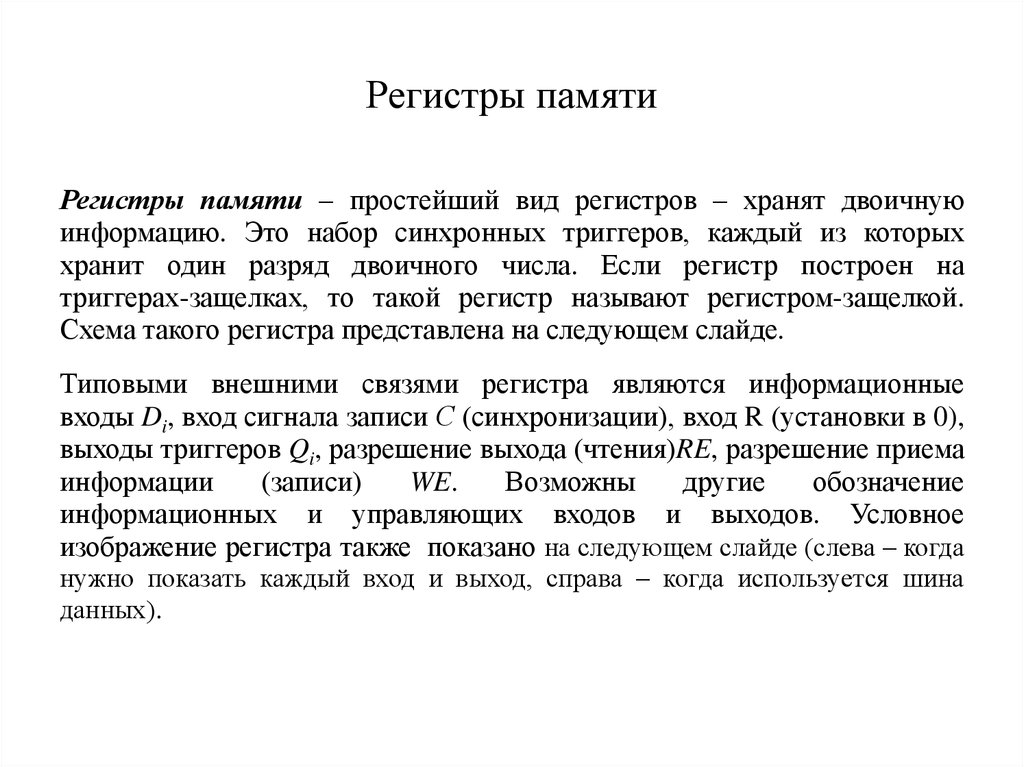

Регистры памяти – простейший вид регистров – хранят двоичнуюинформацию. Это набор синхронных триггеров, каждый из которых

хранит один разряд двоичного числа. Если регистр построен на

триггерах-защелках, то такой регистр называют регистром-защелкой.

Схема такого регистра представлена на следующем слайде.

Типовыми внешними связями регистра являются информационные

входы Di, вход сигнала записи С (синхронизации), вход R (установки в 0),

выходы триггеров Qi, разрешение выхода (чтения)RE, разрешение приема

информации

(записи)

WE.

Возможны

другие

обозначение

информационных и управляющих входов и выходов. Условное

изображение регистра также показано на следующем слайде (слева – когда

нужно показать каждый вход и выход, справа – когда используется шина

данных).

65.

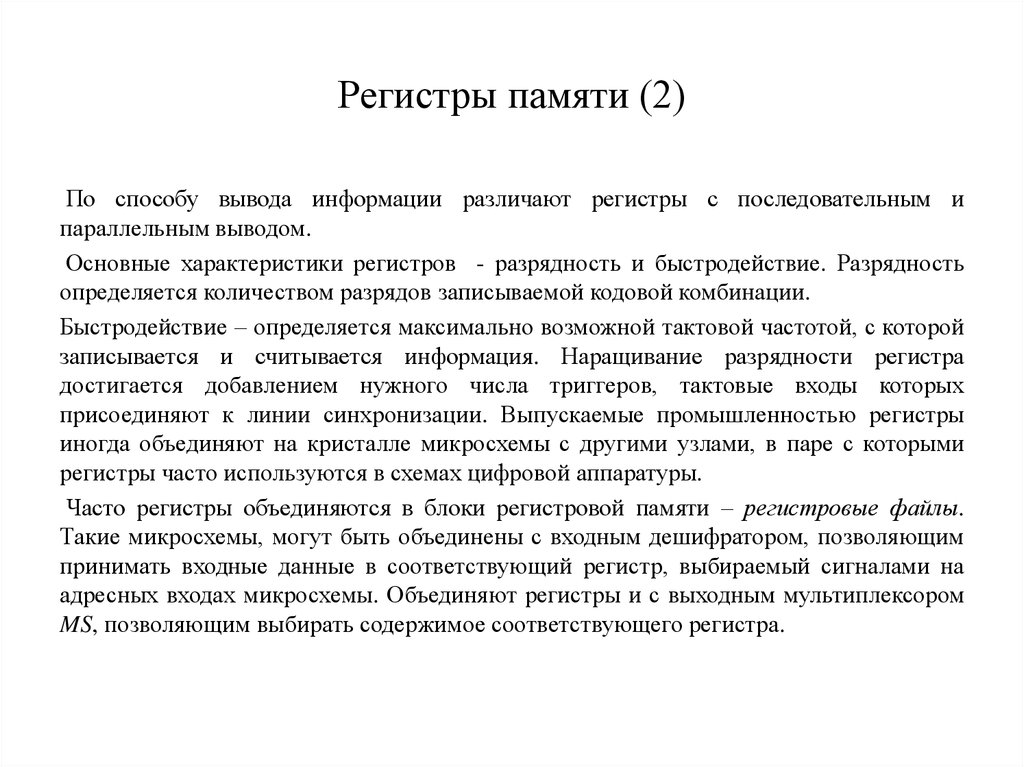

66. Регистры памяти (2)

По способу вывода информации различают регистры с последовательным ипараллельным выводом.

Основные характеристики регистров - разрядность и быстродействие. Разрядность

определяется количеством разрядов записываемой кодовой комбинации.

Быстродействие – определяется максимально возможной тактовой частотой, с которой

записывается и считывается информация. Наращивание разрядности регистра

достигается добавлением нужного числа триггеров, тактовые входы которых

присоединяют к линии синхронизации. Выпускаемые промышленностью регистры

иногда объединяют на кристалле микросхемы с другими узлами, в паре с которыми

регистры часто используются в схемах цифровой аппаратуры.

Часто регистры объединяются в блоки регистровой памяти – регистровые файлы.

Такие микросхемы, могут быть объединены с входным дешифратором, позволяющим

принимать входные данные в соответствующий регистр, выбираемый сигналами на

адресных входах микросхемы. Объединяют регистры и с выходным мультиплексором

MS, позволяющим выбирать содержимое соответствующего регистра.

67. Микропроцессоры

Микропроцессором (МП) называют цифровое устройство, изготовленное в виде БИС испособное выполнять по разработанной программе обработку информации. Как правило,

один МП не может выполнить задачу по обработке информации. Различные системы

контроля и управления, реализованные на основе МП, содержат определенное число

дополнительных

функциональных

устройств.

Такие

системы

называют

микропроцессорными. В основе построения микропроцессорных систем лежит

магистрально-модульный принцип. Это означает, что микропроцессорная система имеет

модульную организацию, т.е. строится из набора модулей. Под модулем в данном случае

понимается конструктивно, функционально и электрически законченное устройство,

позволяющее самостоятельно или в совокупности с другими модулями решать

поставленные перед ним задачи. Модули микропроцессорной системы используют

магистральный способ обмена информацией. Магистральный способ обеспечивает обмен

информацией между модулями с помощью единых магистралей. В микропроцессорных

системах обычно выделяются следующие магистрали: магистраль данных или шина

данных (ШД), адресная магистраль или шина адреса (ША) и магистраль управления или

шина управления (ШУ).

На следующем слайде представлена общая структурная схема микропроцессора.

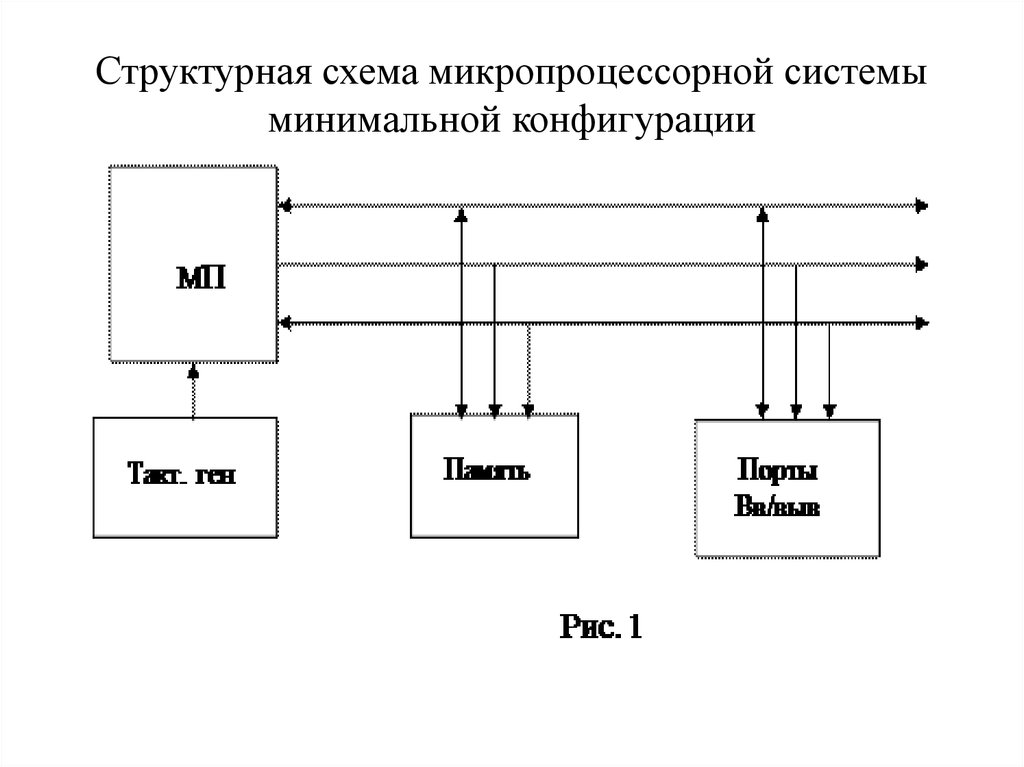

68. Структурная схема микропроцессорной системы минимальной конфигурации

69. Комментарии к структурной схеме МП

Центральным элементом в данной структуре является микропроцессор (МП),который осуществляет обработку информации в соответствии с введенной

программой и организует взаимодействие всех устройств, входящих в систему.

Работа МП происходит под воздействием синхронизирующих сигналов тактового

генератора (ТАКТ. ГЕН.), часто выполняемого в виде отдельного модуля. Память

МП реализуется в виде отдельного модуля на полупроводниковых БИС. Память

предназначена для хранения программы, согласно которой производится

управление работой МП. В памяти могут храниться данные, которые должны

быть обработаны в соответствии с программой. В память можно загрузить

промежуточные и окончательные результаты вычислений.

Для ввода программ и данных извне в память или регистры МП, а также вывода

результатов используется набор периферийных или внешних устройств (ВУ):

клавиатура, принтер, дисплей, накопители на магнитных дисках и др.

Подключение внешних устройств производится с помощью специальных

модулей - портов ввода-вывода, выполненных на БИС.

70. Комментарии к структурной схеме МП

Обмен информацией между МП и остальными модулями системыосуществляется по трем магистралям: ШД, ША, ШУ. ША служит для передачи

кода адреса, по которому производится обращение к устройствам памяти, вводавывода и другим устройствам, подключенным к МП. Обрабатываемая

информация и результаты вычислений передаются по магистрали данных (ШД).

Магистраль управления (ШУ) передает управляющие сигналы на все модули

МПС, настраивая на нужный режим внешние устройства, участвующие в

выполняемой команде.

МП ведет обработку информации в соответствии с программой, записанной в

одном из блоков памяти. Для получения кода команды, которую необходимо

исполнить, МП формирует на ША адрес ячейки памяти, в которой она записана, а

по магистрали управления - управляющие сигналы, обеспечивающие режим

считывания информации. Считанный из памяти код поступает по ШД в МП, где

он записывается в специальный регистр. В соответствии с записанным кодом

выполняются операции, необходимые для реализации команды.

71. Характеристики МП

Любой МП можно оценить с помощью следующих трех характеристик: длинойслова данных, количеством адресуемых слов памяти и скоростью выполнения

команд.

МП оперирует данными, представляемыми словами фиксированной длины

(последовательность из 0 и 1). Все слова перед обработкой хранятся в регистрах

МП. Число разрядов регистров кратно 8 и обычно составляет 8-, 16-, 32- или 64разряда.

Другой характеристикой МП является количество слов памяти, к которым он

может обращаться. Каждому слову в памяти, как уже ранее отмечалось,

присваивается номер или адрес. Адреса памяти начинаются с нуля и

представляются в двоичной системе счисления. Для МП с 8-разрядной ША

максимальный объем памяти 28 = 256 байт, а для 16-разрядных - 65536 байт или

64 Кбайт.

72. Характеристики МП

Следующей характеристикой МП является скорость, с которой он выполняеткоманды. Этот параметр неразрывно связан с частотой тактового генератора.

Современные МП могут работать с частотами десятки, сотни и даже тысячи МГц.

При тактовой частоте 10МГц один такт выполняется за 0.1 мкс. Для выполнения

одной простой операции, например арифметического сложения двух целых чисел,

взятых из памяти с пересылкой результата в память, требуется 25-30 тактов.

Таким образом, на выполнение такой операции при указанной тактовой частоте

затрачивается 2.5-3.0 мкс. Следовательно, МП может выполнить в этом случае

300-400тыс. таких операций в секунду. Для умножения целых положительных

чисел требуется 130-150 тактов, т.е. в этом случае время выполнения операции

13-15 мкс, а быстродействие исчисляется в 60-80 тыс. операций в секунду. В

некоторых случаях при выполнении сложных операций быстродействие падает

до 8-10 тыс. операций в секунду.

73. Классификация МП

По назначению различают универсальные и специализированные МП. Универсальные МПхарактеризуются универсальным набором команд. Это означает, что с помощью такого

набора команд можно осуществить преобразование информации в соответствии с любым

заданным алгоритмом. Специализированные МП предназначены для решения

определенного класса задач и, может быть, для решения одной конкретной задачи..

По числу БИС различают: однокристальные, многокристальные и секционные МП.

Однокристальные МП реализуются в виде одной БИС или СБИС. Чаще всего под МП

понимают именно однокристальный МП. Возможности таких МП ограничены предельно

допустимым числом активных элементов в кристалле и допустимым числом выводов. У

многокристального МП логическая структура разбивается на функционально законченные

части, каждая из которых реализуется в виде БИС. Такой МП обычно содержит БИС

обработки информации, БИС управления и синхронизации, БИС для связи с внешними

устройствами и др. Секционный МП представляет собой многоразрядный МП,

образованный параллельным включением микропроцессорных секций. Микропроцессорная

секция представляет собой БИС для обработки 2-, 4-, или 8-разрядных чисел и

позволяющая соединять одновременно несколько секций для увеличения разрядности

обрабатываемого слова до 16-, 24-, 32-разрядов.

74. Структура универсального 8-разрядного микропроцессора и принципы функционирования

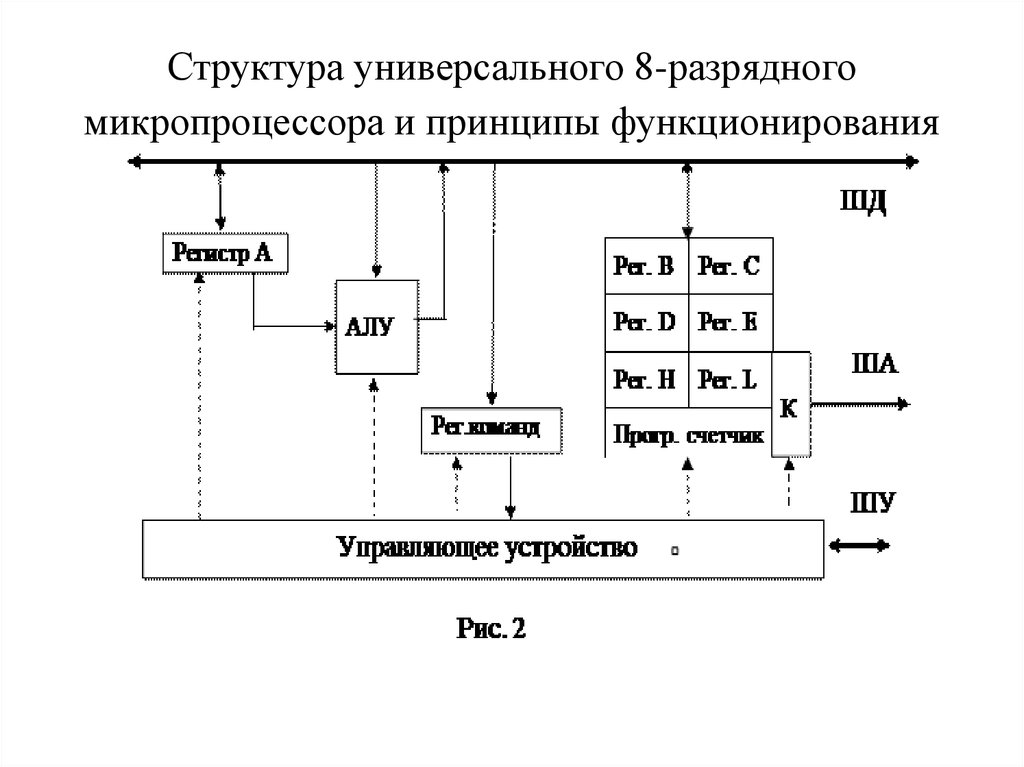

75. Комментарии к структуре МП К580ИК80 (1)

Микропроцессор К580ИК80, прототипом которого является МП Intel 8080, одиниз первых отечественных однокристальных 8-разрядных МП представляет собой

БИС, изготовленную по n-МОП технологии, содержащую около 5 тыс.

транзисторов, размещенных на кремниевом кристалле размером около 30 мм2, в

пластмассовом корпусе с 40 выводами. МП предназначен для обработки 8разрядных слов. Имеет 16-разрядную ША, что позволяет ему обращаться к

памяти с общей емкостью 64 Кбайт. Быстродействие данного микропроцессора

составляет порядка 500 тыс. операций в секунду.

В составе микропроцессора можно выделить следующие элементы:

арифметическо-логическое устройство (АЛУ), управляющее устройство (УУ),

набор регистров. Основным элементом микропроцессора является АЛУ, которое

предназначено для выполнения всех логических и арифметических операций,

предусмотренных программой. В составе АЛУ имеется 8-разрядное

суммирующее устройство и набор регистров для выполнения сдвиговых

операций.

76. Комментарии к структуре МП К580ИК80 (2)

Устройство управления является вторым наиболее сложным элементом вструктуре МП. Оно организует взаимодействие между всеми элементами

как самого микропроцессора, так и микропроцессорной системы.

Выполнение любой операции можно разбить на элементарные действия:

запись числа в регистр, считывание из регистра, сдвиг кодовой

комбинации на один разряд влево или вправо, инвертирование и т.д. Для

выполнения каждой элементарной операции требуется управляющий

сигнал. Такие элементарные операции, выполняемые в течение одного

такта сигналов синхронизации, называются микрооперациями. Как

правило, в течение одного такта могут выполняться несколько

микроопераций. Совокупность управляющих сигналов, соответствующая

набору микроопераций, выполняемых в одном такте, называют

микрокомандой, а набор микрокоманд для реализации одной операции микропрограммой.

77. Комментарии к структуре МП К580ИК80 (3)

При выполнении определенной операции в памяти управляющегоустройства отыскивается соответствующая ей микропрограмма. Ее

микрокоманды

последовательно

считываются

и

выполняют

элементарные действия, из которых складывается операция. Такой

способ реализации операций получил название микропрограммного, а

МП с устройством управления на этом принципе называется МП с

программируемой логикой. Достоинство такой организации управления

заключается в возможности гибкого изменения набора команд в МП с

помощью изменения совокупности микропрограмм. В то же время

использование принципа программируемой логики при построении

управляющих устройств приводит к снижению быстродействия МП из-за

сложности реализации микропрограммы. В некоторых случаях

формирование микрокоманд осуществляется с помощью набора

логических схем. Это значительно повышает быстродействие

микропроцессора, но при этом нет возможности корректировать или

изменять сами микрокоманды. Такие УУ называют с жесткой логикой.

78. Регистры в структуре МП

Все остальные элементы микропроцессора – регистры. Регистр команд - предназначен длязаписи и хранения команд, которые считываются из памяти и по ШД передаются в МП.

Команда содержит код операции, которую должен выполнить МП.

Регистрами общего назначения (РОН) называют регистры А, В, С, D, Е, Н, L, которые

образуют сверхоперативную память микропроцессора. У данного МП все регистры общего

назначения 8-разрядные.

Особое место среди регистров общего назначения занимает регистр А, который является

аккумулятором. Аккумулятор - это регистр, в который заносится одно из чисел, которое

должно быть обработано АЛУ. В аккумулятор записывается результат выполнения любой

операции. Так, например, если необходимо произвести сложение двух чисел, то одно из

чисел записывается в аккумулятор, а другое в один из регистров общего назначения. После

выполнения операции сложения результат будет записан в аккумулятор. Программный

счетчик или счетчик команд - этот регистр предназначен для хранения адреса (номера)

следующей команды, которая должна быть извлечена из памяти. Перед началом работы в

счетчик команд заносится адрес первой команды программы.

79. Принцип программного управления

Все МП работают в соответствии с принципами программного управления. Суть этихпринципов заключается в следующем:

1.Вся информация для МП представляется в двоичном коде.

2.Алгоритм решения любой задачи представляется в виде последовательности команд

(программы).

3.Команда содержит наименование операции и определяет объект, над которым

выполняется заданное действие.

4.Программа и данные располагаются в памяти, состоящей из ячеек, каждая из

которых имеет свой номер (адрес) и служит для хранения одной команды или числа.

5. Выполнение программы сводится к выборке и выполнению составляющих ее

команд.

Электроника

Электроника