Похожие презентации:

Комбинационные логические устройства компьютера. Арифметико-логические устройства (АЛУ)

1.

УЧЕБНАЯ ДИСЦИПЛИНА«АРХИТЕКТУРА АППАРАТНЫХ СРЕДСТВ»

ПРЕПОДАВАТЕЛЬ:

ИГНАТЬЕВ

ЕВГЕНИЙ АЛЕКСАНДРОВИЧ

1

2.

РАЗДЕЛ 2. Архитектура и принципы работы основныхлогических блоков вычислительных систем

Тема 2.2 Логические элементы, узлы, блоки и устройства

компьютера

Лекция 9. Комбинационные логические устройства.

Арифметико-логические устройства (АЛУ)

Учебные вопросы:

1. Комбинационные логические устройства: дешифраторы,

шифраторы,

мультиплексоры,

демультиплексоры,

сумматоры

2. Арифметико-логические устройства (АЛУ): применение,

обобщенная структурная схема.

2

3.

Вопрос 1.Комбинационные логические устройства

К комбинационным устройствам относятся функциональные

узлы, в которых отсутствуют элементы памяти.

Состояние

комбинационного

узла

однозначно

определяется комбинацией входных сигналов в данный

момент и не зависит от предыдущего состояния.

К таким узлам относятся шифраторы, дешифраторы,

сумматоры,

мультиплексоры,

демультиплексоры,

компараторы, преобразователи кодов и другие.

3

4.

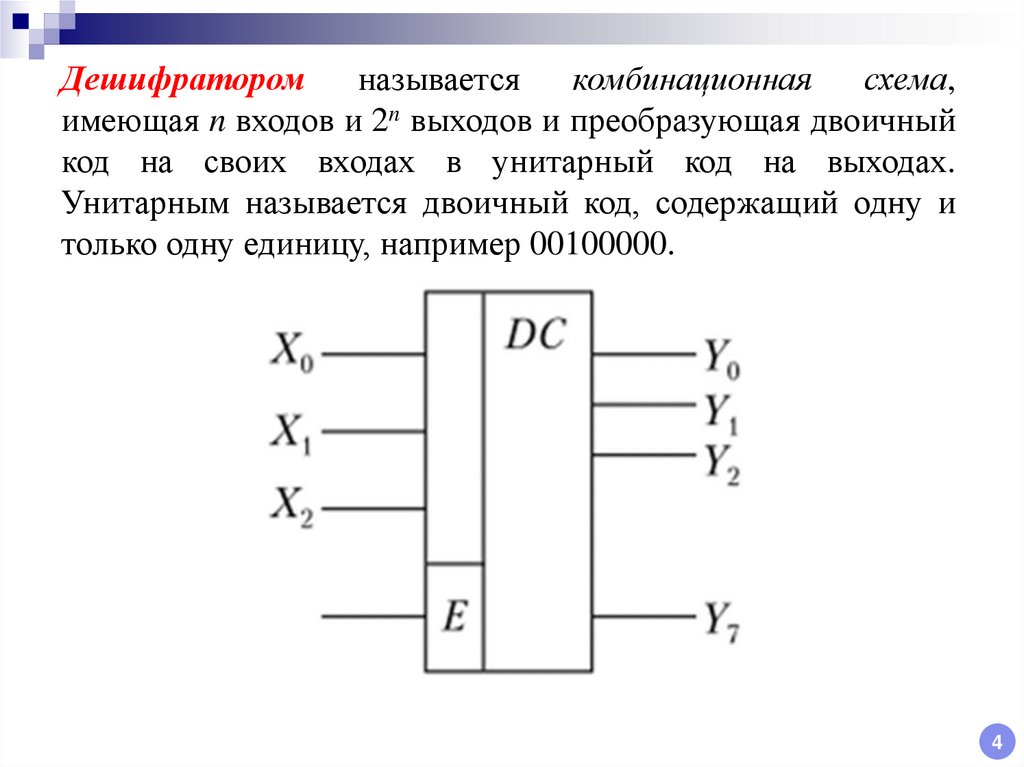

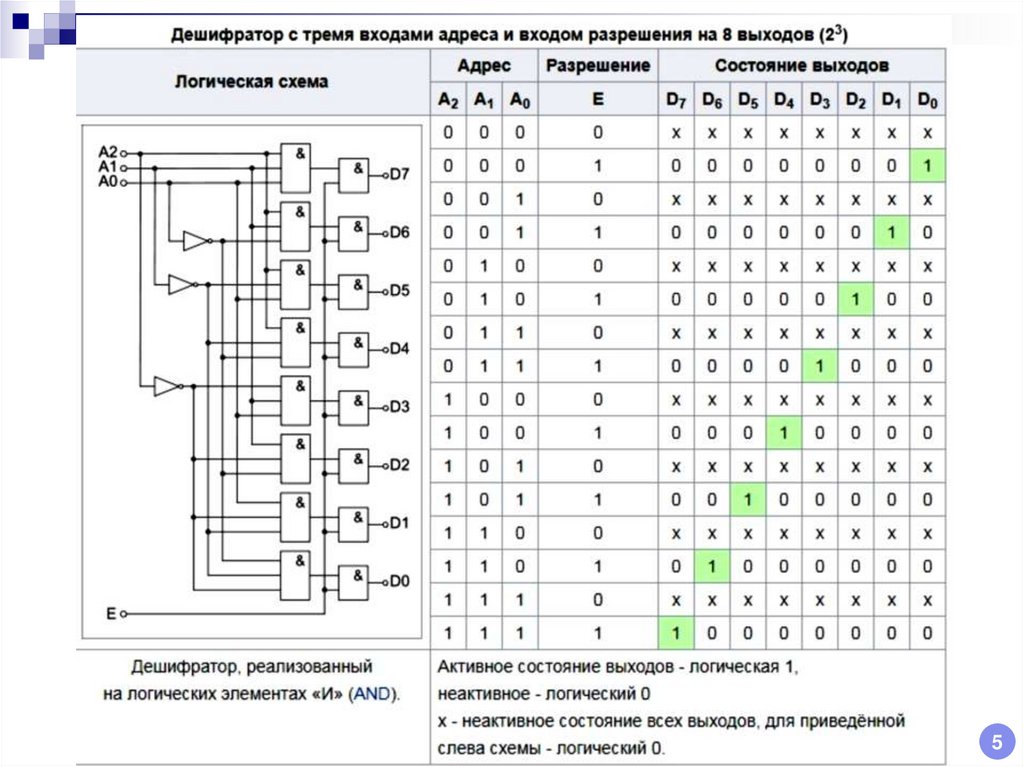

Дешифраторомназывается

комбинационная

схема,

имеющая n входов и 2n выходов и преобразующая двоичный

код на своих входах в унитарный код на выходах.

Унитарным называется двоичный код, содержащий одну и

только одну единицу, например 00100000.

4

5.

56.

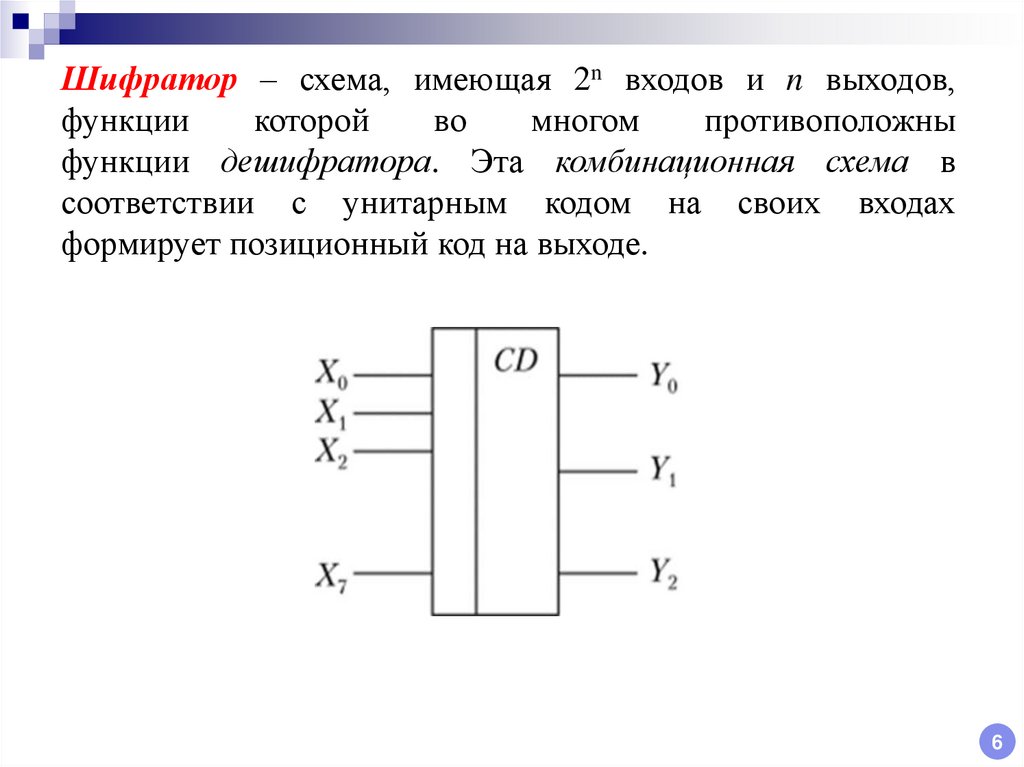

Шифратор – схема, имеющая 2n входов и n выходов,функции

которой

во

многом

противоположны

функции дешифратора. Эта комбинационная схема в

соответствии с унитарным кодом на своих входах

формирует позиционный код на выходе.

6

7.

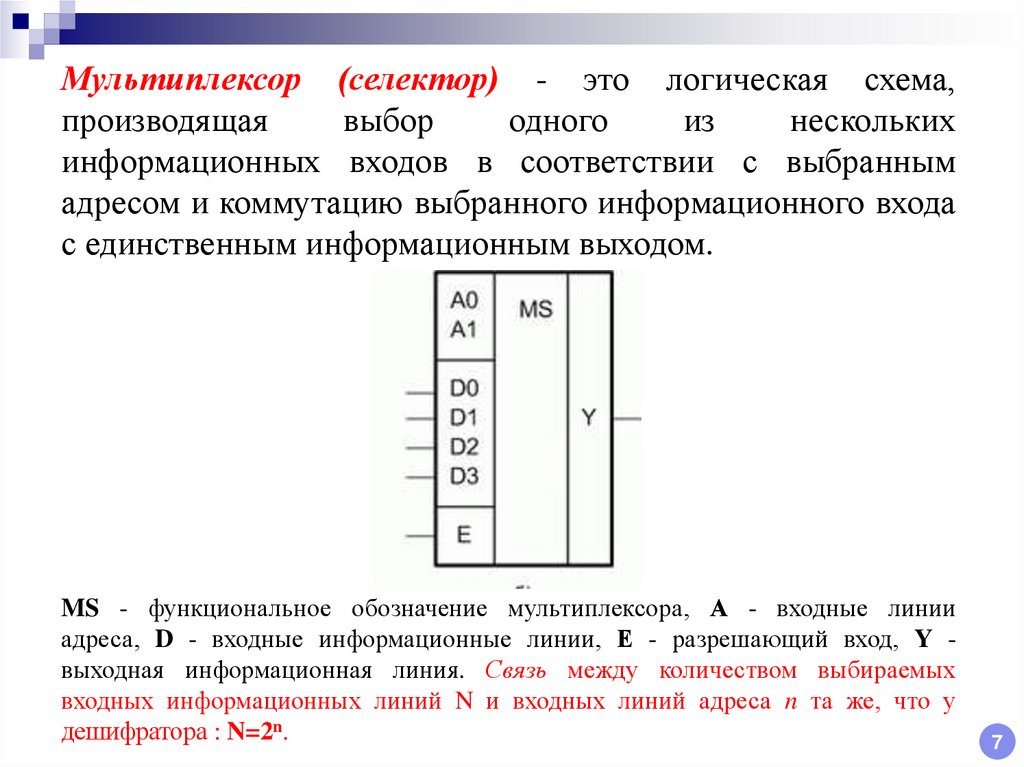

Мультиплексор (селектор) - это логическая схема,производящая

выбор

одного

из

нескольких

информационных входов в соответствии с выбранным

адресом и коммутацию выбранного информационного входа

с единственным информационным выходом.

MS - функциональное обозначение мультиплексора, А - входные линии

адреса, D - входные информационные линии, Е - разрешающий вход, Y выходная информационная линия. Связь между количеством выбираемых

входных информационных линий N и входных линий адреса n та же, что у

дешифратора : N=2n.

7

8.

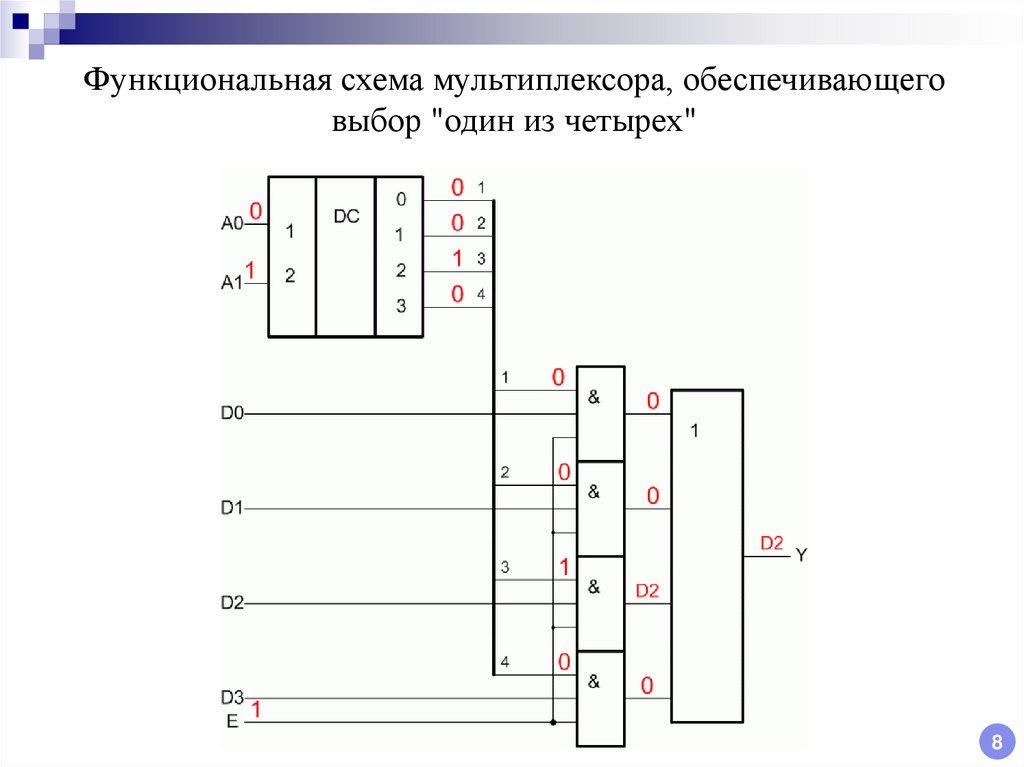

Функциональная схема мультиплексора, обеспечивающеговыбор "один из четырех"

8

9.

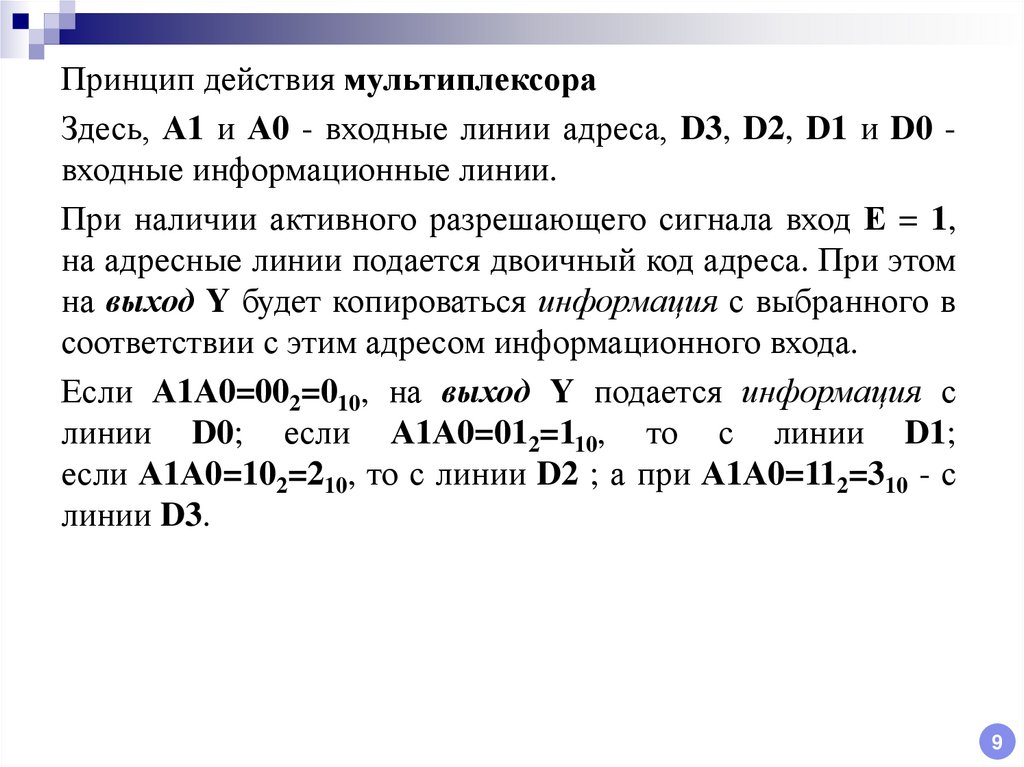

Принцип действия мультиплексораЗдесь, А1 и А0 - входные линии адреса, D3, D2, D1 и D0 входные информационные линии.

При наличии активного разрешающего сигнала вход Е = 1,

на адресные линии подается двоичный код адреса. При этом

на выход Y будет копироваться информация с выбранного в

соответствии с этим адресом информационного входа.

Если А1А0=002=010, на выход Y подается информация с

линии D0; если А1А0=012=110, то с линии D1;

если А1А0=102=210, то с линии D2 ; а при А1А0=112=310 - с

линии D3.

9

10.

Таблица истинности данного мультиплексора10

11.

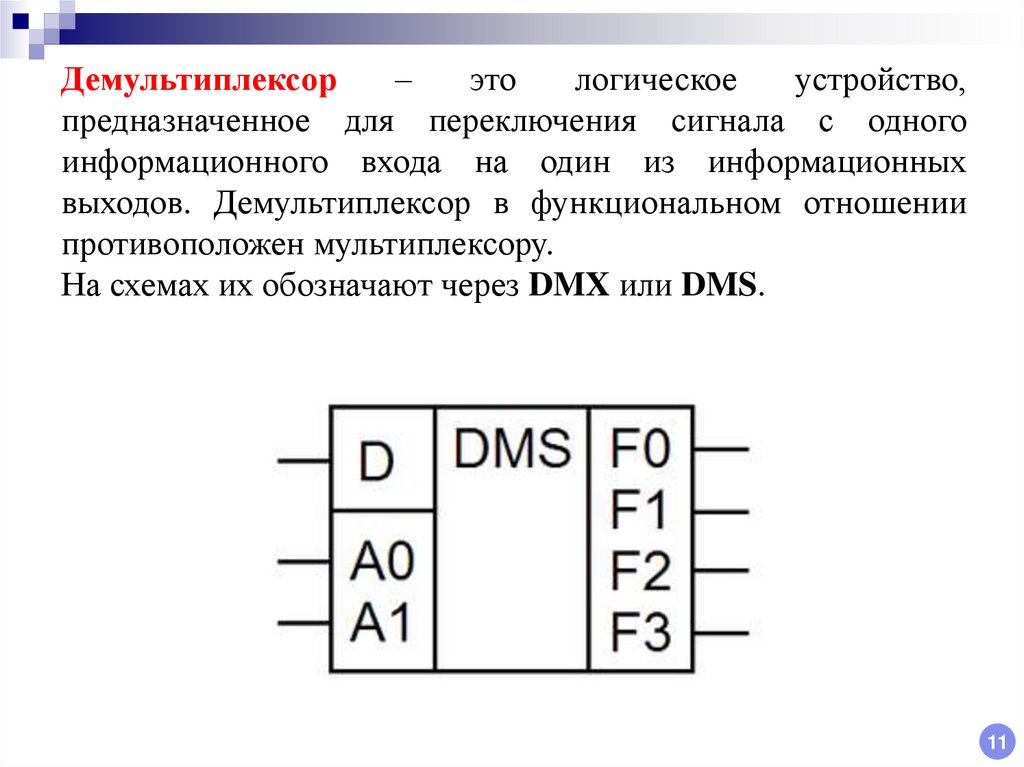

Демультиплексор–

это

логическое

устройство,

предназначенное для переключения сигнала с одного

информационного входа на один из информационных

выходов. Демультиплексор в функциональном отношении

противоположен мультиплексору.

На схемах их обозначают через DMX или DMS.

11

12.

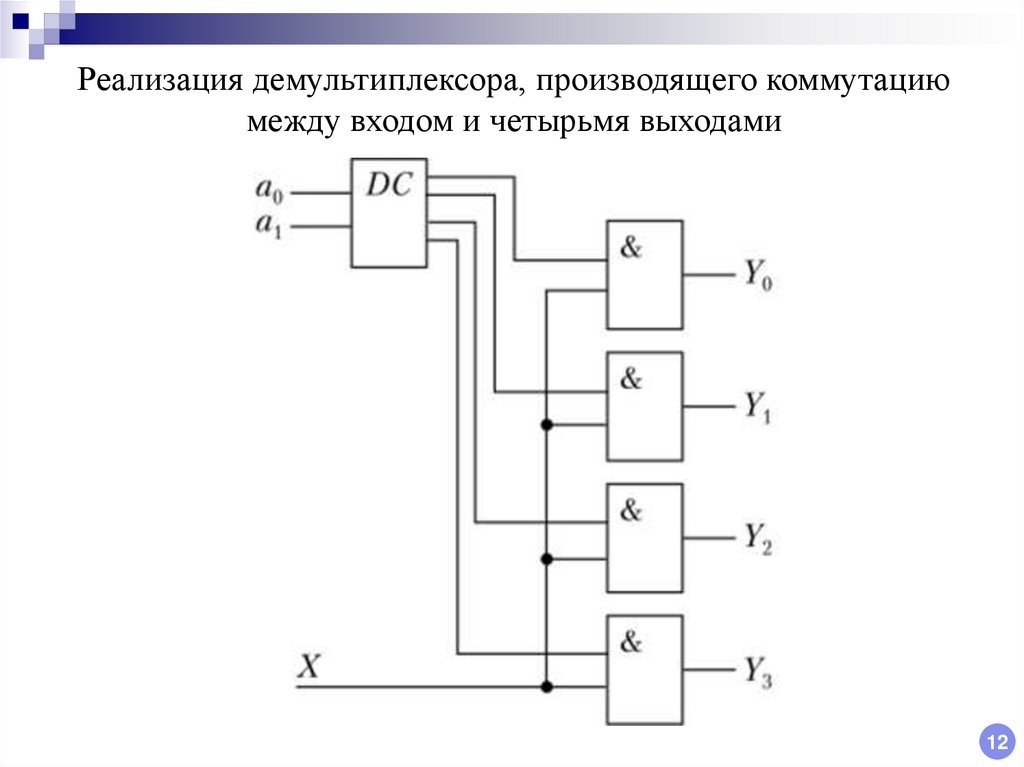

Реализация демультиплексора, производящего коммутациюмежду входом и четырьмя выходами

12

13.

Сумматор – логический операционный узел, выполняющийарифметическое сложение кодов двух чисел.

Сумматоры классифицируют по различным признакам.

В зависимости от системы счисления различают:

двоичные;

двоично-десятичные;

десятичные;

прочие (например, амплитудные).

По количеству одновременно обрабатываемых разрядов

складываемых чисел:

одноразрядные,

многоразрядные.

13

14.

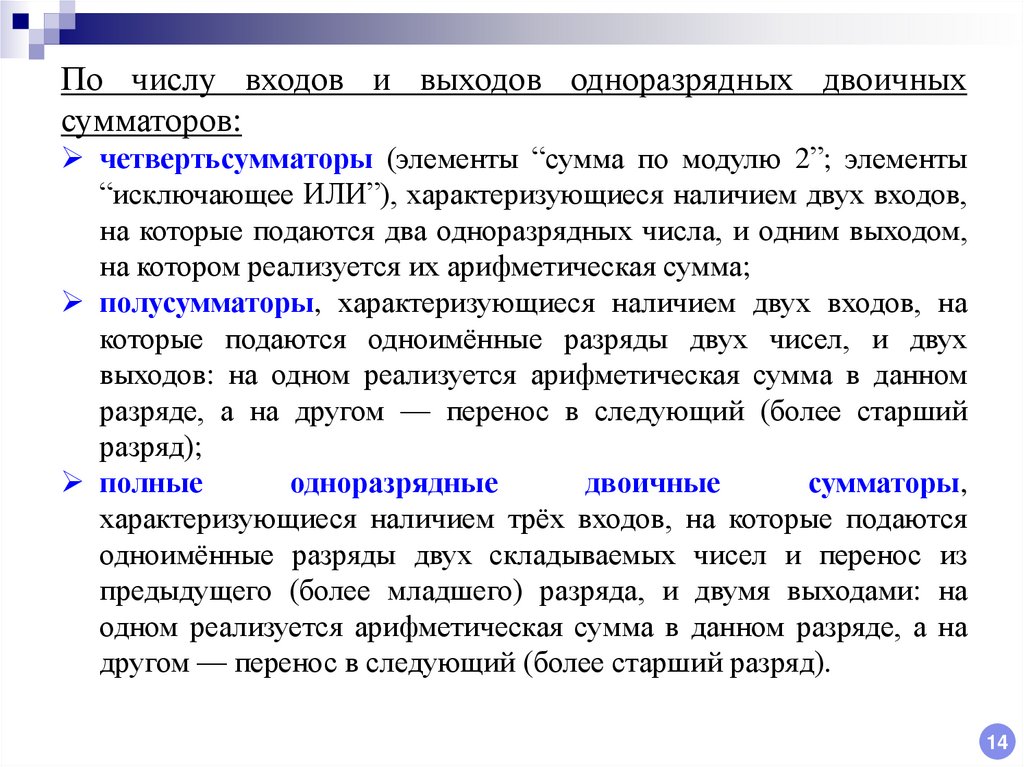

По числу входов и выходов одноразрядных двоичныхсумматоров:

четвертьсумматоры (элементы “сумма по модулю 2”; элементы

“исключающее ИЛИ”), характеризующиеся наличием двух входов,

на которые подаются два одноразрядных числа, и одним выходом,

на котором реализуется их арифметическая сумма;

полусумматоры, характеризующиеся наличием двух входов, на

которые подаются одноимённые разряды двух чисел, и двух

выходов: на одном реализуется арифметическая сумма в данном

разряде, а на другом — перенос в следующий (более старший

разряд);

полные

одноразрядные

двоичные

сумматоры,

характеризующиеся наличием трёх входов, на которые подаются

одноимённые разряды двух складываемых чисел и перенос из

предыдущего (более младшего) разряда, и двумя выходами: на

одном реализуется арифметическая сумма в данном разряде, а на

другом — перенос в следующий (более старший разряд).

14

15.

По способу представления и обработки складываемых чиселмногоразрядные сумматоры подразделяются на:

последовательные, в которых обработка чисел ведётся

поочерёдно, разряд за разрядом на одном и том же

оборудовании;

параллельные, в которых слагаемые складываются

одновременно по всем разрядам, и для каждого разряда

имеется своё оборудование.

По способу организации межразрядных переносов

параллельные сумматоры, реализующие структурные

методы, делят на сумматоры:

с последовательным переносом;

с параллельным переносом;

с групповой структурой;

со специальной организацией цепей переноса.

15

16.

ЧетвертьсумматорПростейшим двоичным суммирующим элементом является

четвертьсумматор.

Наиболее известны для данной схемы названия: элемент

“сумма по модулю 2” и элемент “исключающее ИЛИ”. Схема

имеет два входа а и b для двух слагаемых и один выход S для

суммы. Уравнение имеет вид:

16

17.

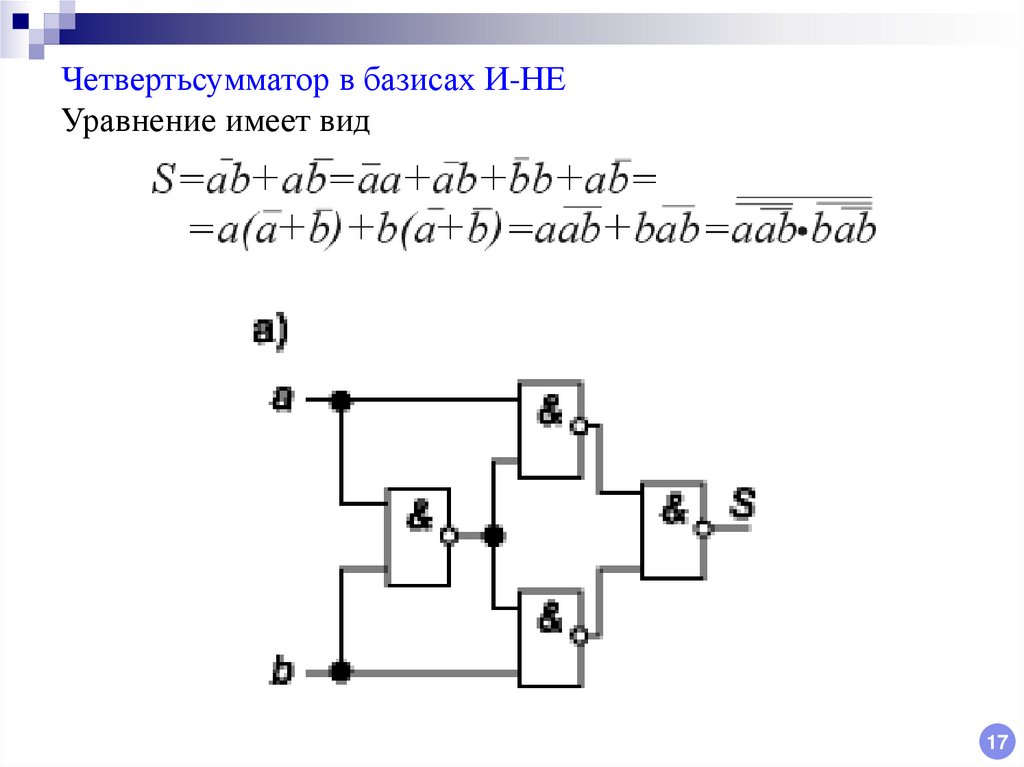

Четвертьсумматор в базисах И-НЕУравнение имеет вид

17

18.

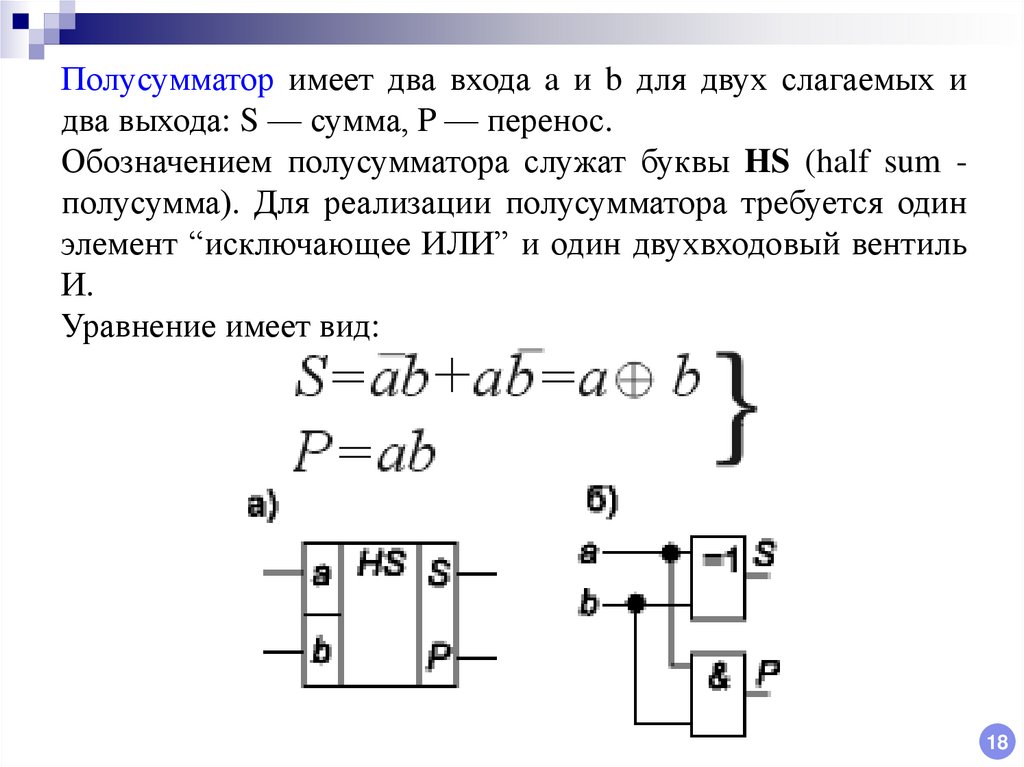

Полусумматор имеет два входа a и b для двух слагаемых идва выхода: S — сумма, P — перенос.

Обозначением полусумматора служат буквы HS (half sum полусумма). Для реализации полусумматора требуется один

элемент “исключающее ИЛИ” и один двухвходовый вентиль

И.

Уравнение имеет вид:

18

19.

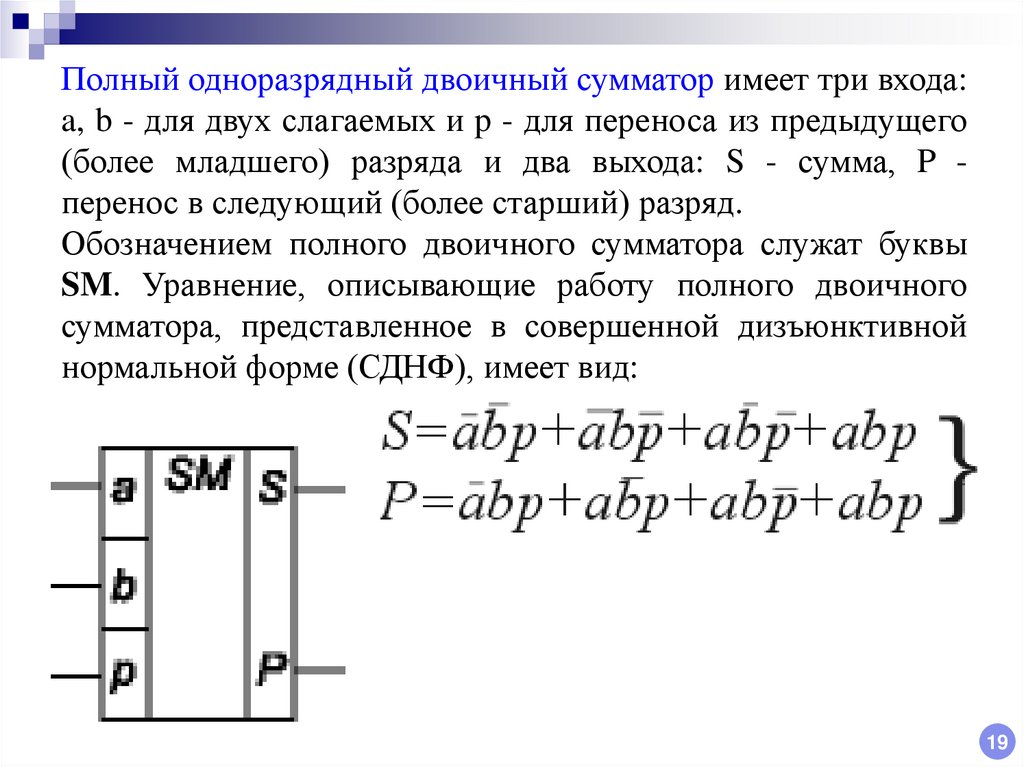

Полный одноразрядный двоичный сумматор имеет три входа:a, b - для двух слагаемых и p - для переноса из предыдущего

(более младшего) разряда и два выхода: S - сумма, P перенос в следующий (более старший) разряд.

Обозначением полного двоичного сумматора служат буквы

SM. Уравнение, описывающие работу полного двоичного

сумматора, представленное в совершенной дизъюнктивной

нормальной форме (СДНФ), имеет вид:

19

20.

Вопрос 2.Арифметико-логические устройства (АЛУ)

Классическая ЭВМ состоит из трех основных устройств:

арифметико-логического устройства;

устройства управления;

запоминающего устройства.

В современных ЭВМ арифметико-логическое устройство не

является самостоятельным схемотехническим блоком. Оно

входит в состав микропроцессора, на котором строится

компьютер.

Арифметико-логические устройства (АЛУ) – являются

узлом ЭВМ, который выполняет арифметические и

логические операции над данными, обрабатываемыми ЭВМ.

20

21.

АЛУ можно классифицировать по ряду признаков.Классификация по способу представления данных:

с фиксированной запятой;

с плавающей запятой.

Классификация по способу действия над операндами:

последовательные

АЛУ,

где

каждая

операция

выполняется последовательно над каждым разрядом;

параллельные АЛУ, операция выполняется над всеми

разрядами данных одновременно;

последовательно - параллельные АЛУ, где слово данных

делится на слоги, обработка данных ведется параллельно

над разрядами слога и последовательно над слогами.

Классификация по использованию систем счисления:

двоичная;

двоично - десятичная;

восьмеричная;

шестнадцатеричная и т.д.

21

22.

Классификация по характеру использования элементов иузлов:

блочные - для выполнения отдельных арифметических

операций в структуру АЛУ вводят специальные блоки,

что позволяет процесс обработки информации вести

параллельно;

конвейерные - в конвейерных АЛУ операция разбивается

на последовательность микроопераций, выполняемых за

одинаковые промежутки времени (такты) на разных

ступенях конвейера, что позволяет выполнять операцию

над потоком операндов каждый такт;

многофункциональные - это универсальные АЛУ,

выполняющие множество операций в одном устройстве.

В таких АЛУ требуется настройка на выполнение данной

операции при помощи кода операции.

22

23.

Классификация по временным характеристикам.синхронные - в синхронных АЛУ каждая операция

выполняется за один такт.

асинхронные - не тактируемые АЛУ, обеспечивающие

высокое быстродействие, так как выполняются на

комбинационных схемах.

Классификация по структуре устройства управления:

АЛУ с жесткой логикой устройства управления;

АЛУ с микропрограммным управлением.

23

24.

Основные функции АЛУСовременные АЛУ выполняют:

функции двоичной арифметики для данных в формате с

фиксированной точкой;

функции двоичной арифметики для данных в формате с

плавающей точкой;

функции

арифметики

двоично-десятичного

представления данных;

логические

операций

(в

том

числе

сдвиги

арифметические и логические);

операции пересылки данных;

работу с символьными данными;

работу с графическими данными.

24

25.

Основные характеристики АЛУОсновные характеристики АЛУ:

Количественные характеристики:

скорость выполнения операций;

Vср = N(T)/T

Vср - средняя скорость выполнения операций

N(T) - количество операций, выполненных за отрезок

времени Т.

время выполнения одной операции;

Tср = 1/Vср

точность представления данных;

количество выполняемых операций.

Качественные характеристики:

структурные особенности АЛУ;

форматы представления данных (с фиксированной или

плавающей точкой);

способы кодирования данных.

25

26.

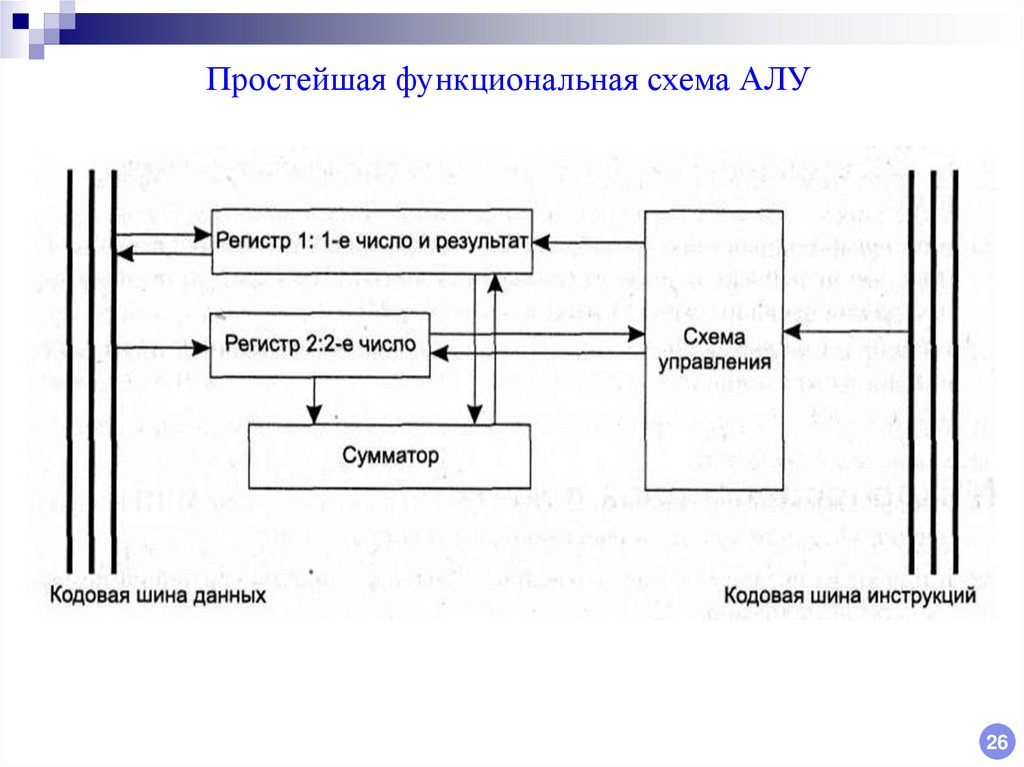

Простейшая функциональная схема АЛУ26

27.

Функционально в простейшем варианте АЛУ состоитиз:

двух регистров – быстродействующие ячейки памяти

различной длины: регистр 1 имеет разрядность двойного

слова, а регистр 2 - разрядность слова;

сумматора – вычислительная схема, выполняющая

процедуру сложения поступающих на ее вход двоичных

кодов (сумматор имеет разрядность двойного машинного

слова);

схем управления (местного устройства управления) –

они

принимают по кодовым шинам инструкций

управляющие сигналы от устройства управления и

преобразуют их в сигналы для управления работой

регистров и сумматора АЛУ.

27

28.

АЛУ выполняет арифметические операции «+», «–», «*»и «÷» только над двоичной информацией с запятой,

фиксированной после последнего разряда, то есть только

над целыми двоичными числами.

Выполнение операций над двоичными числами с

плавающей запятой и над двоично-кодированными

десятичными числами осуществляется с привлечением

математического сопроцессора или по специально

составленным программам.

28

Электроника

Электроника