Похожие презентации:

Архитектура вычислительных систем. (Лекция 4)

1. Архитектура вычислительных систем. Лекция 4

Компьютеры с общей памятьюКэш-когерентность

NUMA и ccNUMA архитектуры. Примеры.

Особенности архитектуры современных

микропроцессоров, направленные на повышение

производительности:

- ILP (суперскалярность, VLIW)

- TLP и многоядерность

- Реализация SIMD-вычислений

- Концепция RISC

- Спецпроцессоры. Процессоры Cell

2. Компьютеры с общей памятью (1)

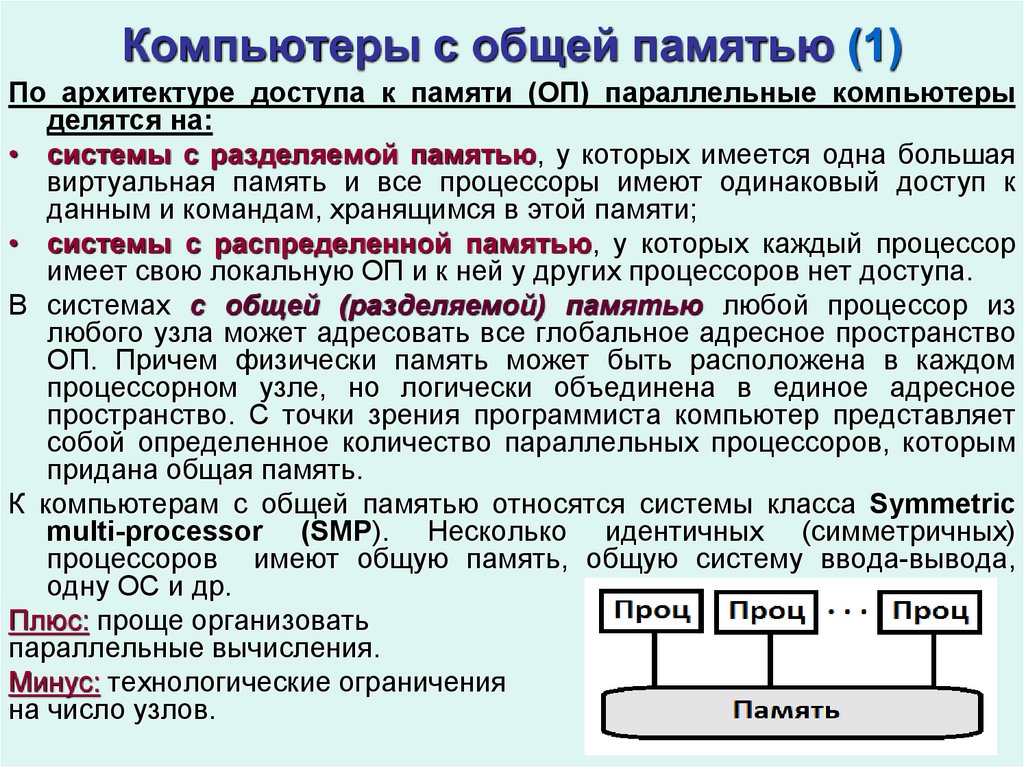

По архитектуре доступа к памяти (ОП) параллельные компьютерыделятся на:

• системы с разделяемой памятью, у которых имеется одна большая

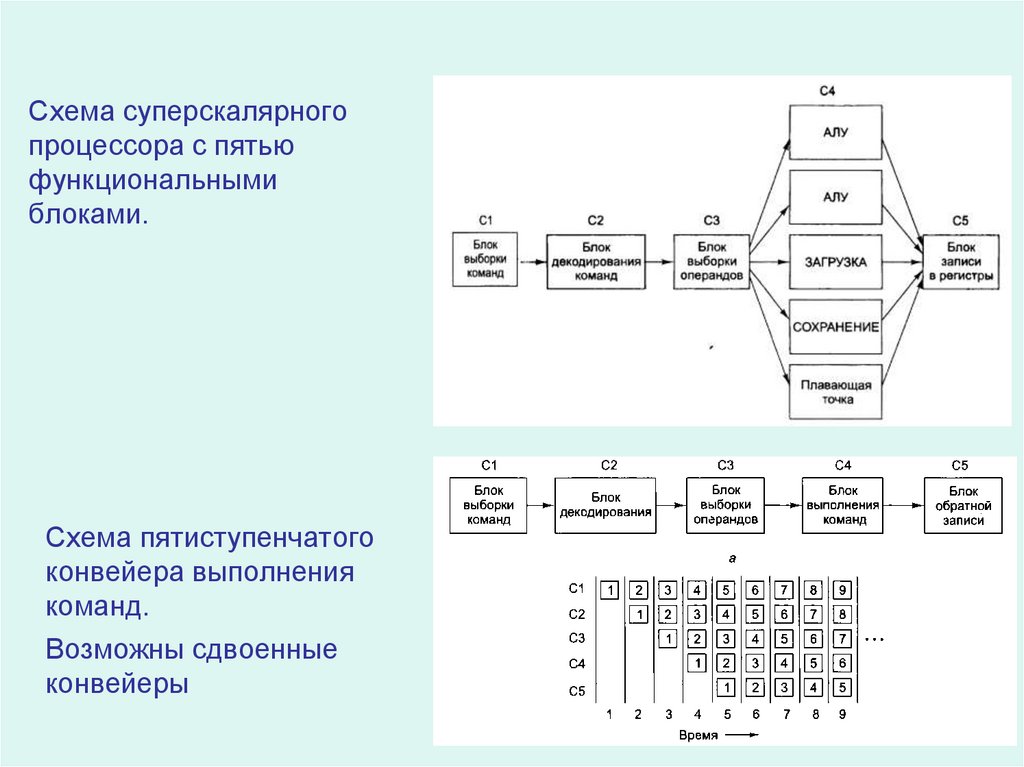

виртуальная память и все процессоры имеют одинаковый доступ к

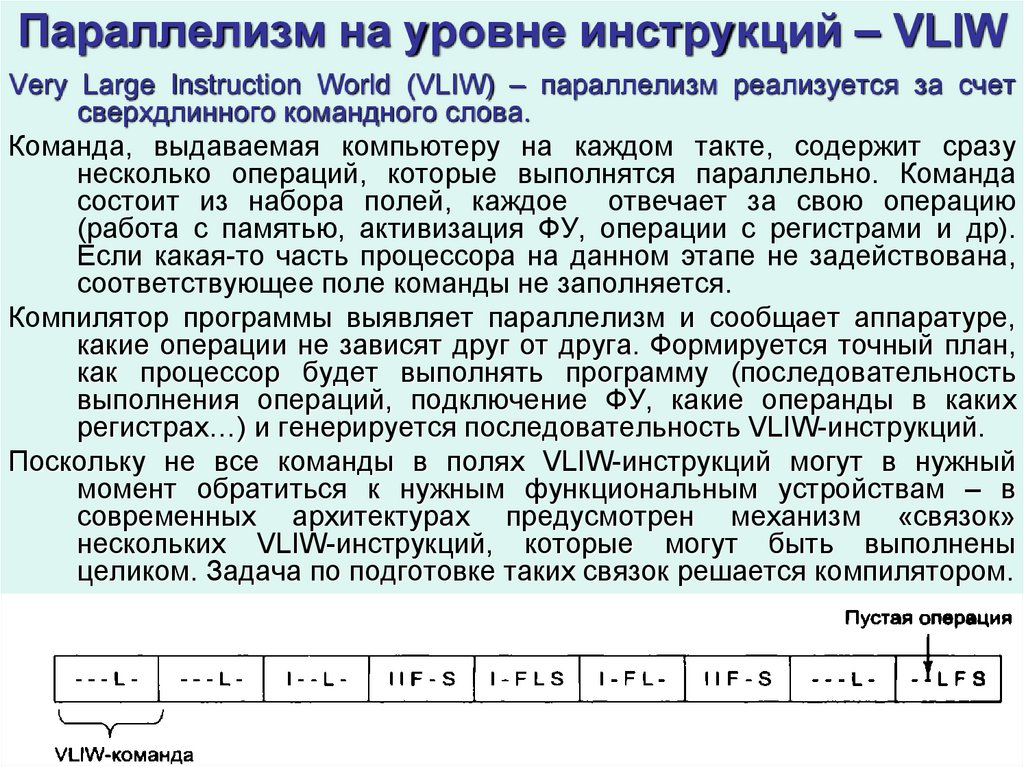

данным и командам, хранящимся в этой памяти;

• системы с распределенной памятью, у которых каждый процессор

имеет свою локальную ОП и к ней у других процессоров нет доступа.

В системах с общей (разделяемой) памятью любой процессор из

любого узла может адресовать все глобальное адресное пространство

ОП. Причем физически память может быть расположена в каждом

процессорном узле, но логически объединена в единое адресное

пространство. С точки зрения программиста компьютер представляет

собой определенное количество параллельных процессоров, которым

придана общая память.

К компьютерам с общей памятью относятся системы класса Symmetric

multi-processor (SMP). Несколько идентичных (симметричных)

процессоров имеют общую память, общую систему ввода-вывода,

одну ОС и др.

Плюс: проще организовать

параллельные вычисления.

Минус: технологические ограничения

на число узлов.

3. Компьютеры с общей памятью (2)

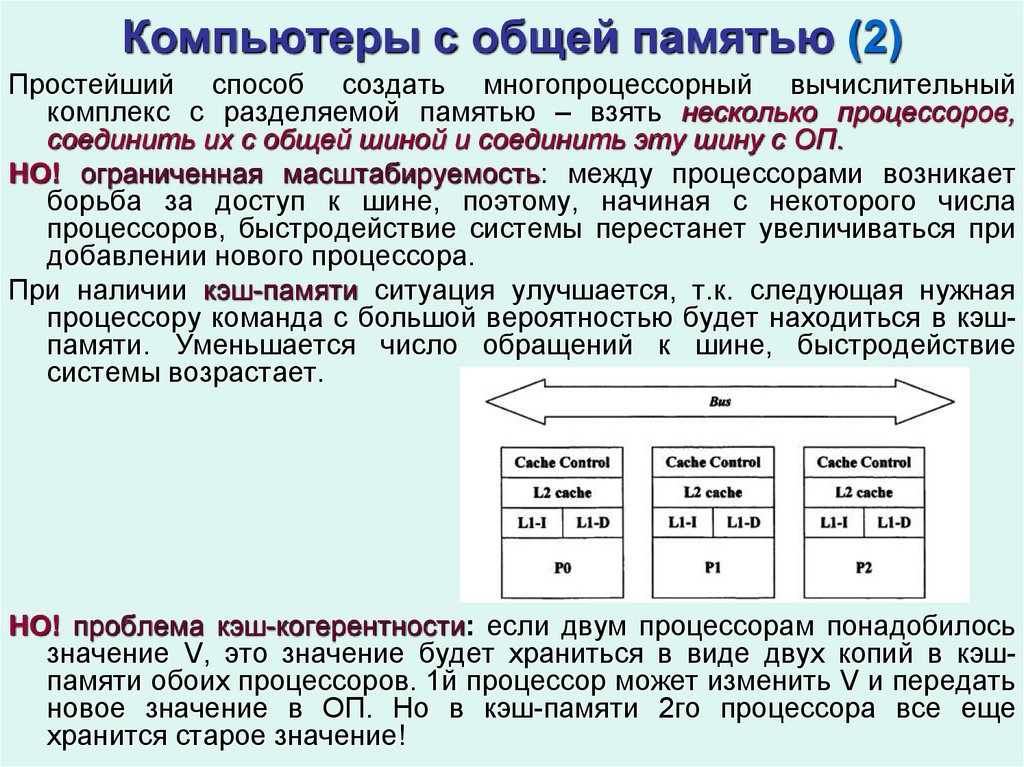

Простейший способ создать многопроцессорный вычислительныйкомплекс с разделяемой памятью – взять несколько процессоров,

соединить их с общей шиной и соединить эту шину с ОП.

НО! ограниченная масштабируемость: между процессорами возникает

борьба за доступ к шине, поэтому, начиная с некоторого числа

процессоров, быстродействие системы перестанет увеличиваться при

добавлении нового процессора.

При наличии кэш-памяти ситуация улучшается, т.к. следующая нужная

процессору команда с большой вероятностью будет находиться в кэшпамяти. Уменьшается число обращений к шине, быстродействие

системы возрастает.

НО! проблема кэш-когерентности: если двум процессорам понадобилось

значение V, это значение будет храниться в виде двух копий в кэшпамяти обоих процессоров. 1й процессор может изменить V и передать

новое значение в ОП. Но в кэш-памяти 2го процессора все еще

хранится старое значение!

4. Компьютеры с общей памятью (3)

Таким образом, необходимо обеспечить своевременное обновлениеданных в кэш-памяти всех процессоров компьютера.

Механизм когерентности является критичным для эффективной

параллельной работы SMP-узла и должен иметь малое время задержки.

Требование малых задержек когерентных связей приводит к

архитектуре с одной объединительной платой, что физически

ограничивает возможное число подсоединенных процессоров и плат

памяти.

Поэтому самые крупные SMP-системы обычно содержат максимум 32

процессора на узел. Для дальнейшего увеличения числа процессоров в

узле приходится применять более медленную программную

реализацию, что сказывается на производительности.

Альтернативный

вариант

реализации

разделяемой

памяти,

позволяющий увеличить число вычислительных узлов – разделяемая

память с дискретными модулями памяти. Физическая память

состоит из нескольких модулей, хотя виртуальное адресное

пространство общее. Запросы от процессора к памяти направляет

переключатель. Если процессоры обращаются к разным модулям

памяти,

запросы

обрабатываются

параллельно,

поэтому

быстродействие возрастает.

Главное достоинство SMP-узлов и других систем с разделяемой

памятью – возможность оперировать единым адресным пространством,

что очень удобно для разработчиков приложений.

5. Кэш-когерентность (1)

Поскольку в SMP-узлах процессоры одновременно работаютс данными, хранящимися в единой ОП узла, в SMPархитектурах

обязателен

механизм

поддержки

когерентности данных.

Когерентность данных означает, что в любой момент

времени для каждого элемента данных во всей памяти

узла существует только одно его значение, несмотря на

то, что одновременно могут существовать несколько

копий элемента данных, расположенных в разных видах

памяти и обрабатываемых разными процессорами.

1

2

Если устройство 1 в верхней

части имеет копию блока памяти

из предыдущего чтения, а

устройство 2 изменяет этот блок

памяти, копия данных в кэше 1го

устройства становится

устаревшей

6. Кэш-когерентность (2)

Механизм когерентности должен следить, чтобы операции с одним и темже элементом данных выполнялись на разных процессорах

последовательно, удаляя устаревшие копии.

В современных SMP-архитектурах когерентность реализуется аппаратно.

• Когерентность с использованием справочника (directory). Информация о

состоянии блока физической памяти содержится только в одном месте,

называемом справочником (физически справочник может быть

распределен по узлам системы).

• Перехват (snarfing). Когда из какого-либо одного кэша данные

переписываются в оперативную память, контроллеры остальных

получают сигнал об этом изменении ("перехватывают" информацию об

изменении данных) и, если необходимо, изменяют соответствующие

данные в своих кэшах.

• Когерентность с использованием отслеживания (snooping). Каждый кэш,

который содержит копию данных некоторого блока физической памяти,

имеет также соответствующую копию служебной информации о его

состоянии. Централизованная система записей отсутствует. Обычно

кэши расположены на общей (разделяемой) шине и контроллеры всех

кэшей наблюдают за шиной (просматривают её) для определения того,

не содержат ли они копию соответствующего блока.

7. Кэш-когерентность (3): согласование памяти

Строгая согласованность вычислений означает: операция чтениядолжна возвращать значение переменной, соответствующее последней

по времени операции записи.

В однопроцессорных системах или в системах с одним модулем

обеспечение строго согласованности вполне естественно.

В распределенных системах ситуация осложняется отсутствием

«единого времени», которое позволило бы полностью упорядочить

действия процессоров, но неминуемо привело бы к снижению

производительности.

Поэтому необходимы модели с более слабыми требованиями к

согласованности.

Последовательная согласованность.

• Модель предложена Лэмпортом в 1979.

• Все процессы наблюдают одну и ту же последовательность обращений

к памяти.

• Практически это означает, что один процессор, выполняющий запись,

ожидает от других процессоров подтверждения модификации или

объявления модифицируемых данных несостоятельными.

• Это обеспечивает единый порядок записей, видимый всеми

процессорами.

• Последовательная согласованность не гарантирует, что операция

чтения возвратит значение, записанное чуть раньше другим процессом.

8. Кэш-когерентность (4): согласование памяти

Пусть имеется вычислительная система с параллельными процессорамиП1, П2,П3, П4. с общей памятью. Каждый процессор выполняет

операции записи (w – write) и чтения (r – read) относительно ячейки

памяти с адресом х.

Пример последовательной согласованности (по горизонтали - время)

П1 w(x) 2

w(x) 1

П2

r(x) 2

r(x) 1

П3

r(x) 2

r(x) 1

Пример нарушения последовательной согласованности

П1 w(x) 1

П2

w(x) 2

П3

r(x) 1

r(x) 2

П4

r(x) 2

r(x) 1

Когерентность (согласованность) кэш-памяти устанавливает порядок, в

котором процессы модифицируют одну и ту же переменную, в то время

как операции записи в разные переменные могут осуществляться

параллельно.

Таким образом, когерентность – последовательная согласованность

локальной области памяти. Эта модель строго слабее модели

последовательной согласованности.

9. Архитектура NUMA (ссNUMA)

Попытка объединения достоинств компьютеров с общей ираспределенной памятью реализована в архитектурах организации

памяти non uniform memory access – технологиях NUMA и ccNUMA

(cache-coherent NUMA).

Идея в том, чтобы создать механизм, позволяющий всю совокупную,

(вообще говоря, неоднородную, физическую память компьютера

рассматривать (виртуально) как единую адресуемую память.

При этом сохраняется преимущество работы с единым адресным

пространством и одновременно ослабляются ограничения на число

параллельных узлов. Таким образом, архитектуры NUMA и ccNUMA

представляют нечто среднее между SMP и MPP. В таких системах

память физически распределена, но логически общедоступна.

NUMA-системы состоят из однородных базовых модулей (плат);

каждый из модулей имеет небольшое число процессоров и блок памяти.

Модули объединены с помощью высокоскоростного коммутатора.

Поддерживается

единое

адресное

пространство,

аппаратно

поддерживается доступ к удаленной памяти (к памяти других модулей).

Время доступа к памяти определяется её физическом расположением:

доступ к локальной памяти процессора в несколько раз быстрее, чем к

удаленной. Если поддерживается когерентность кэшей во всей системе

(обычно это так), говорят об архитектуре cc-NUMA (cache-coherent

NUMA). Для поддержки кэш-когерентности используются специальные

аппаратные решения.

10. NUMA: компьютер Cm*

Система Cm* (конец 70х) – первый NUMAкомпьютер. Набор кластеров, соединенных

между собой через межкластерную шину.

Каждый

кластер

объединяет

процессор,

контроллер памяти, модуль памяти, плюс

вспомогательные

устройства,

соединенные

между собой посредством локальной шины.

Когда процессору нужно выполнить операции

чтения или записи, он посылает запрос с

адресом

своему

контроллеру

памяти.

Контроллер анализирует старшие разряды

адреса и определяет, в каком модуле хранятся

нужные данные. Если адрес локальный – запрос

выставляется на локальную шину, запрос для

удаленного

кластера

отправляется

через

межкластерную шину.

Программа, хранящаяся в одном модуле памяти,

может

выполняться

любым

процессором

системы. Различие заключается лишь в скорости

выполнения. Локальные ссылки отрабатываются

намного быстрее, чем удаленные (разрыв до

700%). Поэтому процессор того кластера, где

хранится программа, выполнит ее на порядок

быстрее, чем другие.

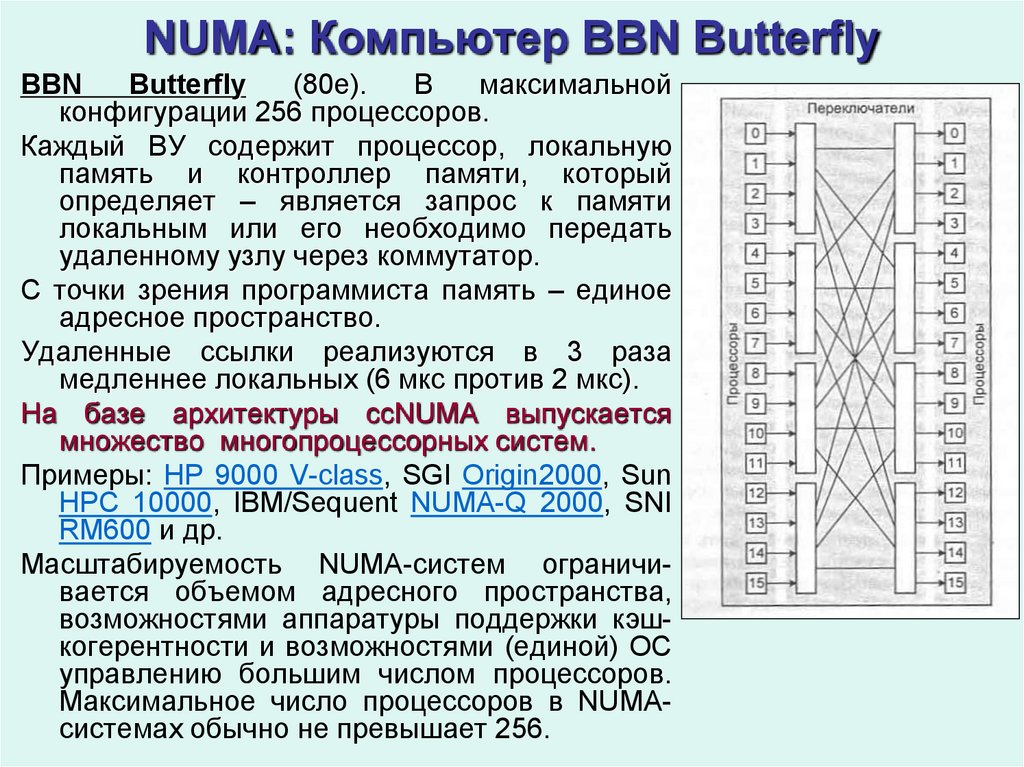

11. NUMA: Компьютер BBN Butterfly

BBNButterfly

(80е).

В

максимальной

конфигурации 256 процессоров.

Каждый ВУ содержит процессор, локальную

память и контроллер памяти, который

определяет – является запрос к памяти

локальным или его необходимо передать

удаленному узлу через коммутатор.

С точки зрения программиста память – единое

адресное пространство.

Удаленные ссылки реализуются в 3 раза

медленнее локальных (6 мкс против 2 мкс).

На базе архитектуры ссNUMA выпускается

множество многопроцессорных систем.

Примеры: HP 9000 V-class, SGI Origin2000, Sun

HPC 10000, IBM/Sequent NUMA-Q 2000, SNI

RM600 и др.

Масштабируемость NUMA-систем ограничивается объемом адресного пространства,

возможностями аппаратуры поддержки кэшкогерентности и возможностями (единой) ОС

управлению большим числом процессоров.

Максимальное число процессоров в NUMAсистемах обычно не превышает 256.

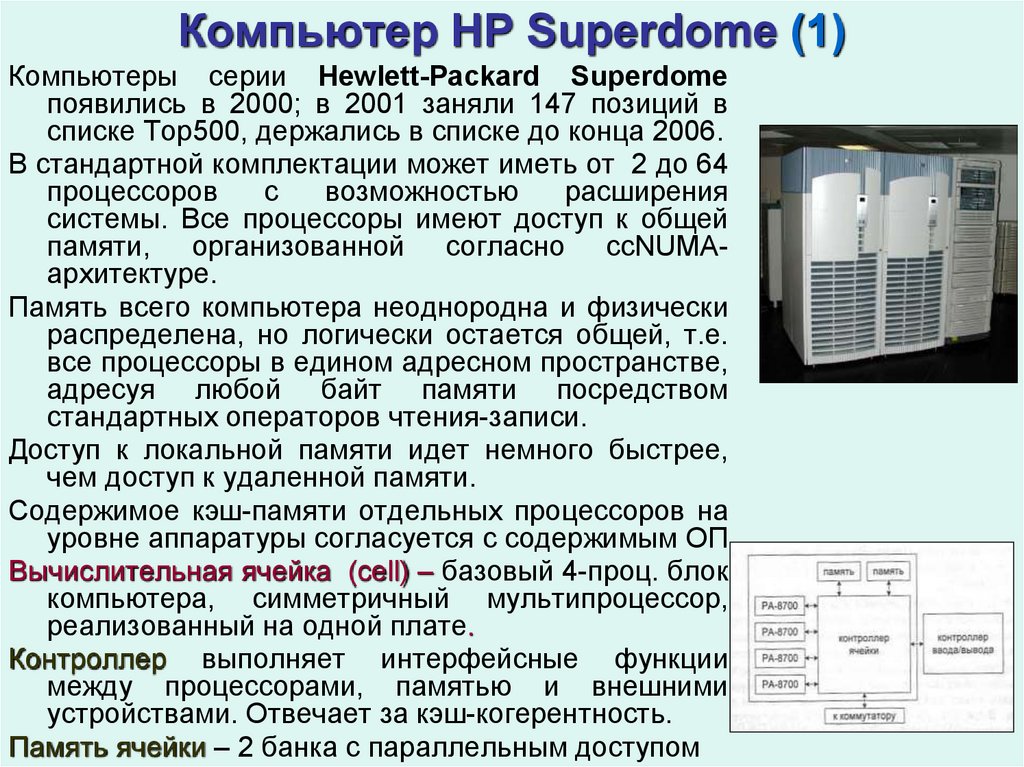

12. Компьютер НР Superdome (1)

Компьютеры серии Hewlett-Packard Superdomeпоявились в 2000; в 2001 заняли 147 позиций в

списке Тор500, держались в списке до конца 2006.

В стандартной комплектации может иметь от 2 до 64

процессоров

с

возможностью

расширения

системы. Все процессоры имеют доступ к общей

памяти, организованной согласно ccNUMAархитектуре.

Память всего компьютера неоднородна и физически

распределена, но логически остается общей, т.е.

все процессоры в едином адресном пространстве,

адресуя любой байт памяти посредством

стандартных операторов чтения-записи.

Доступ к локальной памяти идет немного быстрее,

чем доступ к удаленной памяти.

Содержимое кэш-памяти отдельных процессоров на

уровне аппаратуры согласуется с содержимым ОП.

Вычислительная ячейка (cell) – базовый 4-проц. блок

компьютера, симметричный мультипроцессор,

реализованный на одной плате.

Контроллер выполняет интерфейсные функции

между процессорами, памятью и внешними

устройствами. Отвечает за кэш-когерентность.

Память ячейки – 2 банка с параллельным доступом

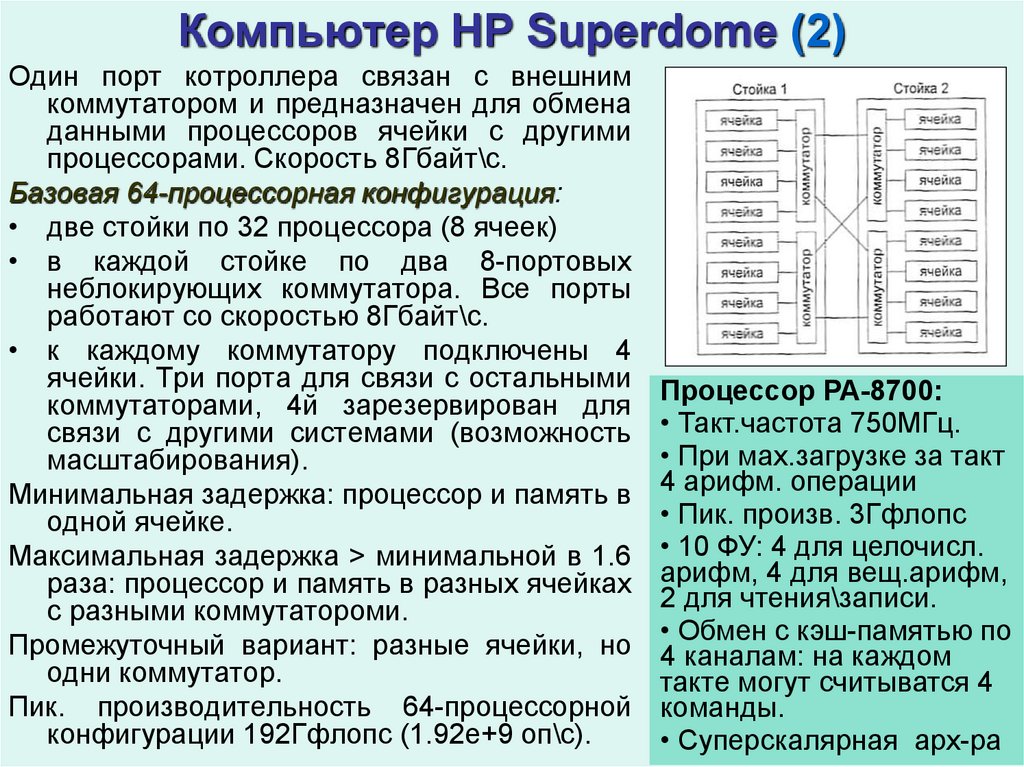

13. Компьютер НР Superdome (2)

Один порт котроллера связан с внешнимкоммутатором и предназначен для обмена

данными процессоров ячейки с другими

процессорами. Скорость 8Гбайт\с.

Базовая 64-процессорная конфигурация:

• две стойки по 32 процессора (8 ячеек)

• в каждой стойке по два 8-портовых

неблокирующих коммутатора. Все порты

работают со скоростью 8Гбайт\с.

• к каждому коммутатору подключены 4

ячейки. Три порта для связи с остальными

коммутаторами, 4й зарезервирован для

связи с другими системами (возможность

масштабирования).

Минимальная задержка: процессор и память в

одной ячейке.

Максимальная задержка > минимальной в 1.6

раза: процессор и память в разных ячейках

с разными коммутатороми.

Промежуточный вариант: разные ячейки, но

одни коммутатор.

Пик. производительность 64-процессорной

конфигурации 192Гфлопс (1.92е+9 оп\с).

Процессор РА-8700:

• Такт.частота 750МГц.

• При мах.загрузке за такт

4 арифм. операции

• Пик. произв. 3Гфлопс

• 10 ФУ: 4 для целочисл.

арифм, 4 для вещ.арифм,

2 для чтения\записи.

• Обмен с кэш-памятью по

4 каналам: на каждом

такте могут считыватся 4

команды.

• Суперскалярная арх-ра

14. Повышение эффективности работы микропроцессоров

Способы повышения производительности микропроцессоров:увеличение тактовой частоты. Технологические ограничения:

(1) рост энергопотребления (значит, и тепловыделения)

пропорционально 4й степени частоты;

(2) сверхтонкие технологии производства микросхем

обостряют проблему возможной утечки электротока

методы, повышающие производительность процессора за

счет увеличения количества инструкций программного кода,

параллельно выполняемых за один такт

(внутрипроцессорный параллелизм)

1. параллелизм на уровне машинных инструкций

(ILP, Instruction Level Parallelism)

2. параллельное исполнение потоков

(TLP, Thread Level Parallelism).

3. Спецпроцессоры

15. Параллелизм на уровне инструкций – суперскалярность

Параллелизм на уровне инструкций (ILP, Instruction Level Parallelism) –скрытый от пользователя параллелизм, нет необходимости в специальном

параллельном программировании со стороны пользователя, нет проблем

с переносимостью кода с одного компьютера на другой.

Суперскалярные процессоры – способны за один такт вызвать

несколько команд. Широко используется конвейерное выполнение

инструкций. Количество выполняемых команд в конкретный момент

времени зависит от конструкции процессора и от текущей ситуации.

Предполагается, что программа не содержит никакой информации о

возможности ее распараллеливания. Задача обнаружения и

реализации параллелизма возлагается на аппаратуру, которая и

строит соответствующую последовательность команд.

Максимально возможное количество вызываемых команд – обычно от

двух до шести – зависит от аппаратной реализации. Если для

выполнения команды необходим недоступный в данный момент

функциональный блок или еще не полученный результат другой

команды – такая команда не будет вызвана к выполнению.

Несколько ФУ, параллельно работающих в процессоре, исполняют по

мере возможности инструкции, находящиеся в специальном буфере,

куда они поступили после декодирования. Распараллеливание

происходит на уровне команд, совмещая выполнение двух или более

арифметических операций. Чтобы эффективно применять такую

архитектуру, кэш 1го уровня должен обладать высокими пропускной

способностью и емкостью.

16. Схема суперскалярного процессора с пятью функциональными блоками.

Схема пятиступенчатогоконвейера выполнения

команд.

Возможны сдвоенные

конвейеры

17. Параллелизм на уровне инструкций – VLIW

Very Large Instruction World (VLIW) – параллелизм реализуется за счетсверхдлинного командного слова.

Команда, выдаваемая компьютеру на каждом такте, содержит сразу

несколько операций, которые выполнятся параллельно. Команда

состоит из набора полей, каждое отвечает за свою операцию

(работа с памятью, активизация ФУ, операции с регистрами и др).

Если какая-то часть процессора на данном этапе не задействована,

соответствующее поле команды не заполняется.

Компилятор программы выявляет параллелизм и сообщает аппаратуре,

какие операции не зависят друг от друга. Формируется точный план,

как процессор будет выполнять программу (последовательность

выполнения операций, подключение ФУ, какие операнды в каких

регистрах…) и генерируется последовательность VLIW-инструкций.

Поскольку не все команды в полях VLIW-инструкций могут в нужный

момент обратиться к нужным функциональным устройствам – в

современных архитектурах предусмотрен механизм «связок»

нескольких VLIW-инструкций, которые могут быть выполнены

целиком. Задача по подготовке таких связок решается компилятором.

18. Суперскалярность и VLIW – сравнение

Итак, в суперскалярных процессорах функции распараллеливания лежатна аппаратуре, в VLIW-процессорах – на компиляторе.

Исторически первые суперскалярные процессоры - советские Эльбрусы.

Поддержка суперскалярности: Pentium, AMD, архитектура x86 и др.

VLIW-процессоры появились в конце 80х. Элементы архитектуры

содержались в серии PA-RISC. Пример классического VLIWпроцессора: Itanium (долго был самым мощным процессором в мире).

Плюсы VLIW

(1) Компилятор является более «умной» системой, чем аппаратура,

способной хранить больше контекстной информации и значит

принимать более верные решения об оптимизации.

(2) Подход VLIW сильно упрощает архитектуру процессора. Поскольку

отсутствуют большие и сложные узлы, снижается энергопотребление.

Минусы VLIW

(1) Невысокая плотность кода, большое количество пустых инструкций

для простаивающих устройств. Коды для VLIW-процессоров гораздо

длиннее, чем аналогичные коды для традиционных архитектур

(2) Приходится полагаться на оптимизацию компилятора, который может

содержать ошибки. Разработка эффективного компилятора для VLIW

– сложнейшая задача.

EPIC (Explicitly Parallel Instruction Computing: Микропроцессор Intel Itanium,

имея суперскалярную архитектуру, кроме традиционной, содержит 64битную систему команд «с явным параллелизмом», которая позволяет

использовать VLIW-ядро непосредственно.

19. Параллелизм на уровне потоков (1)

Распараллеливание на уровне потоков TLP (в отличие от ILP) управляетсяпрограммно.

Виртуальная многопоточность создается в результате выделения в одном

физическом процессоре двух или более логических. Классический

пример – технология Hyper-Threading (НТ) компании Intel.

Зачем:

(1) В современных конвейеризованных процессорах, если при запросе к

памяти слово отсутствует в кэшах 1го или 2го уровней – на его

загрузку уходит время, в течение которого конвейер простаивает.

Выход – организация внутрипроцессорной многопоточности

(2) В течение такта, как правило, не все исполнительные модули

процессора

задействованы,

поэтому

их

можно

загрузить

параллельным потоком. Понятно, что вдвое производительность не

увеличится, т.к. параллельные потоки используют общие память, кэш

и др., плюс потери из-за синхронизации и распараллеливания

инструкции. По имеющимся данным, рост производительности 3550%

Таким образом, многопоточность позволяет маскировать простои. Если

поток 1 блокирован, загрузка аппаратуры обеспечивается потоком 2.

Минус TLP – возникновение конфликта при обращении из разных потоков

к одному адресу памяти или когда одному потоку требуются

результаты выполнения другого. Это приводит к росту количества

тактов, необходимых для выполнения инструкций многоядерность

20. Параллелизм на уровне потоков (2)

Многопроцессорная конфигурация на одном кристалле обеспечиваетболее высокую скорость обмена между ядрами, чем использование

внешних шин, коммутаторов и т.п. При этом у каждого ядра свой

набор регистров, кэш, ФУ и др.

Компания IBM первой интегрировала в кристалл два процессорных ядра в

технологии Power4. Многоядерные процессоры относятся к SMPсистемам, но имеют отличия от «классических» SMP-архитектур.

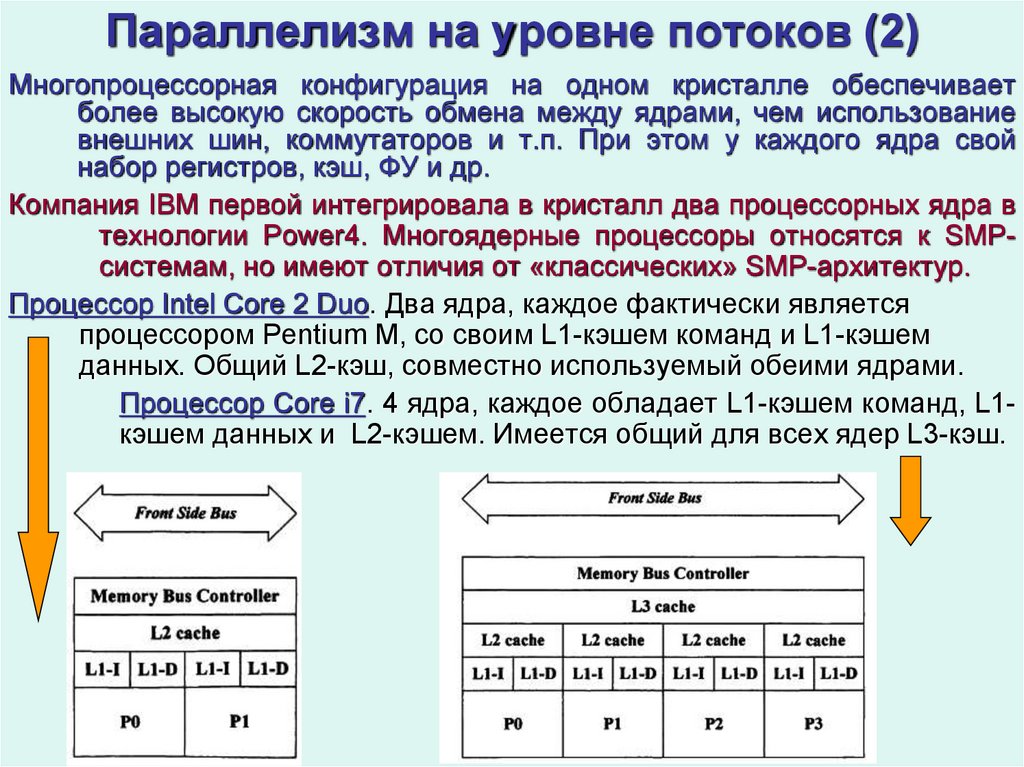

Процессор Intel Core 2 Duo. Два ядра, каждое фактически является

процессором Pentium M, со своим L1-кэшем команд и L1-кэшем

данных. Общий L2-кэш, совместно используемый обеими ядрами.

Процессор Core i7. 4 ядра, каждое обладает L1-кэшем команд, L1кэшем данных и L2-кэшем. Имеется общий для всех ядер L3-кэш.

21. Параллелизм на уровне потоков (3)

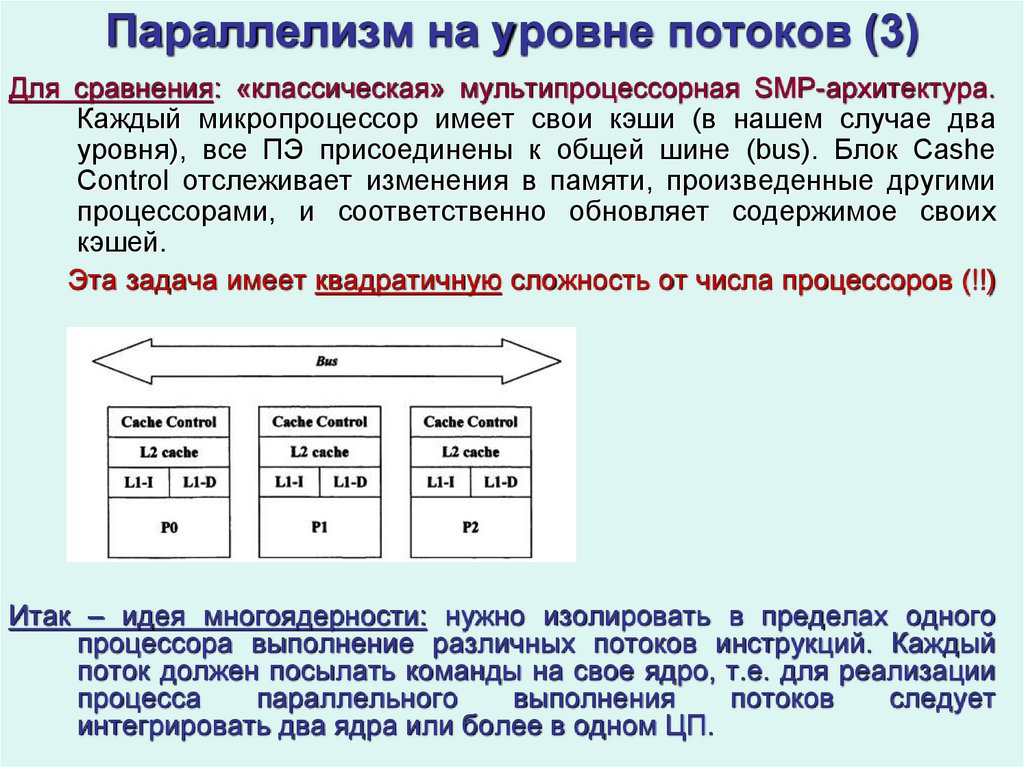

Для сравнения: «классическая» мультипроцессорная SMP-архитектура.Каждый микропроцессор имеет свои кэши (в нашем случае два

уровня), все ПЭ присоединены к общей шине (bus). Блок Cashe

Control отслеживает изменения в памяти, произведенные другими

процессорами, и соответственно обновляет содержимое своих

кэшей.

Эта задача имеет квадратичную сложность от числа процессоров (!!)

Итак – идея многоядерности: нужно изолировать в пределах одного

процессора выполнение различных потоков инструкций. Каждый

поток должен посылать команды на свое ядро, т.е. для реализации

процесса

параллельного

выполнения

потоков

следует

интегрировать два ядра или более в одном ЦП.

22. Параллелизм на уровне потоков (4)

Характерные особенности многоядерных архитектур(1) Многоступенчатая организация кэшей. Общий кэш для нескольких ядер

хорошо сказывается на производительности благодаря быстрому

доступу к совместно используемой информации. Однако при этом

велика вероятность возникновения конфликтов. Многоступенчатая

же организация кэша позволяет использовать его наиболее

эффективно.

(2) Аппаратная реализация многопоточности. Начиная с Power4,

многопоточность реализуется на аппаратном уровне: каждое из двух

и более ядер выполняет свой поток команд, при задержке

выполнения одного потока ресурсы обслуживающего его ядра нельзя

передать другому потоку.

(3) Поддержка приоритетов. Многопоточная технология SMT (впервые в

Power5): аппаратное распределение приоритетов выполнения

потоков (8 уровней). Потоку с высоким приоритетом предоставляется

большая часть ресурсов. Когда приложению требуется использовать

всю полосу пропускания обмена данными с памятью, то процессор

автоматически переходит в однопоточный режим.

(4) Сверхплотная компоновка. Технология сверхплотной компоновки,

особенность которой заключается в применении общей оперативной

памяти и межузловых соединений с большой пропускной

способностью, позволяет реализовать высокоскоростные соединения

между ядрами (в Power5 8 ядер, существуют 12-ядерные, 24-ядерные

системы и т.д.).

23. Параллелизм на уровне потоков (5)

(5) Дублирование ресурсов. У каждого потока свой счетчик команд,регистры, кэш, контроллер прерываний и др.

(6) Снижение энергопотребления и тепловыделения. При увеличении

числа команд за такт растет энергопотребление (и тепловыделение).

Механизмы решения проблемы (начиная с Power5):

При низком приоритете обоих потоков (0 или 1) включается

встроенная технология энергосбережения;

Возможно временное отключение тех компонентов процессора,

которые не потребуются во время следующих тактов.

В результате при прочих равных условиях Power5 выполняет на 50%

больше инструкций, чем Power4, без какого-либо ущерба для

производительности и при одинаковых затратах энергии.

Работы по повышению быстродействия микропроцессоров идут в

следующих направлениях:

- Повышение тактовой частоты

- Размещение на одной микросхеме двух и более процессоров

- Введение новых функциональных блоков

- Удлинение конвейера

- Использование многопоточности

- Поддержка SIMD-вычислений

24. Концепция RISC

Концепция RISC (Reduced Instruction Set) — вычисления с сокращённымнабором команд. Основной принцип: более компактные и простые

инструкции выполняются быстрее.

Простая архитектура позволяет удешевить процессор, поднять тактовую

частоту, а также распараллелить исполнение команд между

несколькими блоками исполнения (в суперскалярных архитектурах).

Многие ранние RISC-процессоры даже не имели команд умножения и

деления. Идея создания RISC ЦП пришла после того, как в 1970х

ученые из IBM обнаружили, что многие функциональные особенности

традиционных ЦПУ игнорировались программистами.

Поскольку создатели процессоров тратили гораздо меньше времени на

улучшение сложных команд, чем на улучшение простых, некоторые

сложные операции были медленнее, чем те же действия,

выполняемые набором простых команд.

Первые RISC-процессоры разработаны в начале 1980х в Стэнфордском и

Калифорнийском университетах. Небольшой (50−100) набор команд

по сравнению с CISC (Complex Instruction Set Computer) 100—200.

Как оказалось в начале 1990х, RISC-архитектуры позволяют получить

большую производительность, чем CISC за счет возможности

серьезного повышения тактовой частоты и за счет упрощения

кристалла с высвобождением площади под кэш-память.

RISC-архитектуры позволили сильно снизить энергопотребление

процессора за счет уменьшения числа транзисторов.

25. Параллелизм в архитектуре процессоров (10)

Характерные особенности RISC-процессоров:Фиксированная длина машинных инструкций (напр., 32 бита), простой

формат команды.

Специализированные команды для операций с памятью — чтения или

записи. Операции вида «прочитать-изменить-записать» отсутствуют.

Любые операции «изменить» выполняются только над содержимым

регистров (т. н. load-and-store архитектура).

Большое количество регистров общего назначения (32 и более).

Отсутствие поддержки операций вида «изменить» над укороченными

типами данных — байт, 16-битное слово.

Отсутствие микропрограмм внутри самого процессора. Традиционными

решениями в рамках концепции RISC являются суперскалярность и

VLIW-архитектура.

Практически все современные процессоры — это суперскалярные

RISC-системы.

Спекулятивное исполнение сокращает простой конвейера при условных

переходах. При встрече с командой условного перехода процессор

исполняет (или в кэш инструкций) сразу все ветви, пока не закончится

вычисление условия перехода.

Переименование регистров. Каждый регистр процессора на самом деле

представляет собой несколько параллельных регистров, хранящих

несколько версий значения. Используется для реализации

спекулятивного исполнения.

26. Спецпроцессоры

Спецпроцессоры разрабатываются для определенного круга задач.Идея состоит в эффективной программно-аппаратной реализации

особенностей конкретных алгоритмов.

Спецпроцессоры могут объединять множество (до сотен тысяч)

параллельно работающих элементарных ФУ. Нет гибкости и

универсальности, зато очень высокая производительность для

конкретного, узкого круга задач.

Примеры: обработка сигналов, распознавание речи, компьютерная

графика, спецпроцессоры для задач молекулярной динамики,

аппаратная поддержка быстрого преобразования Фурье, технология

ПЛИС (программируемые под конкретную задачу интегральные схемы).

Поддержка векторных (SIMD) вычислений – характерная особенность

современных процессоров, включая центральные процессоры,

спецпроцессоры и со-процессоры. Streaming SIMD Extensions

(потоковое SIMD-расширение процессора) — набор инструкций,

первоначально разработанный Intel (впервые представлен в

процессорах серии Pentium 3).

В архитектуру процессора включаются регистры длины 128 бит и более +

набор инструкций для работы со скалярными и упакованными типами

данных. Каждый регистр (128 бит) может содержать четыре 32-битных

значения с плавающей точкой одинарной точности или два двойной

точности. C помощью SSE-команд арифметические действия могут

производится сразу над всеми упакованными числами.

В итоге реализуется идея векторизации вычислений (см. Лекцию 3)

27.

Процессоры CELLРазработка процессора CELL была начата в 2001 альянсом Sony,

Toshiba, IBM (альянс STI).

Работы велись более чем 400 инженерами трех компаний.

За основу была взята архитектура IBM POWER4.

Первое коммерческое применение – игровая консоль Sony Playstation3

(2005)

В 2008 появился процессор PowerXCell 8i.

Основная особенность – заметное повышение производительности в

вычислениях с двойной точностью: около 100 Гфлопс против 14 в

более ранних моделях.

Первое применение PowerXCell 8i – суперкомпьютер IBM RoadRunnder

(10е место в списке Тор500 2011, 22e – в 2012).

С 2014 в списке ТОР500 процессоры PowerXCell 8i фигурируют в составе

«Ломоносова»

«Сellular architecture» («клеточная» архитектура):

множество однотипных процессоров со плотной

Компоновкой и встроенной возможностью

объединения в единую унифицированную

"суперсистему".

28.

Процессор CELL состоит из:1. ПЭ на основе POWER-архитектуры (PPE, POWER Processor Element);

2 64-разрядных процессорных ядра. Если CELL используется как ЦП,

то РРЕ выполняет функции ОС + код пользовательских приложений.

2. 8 Синергических ПЭ (SPE, Synergistic Processor Element); RISCпроцессоры, оптимизированные для высокопроизв. вычислений.

3. Шина Взаимосвязываемых Элементов (EIB, Element Interconnect Bus);

4. Контроллер Интерфейса Памяти (MIC, Memory Interface Controller);

5. Контроллер Интерфейса Шины ввода/вывода (Bus Interface Controller)

Синергетический ПЭ – спец. вект. проц.

для обработки SIMD-инструкций.

4 блока для целочисленной векторной

арифметики и 4 блока для операций с

плавающей запятой.

В каждом СПЭ - 128 128-битных регистров.

Вместо L1-кэша – локальная память (4

сегмента по 64Кбайт), а также DMAконтроллер для обмена данными между

ОП (RAM) и локальной (LM/LS), минуя PPE.

Содержимое регистра может трактоваться

как 2 числа двойной точности, 4 одинарной

или набор целых чисел. Система команд

поддерживает работу со всеми элементами

регистра за 1 такт.

Частота 3.2ГГц

Информатика

Информатика