Похожие презентации:

Цифровые устройства и микропроцессоры. Тема 1. Основы схемотехники и элементная база цифровых электронных устройств

1.

ВОЕННАЯ АКАДЕМИЯ ВОЗДУШНО-КОСМИЧЕСКОЙ ОБОРОНЫИМЕНИ МАРШАЛА СОВЕТСКОГО СОЮЗА Г.К. ЖУКОВА

Кафедра № 13

основ построения радиоэлектронных средств и систем

Учебная дисциплина Д-1321

«ЦИФРОВЫЕ УСТРОЙСТВА И

МИКРОПРОЦЕССОРЫ»

Тверь 2018

2.

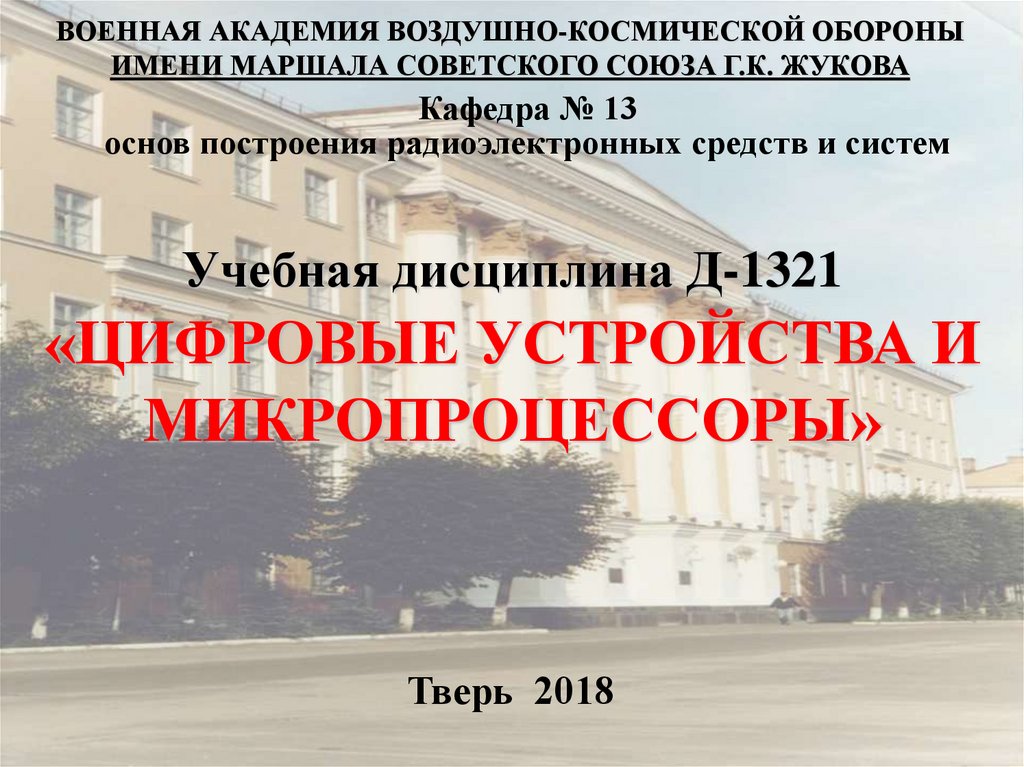

СТРУКТУРА УЧЕБНОЙ ДИСЦИПЛИНЫ ДС-1321Номера и наименование

разделов и тем

Всего

часов

Из них по видам занятий

Лекции Лаб.раб. Пр.зан.

Зачет

5 семестр

Введение

2

2

Тема 1. Основы схемотехники и элементная база

комбинационных цифровых электронных

устройств

14

6

4

4

Тема 2. Основы схемотехники и элементная база

последовательностных цифровых электронных

устройств

24

10

8

6

Тема 3. Аналого-цифровые и цифро-аналоговые 10

преобразователи

4

4

2

Тема 4. Запоминающие устройства ЭВМ и МПС

8

4

2

2

Тема 5. Микропроцессоры и микропроцессорные

системы

26

16

Заключение

2

2

Зачет с оценкой в конце 5-го семестра

4

Всего по дисциплине

90

10

4

44

18

24

4

3.

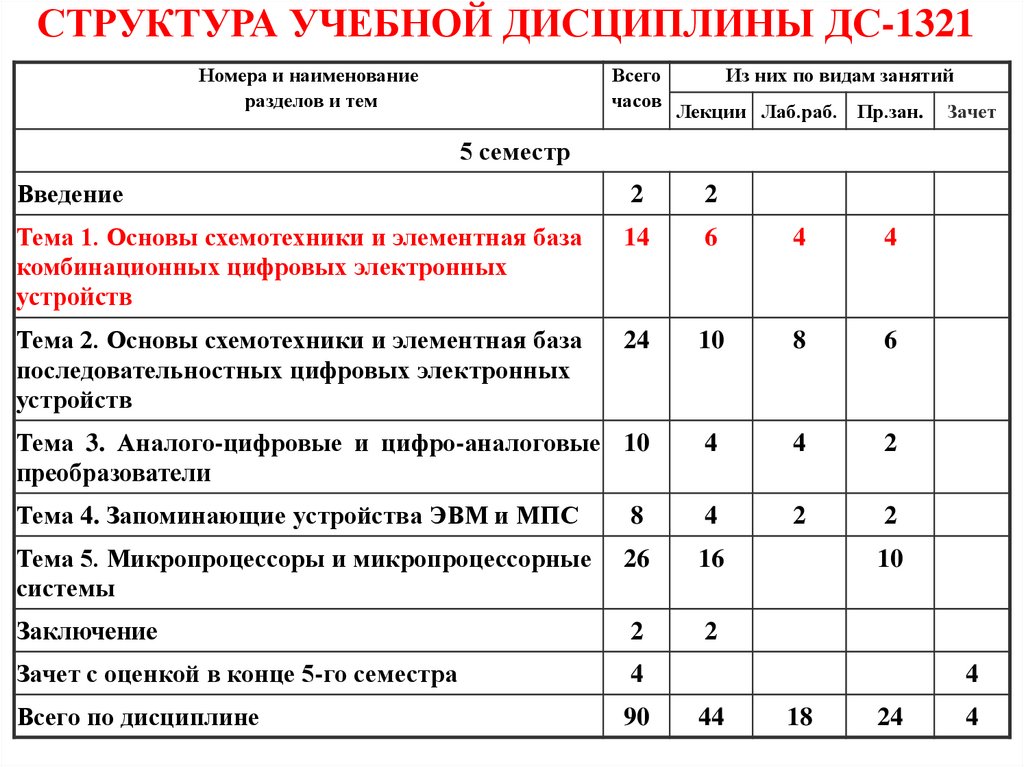

Содержание темы 1«Основы схемотехники и элементная база

комбинационных цифровых электронных устройств»

Номера и вид

занятий

Лекция

№2

Наименование тем занятий

Математическое описание комбинационных

цифровых устройств

Пр.занятие Анализ и синтез комбинационных цифровых

№1

устройств

Основы схемотехники и элементная база

Лекция №3 типовых комбинационных цифровых

электронных устройств

Пр.занятие Анализ и расчет типовых комбинационных

№2

цифровых узлов ЭВМ.

Экспериментальное исследование типовых

Лаб. работа

комбинационных цифровых электронных узлов

№1

радиотехнических систем и ЭВМ

4.

ЛЕКЦИЯ №3Основы схемотехники и

элементная база типовых

комбинационных цифровых

электронных устройств

5.

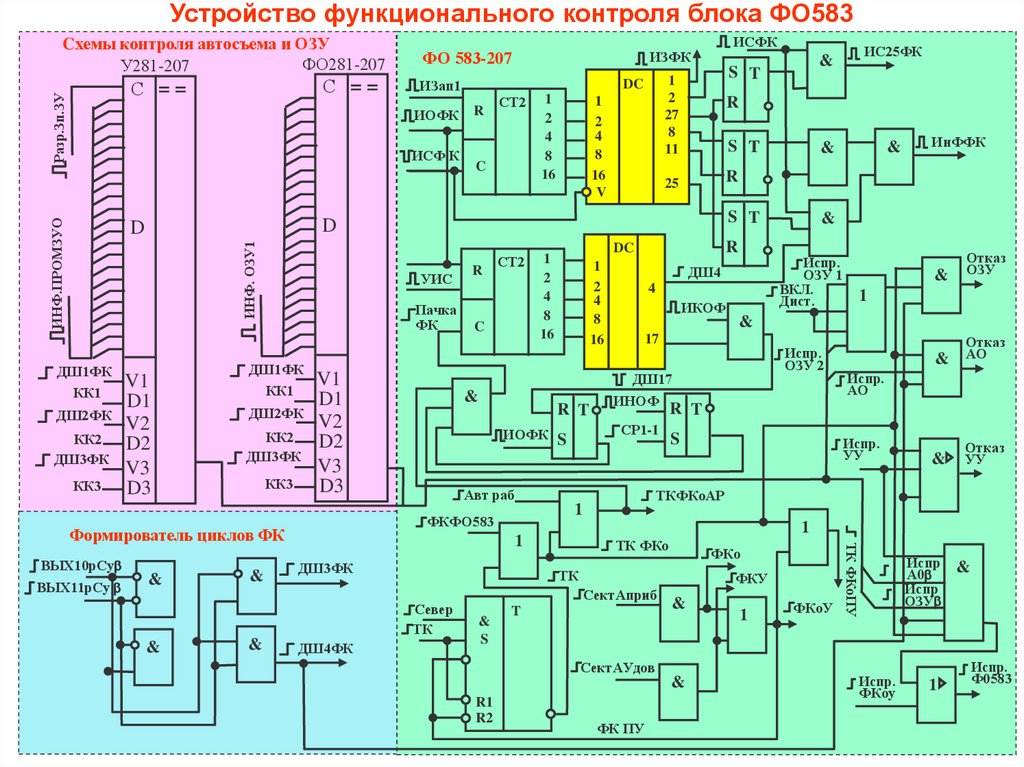

Устройство функционального контроля блока ФО583Cхемы контроля автосъема и ОЗУ

ФО281-207

У281-207

С ==

Разр.Зп.ЗУ

С ==

ФО 583-207

ИЗап1

ИОФК

ИНФ.ПРОМЗУО

ИСФ К

ИНФ. ОЗУ1

ДШ2ФК

КК2

ДШ3ФК

КК3

S T

V1

D1

V2

D2

V3

D3

Пачка

ФК

ДШ1ФК

КК1

ДШ2ФК

КК2

ДШ3ФК

КК3

V1

D1

V2

D2

V3

D3

&

&

&

C

1

2

4

8

16

ИОФК

4

ИКОФ

СР1-1

S

Испр.

ОЗУ 2

Отказ

& АО

Испр.

АО

R T

S

ТК ФКо

Испр.

УУ

ФКо

ТК

ФКУ

СектАприб

T

&

СектАУдов

&

R1

R2

1

&

Отказ

УУ

1

1

&

S

Отказ

ОЗУ

ТКФКоАР

1

ДШ3ФК

&

&

17

ИНОФ

&

Испр.

ОЗУ 1

ВКЛ.

Дист.

ДШ4

Авт раб

ФКФО583

ДШ4ФК

R

ДШ17

R T

ИнФФК

R

25

DC

1

2

4

8

16

&

Север

ТК

&

R

СТ2

&

&

ФК ПУ

1

ФКоУ

ТК ФКоПУ

ВЫХ11рСу

R

S T

УИС

Формирователь циклов ФК

ВЫХ10рСу

C

1

2

4

8

16

V

D

D

ДШ1ФК

КК1

СТ2

1

2

4

8

16

ИС25ФК

&

S T

1

2

27

8

11

DC

R

ИСФК

ИЗФК

Испр.

ФКоу

Испр

А0

Испр

ОЗУ

1

&

Испр.

Ф0583

6.

ФОРМИРУЕМАЯ КОМПЕТЕНЦИЯСпособность учитывать в профессиональной деятельности

современные

тенденции

развития

электроники,

измерительной и вычислительной техники (ОПК-6).

ПЛАНИРУЕМЫЕ РЕЗУЛЬТАТЫ ОБУЧЕНИЯ

ЗНАТЬ:

основы схемотехники и элементную базу цифровых

электронных устройств, архитектуру, условия и способы

использования микропроцессоров и микропроцессорных

систем в электронных устройствах.

УЧЕБНАЯ ЦЕЛЬ ЛЕКЦИИ

Систематизировать основы научных знаний по основам

схемотехники и элементной базе комбинационных

цифровых устройств.

7.

УЧЕБНЫЕ ВОПРОСЫ ЛЕКЦИИ1.

2.

3.

4.

5.

Шифраторы и дешифраторы.

Мультиплексоры и демультиплексоры.

Сумматоры и арифметико-логические устройства.

Схемы контроля четности.

Методы расчета типовых комбинационных

цифровых устройств.

8.

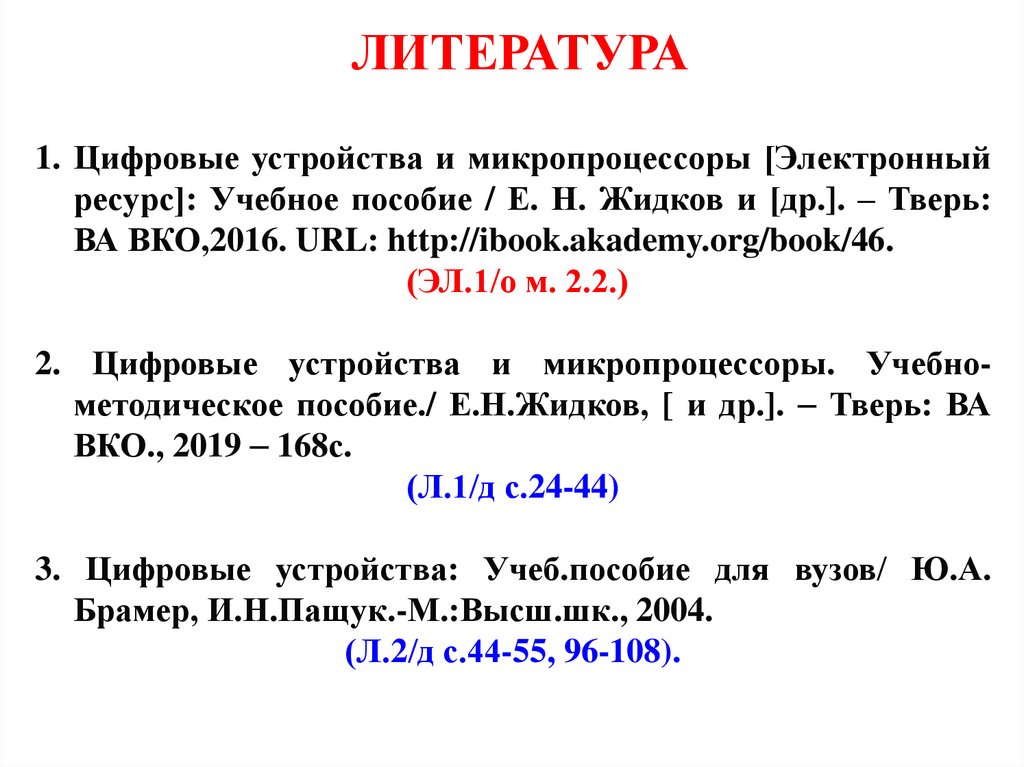

ЛИТЕРАТУРА1. Цифровые устройства и микропроцессоры [Электронный

ресурс]: Учебное пособие / Е. Н. Жидков и [др.]. – Тверь:

ВА ВКО,2016. URL: http://ibook.akademy.org/book/46.

(ЭЛ.1/о м. 2.2.)

2. Цифровые устройства и микропроцессоры. Учебнометодическое пособие./ Е.Н.Жидков, [ и др.]. Тверь: ВА

ВКО., 2019 168с.

(Л.1/д с.24-44)

3. Цифровые устройства: Учеб.пособие для вузов/ Ю.А.

Брамер, И.Н.Пащук.-М.:Высш.шк., 2004.

(Л.2/д с.44-55, 96-108).

9.

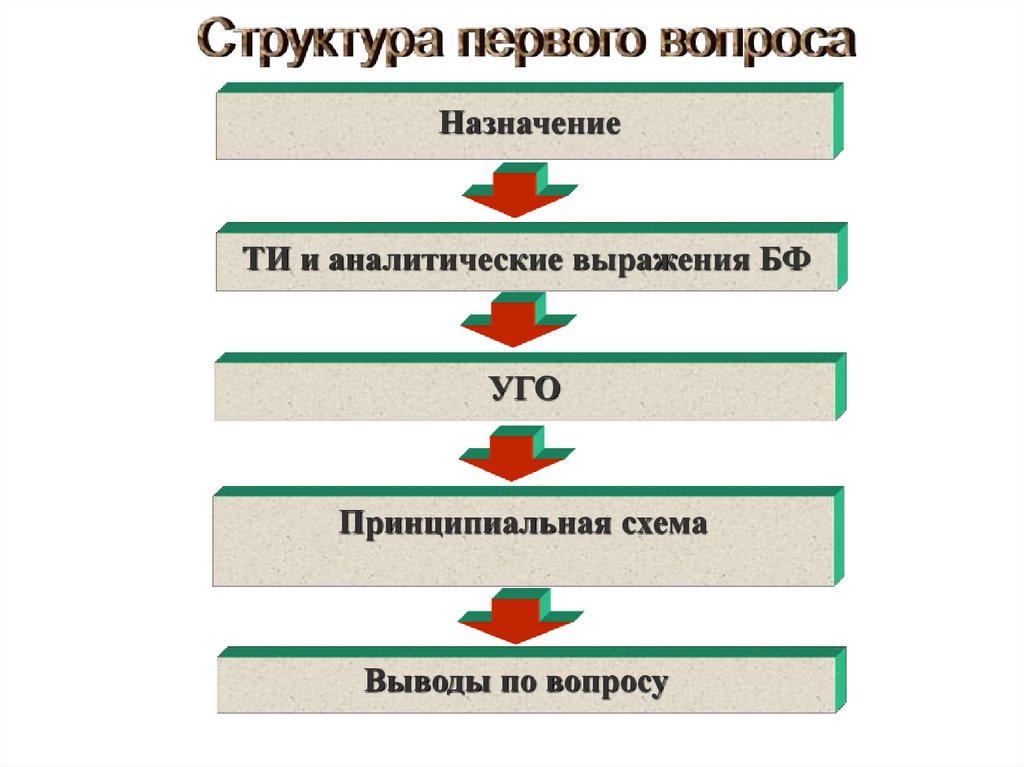

1. Шифраторы и дешифраторы10.

НазначениеТИ и аналитические выражения БФ

УГО

Принципиальная схема

Выводы по вопросу

11.

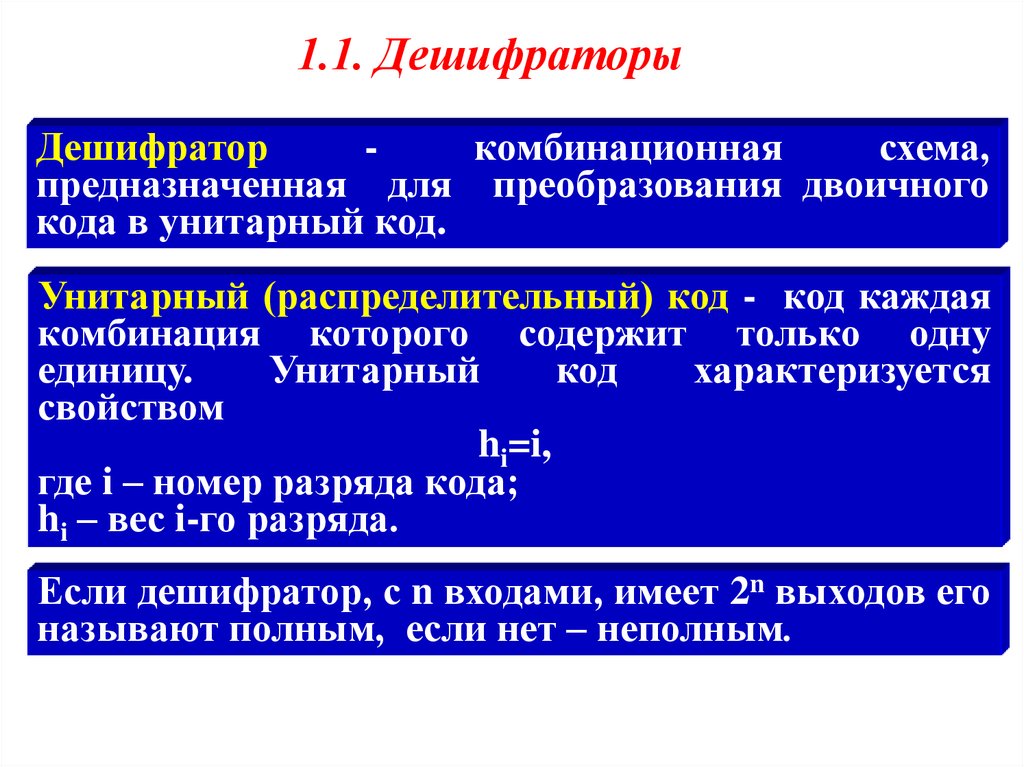

1.1. ДешифраторыДешифратор

комбинационная

схема,

предназначенная для преобразования двоичного

кода в унитарный код.

Унитарный (распределительный) код - код каждая

комбинация которого содержит только одну

единицу.

Унитарный

код

характеризуется

свойством

hi=i,

где i – номер разряда кода;

hi – вес i-го разряда.

Если дешифратор, с n входами, имеет 2n выходов его

называют полным, если нет – неполным.

12.

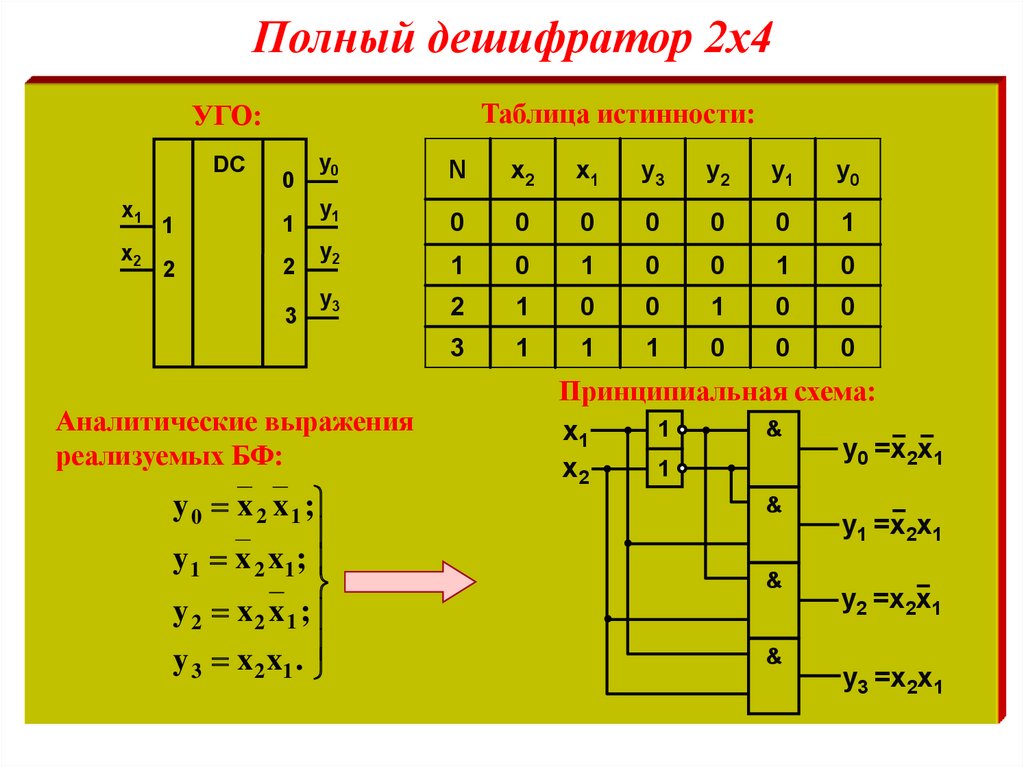

Полный дешифратор 2х4Таблица истинности:

УГО:

DC

x1

x2

0

1

1

2

2

3

y0

y1

y2

y3

Аналитические выражения

реализуемых БФ:

y 0 x 2 x 1 ;

y 1 x 2 x1 ;

y 2 x2 x 1 ;

y 3 x 2 x1 .

N

x2

x1

y3

y2

y1

y0

0

0

0

0

0

0

1

1

0

1

0

0

1

0

2

1

0

0

1

0

0

3

1

1

1

0

0

0

Принципиальная схема:

1

&

x1

y0 =x2x1

1

x2

&

&

&

y1 =x2x1

y2 =x2x1

y3 =x2x1

13.

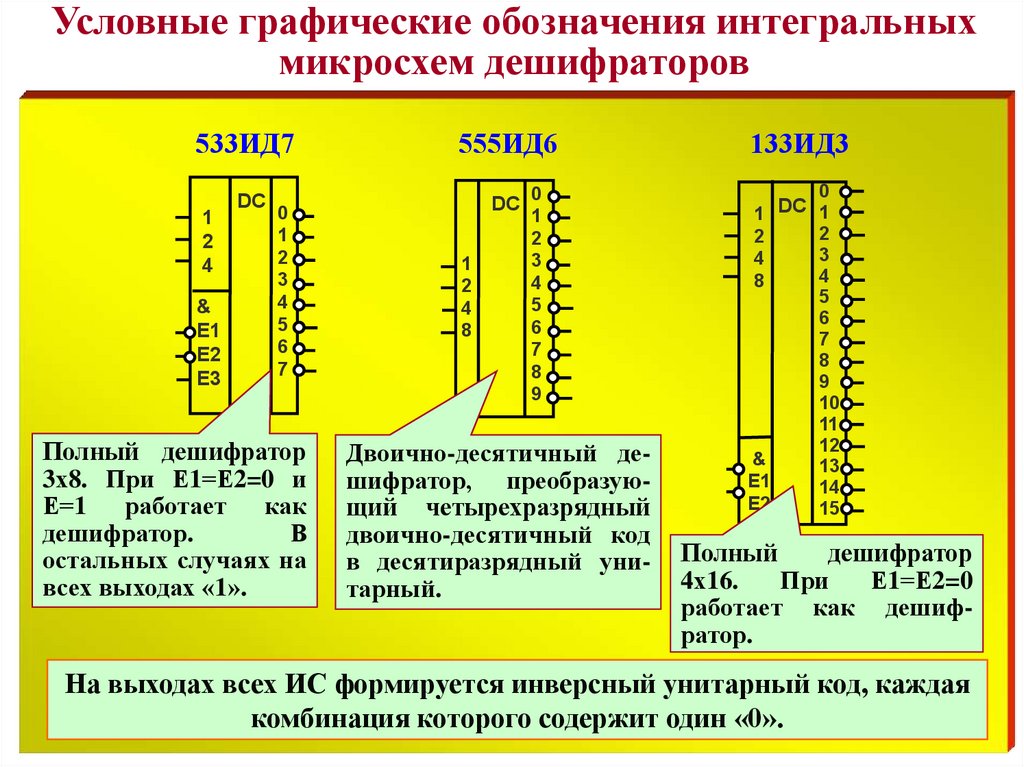

Условные графические обозначения интегральныхмикросхем дешифраторов

533ИД7

1

2

4

&

E1

E2

E3

DC

0

1

2

3

4

5

6

7

Полный дешифратор

3х8. При Е1=Е2=0 и

Е=1 работает как

дешифратор.

В

остальных случаях на

всех выходах «1».

555ИД6

DC

1

2

4

8

0

1

2

3

4

5

6

7

8

9

Двоично-десятичный дешифратор, преобразующий четырехразрядный

двоично-десятичный код

в десятиразрядный унитарный.

133ИД3

0

1 DC 1

2

4

8

&

E1

E2

2

3

4

5

6

7

8

9

10

11

12

13

14

15

Полный

дешифратор

4х16.

При

Е1=Е2=0

работает как дешифратор.

На выходах всех ИС формируется инверсный унитарный код, каждая

комбинация которого содержит один «0».

14.

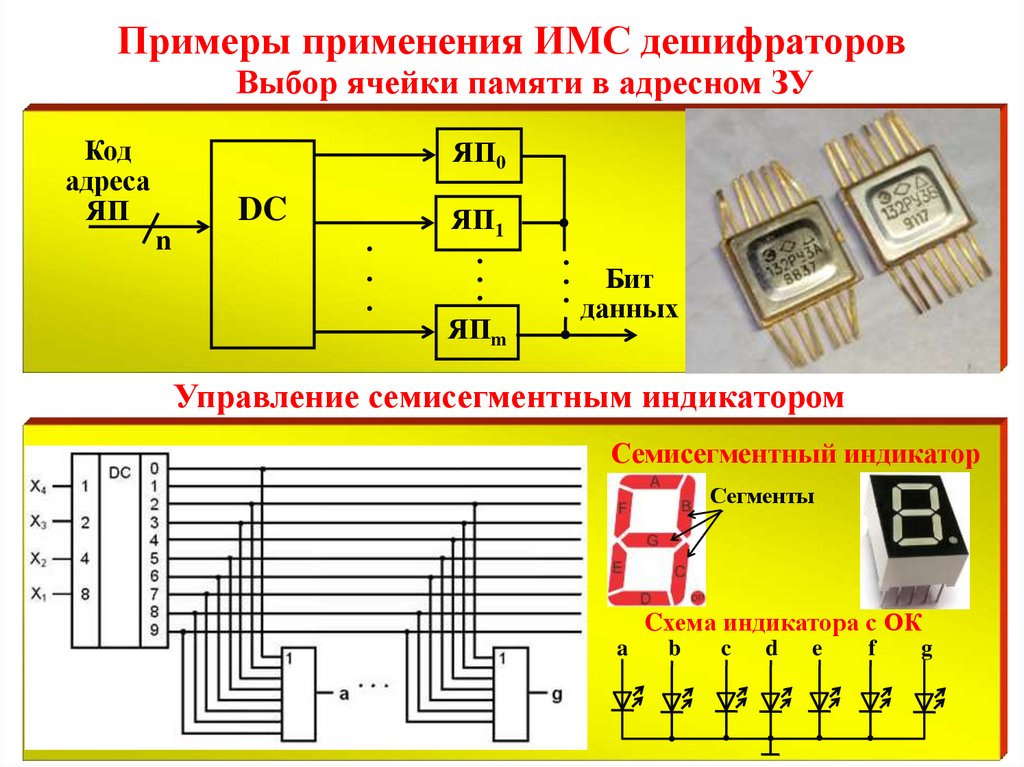

Примеры применения ИМС дешифраторовВыбор ячейки памяти в адресном ЗУ

Код

адреса

ЯП

ЯП0

DC

n

.

.

.

ЯП1

.

.

.

ЯПm

.

.

.

Бит

данных

Управление семисегментным индикатором

Семисегментный индикатор

Сегменты

Cхема индикатора с ОК

a

b

c

d

e

f

g

15.

Конструктивное исполнение интегральныхмикросхем дешифраторов

Корпус 238.16-2

2 – тип корпуса;

38 – подтип;

16 – количество выводов;

2 – регистрационный номер.

Корпус 239.24-1

2 – тип корпуса;

39 – подтип;

24 – количество выводов;

1 – регистрационный номер.

16.

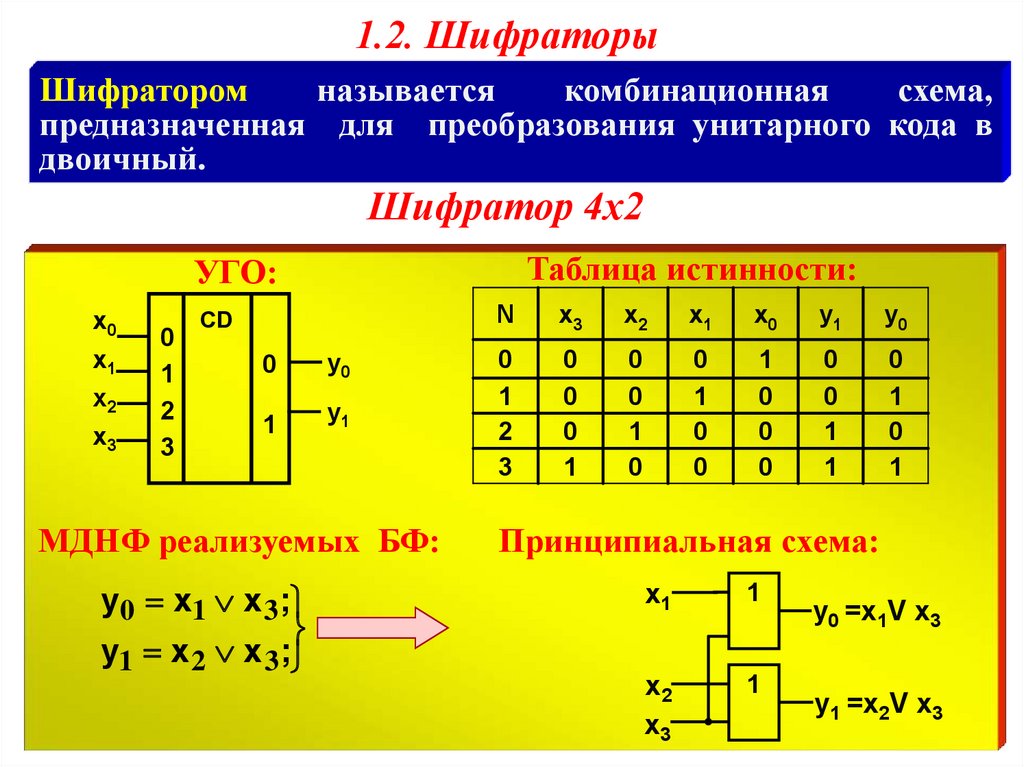

1.2. ШифраторыШифратором

называется

комбинационная

схема,

предназначенная для преобразования унитарного кода в

двоичный.

Шифратор 4х2

Таблица истинности:

УГО:

x0

x1

x2

x3

0

1

2

3

CD

0

y0

1

y1

МДНФ реализуемых БФ:

y0 x1 х 3 ;

y1 x 2 х 3 ;

N

x3

x2

x1

x0

y1

y0

0

1

2

3

0

0

0

1

0

0

1

0

0

1

0

0

1

0

0

0

0

0

1

1

0

1

0

1

Принципиальная схема:

x1

1

x2

x3

1

y0 =x1V x3

y1 =x2V x3

17.

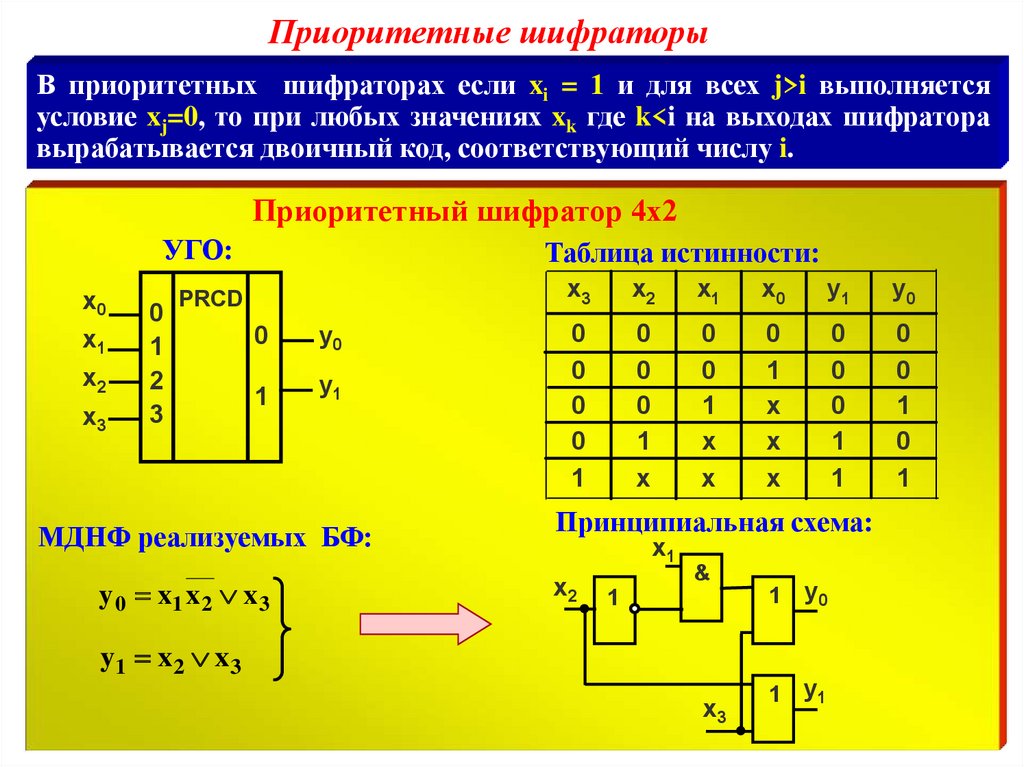

Приоритетные шифраторыВ приоритетных шифраторах если xi = 1 и для всех j>i выполняется

условие xj=0, то при любых значениях xk где k<i на выходах шифратора

вырабатывается двоичный код, соответствующий числу i.

Приоритетный шифратор 4х2

УГО:

x0

x1

x2

x3

0

1

2

3

Таблица истинности:

PRCD

0

y0

1

y1

МДНФ реализуемых БФ:

y 0 x1 x 2 x 3

x3

x2

x1

x0

y1

y0

0

0

0

0

1

0

0

0

1

x

0

0

1

x

x

0

1

x

x

x

0

0

0

1

1

0

0

1

0

1

Принципиальная схема:

x1

x2

&

1

1

y0

y1 x 2 x 3

x3

1 y1

18.

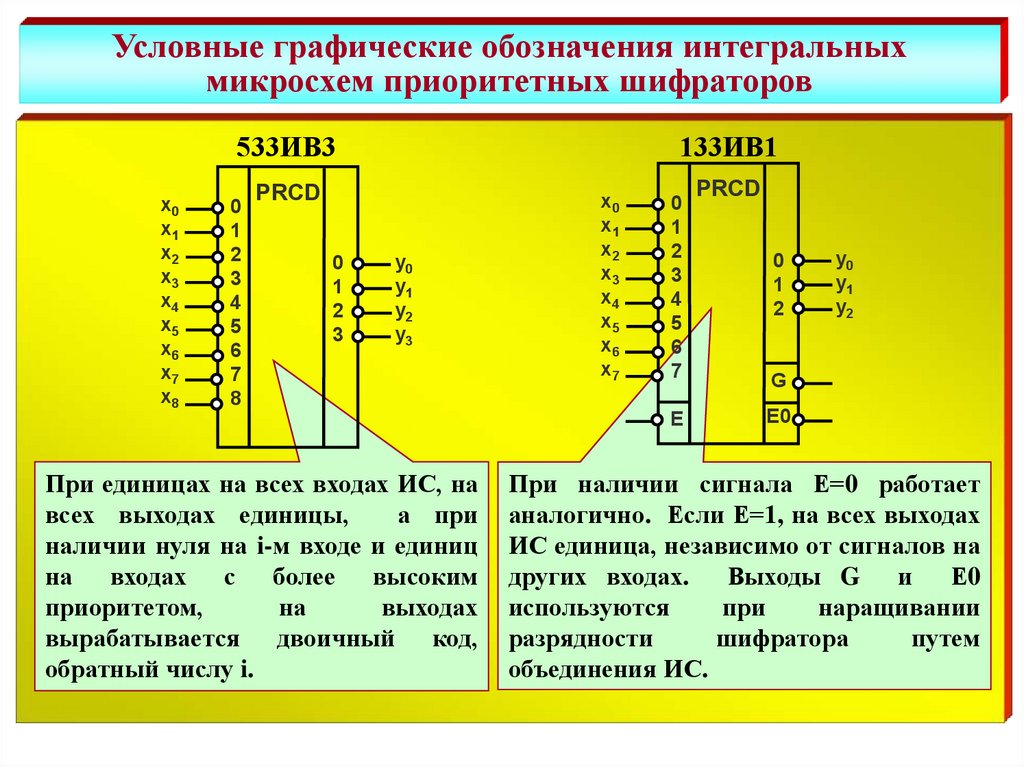

Условные графические обозначения интегральныхмикросхем приоритетных шифраторов

133ИВ1

533ИВ3

x0

x1

x2

x3

x4

x5

x6

x7

x8

0

1

2

3

4

5

6

7

8

PRCD

0

1

2

3

y0

y1

y2

y3

x0

x1

x2

x3

x4

x5

x6

x7

0

1

2

3

4

5

6

7

E

При единицах на всех входах ИС, на

всех выходах единицы,

а при

наличии нуля на i-м входе и единиц

на входах с более высоким

приоритетом,

на

выходах

вырабатывается двоичный код,

обратный числу i.

PRCD

0

1

2

y0

y1

y2

G

E0

При наличии сигнала Е=0 работает

аналогично. Если Е=1, на всех выходах

ИС единица, независимо от сигналов на

других входах. Выходы G и Е0

используются

при

наращивании

разрядности

шифратора

путем

объединения ИС.

19.

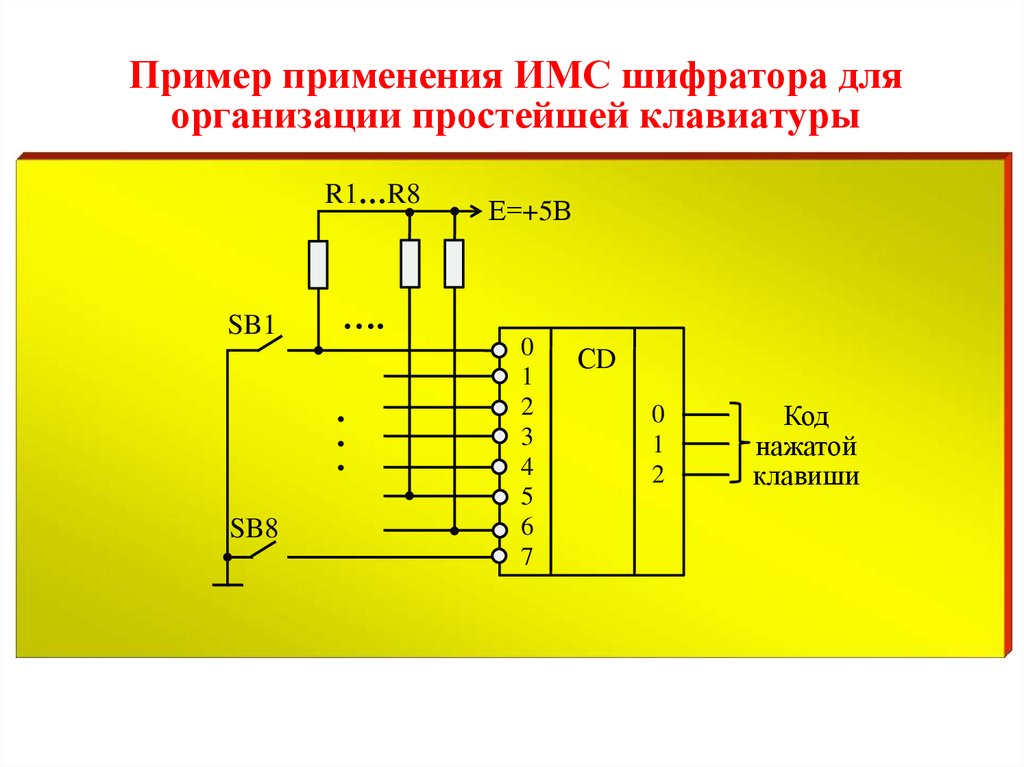

Пример применения ИМС шифратора дляорганизации простейшей клавиатуры

R1…R8

SB1

….

.

.

.

SB8

Е=+5В

0

1

2

3

4

5

6

7

СD

0

1

2

Код

нажатой

клавиши

20.

Дешифраторы преобразуют двоичный код в унитарный,а шифраторы преобразуют унитарный код в двоичный,

т.е. выполняют функцию, обратную дешифраторам.

Шифраторы и дешифраторы являются особыми

разновидностями преобразователей кодов.

21.

2. Мультиплексоры и демультиплексоры22.

НазначениеТИ и аналитические выражения БФ

Условные графические обозначения

Принципиальные схемы

Выводы по вопросу

23.

2.1. МультиплексорыМультиплексор

предназначен

для

коммутации

данных,

поступающих по одному из нескольким входных каналов в один

выходной канал в зависимости от значения управляющего кода.

Четырехканальный одноразрядный мультиплексор

Таблица истинности:

УГО:мультиплексора

Принцип работы

DI

Входные

Входные

каналы

каналы

Управл.

входы

x 0 x0

0

x 1 x1

1

x2 x22

x3 x33

A1

A1

A2 A

2

MUX

Выходной

канал y

Выходной

y канал

A 2A 1

Управляющие

входы

N

А2

А1

y

0

1

2

3

0

0

1

1

0

1

0

1

x0

x1

x2

x3

Принципиальная схема:

x0

x1

x2

x3

Аналитическое выражение

реализуемой БФ:

y x0 A2 A1 x1 A2 A1 x2 A2 A1 x3 A2 A1

А1

А2

DC 0

1

1

2

2

3

_ _

A2A1

_

A2A1

_

A2A1

A2A1

&

&

&

&

1

y

24.

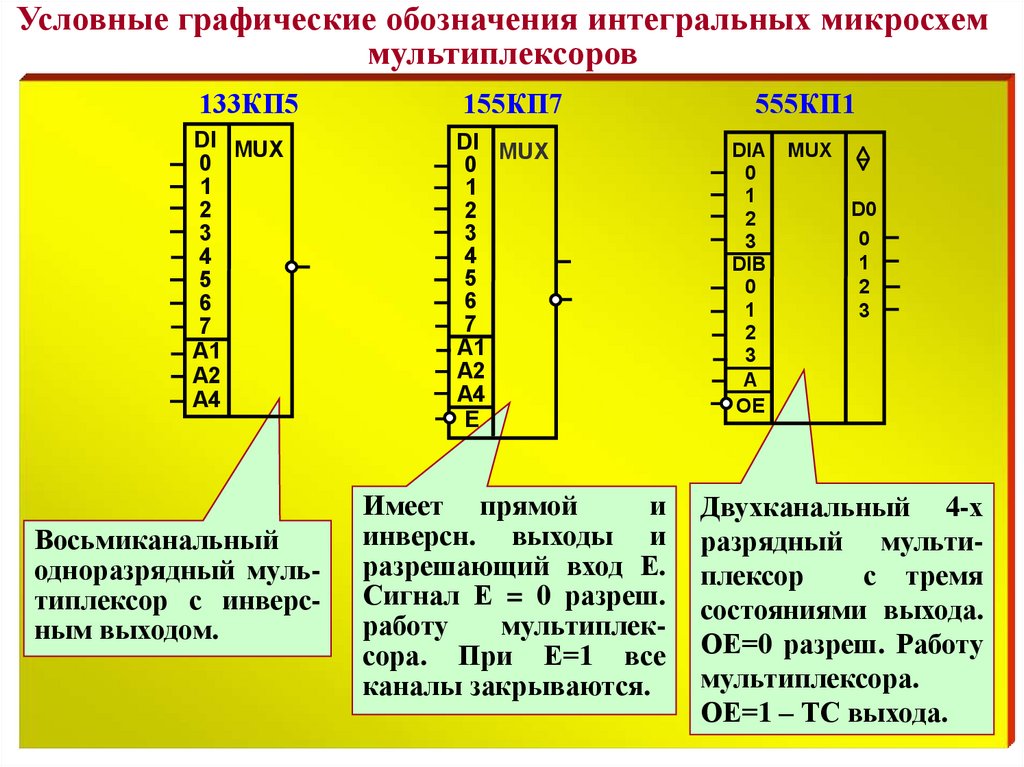

Условные графические обозначения интегральных микросхеммультиплексоров

133КП5

155КП7

DI MUX

0

1

2

3

4

5

6

7

A1

A2

A4

DI MUX

0

1

2

3

4

5

6

7

A1

A2

A4

E

Восьмиканальный

одноразрядный мультиплексор с инверсным выходом.

Имеет прямой

и

инверсн. выходы и

разрешающий вход Е.

Сигнал Е = 0 разреш.

работу

мультиплексора. При Е=1 все

каналы закрываются.

555КП1

DIA

0

1

2

3

DIB

0

1

2

3

A

OE

MUX

D0

0

1

2

3

Двухканальный 4-х

разрядный мультиплексор

с тремя

состояниями выхода.

ОЕ=0 разреш. Работу

мультиплексора.

ОЕ=1 – ТС выхода.

25.

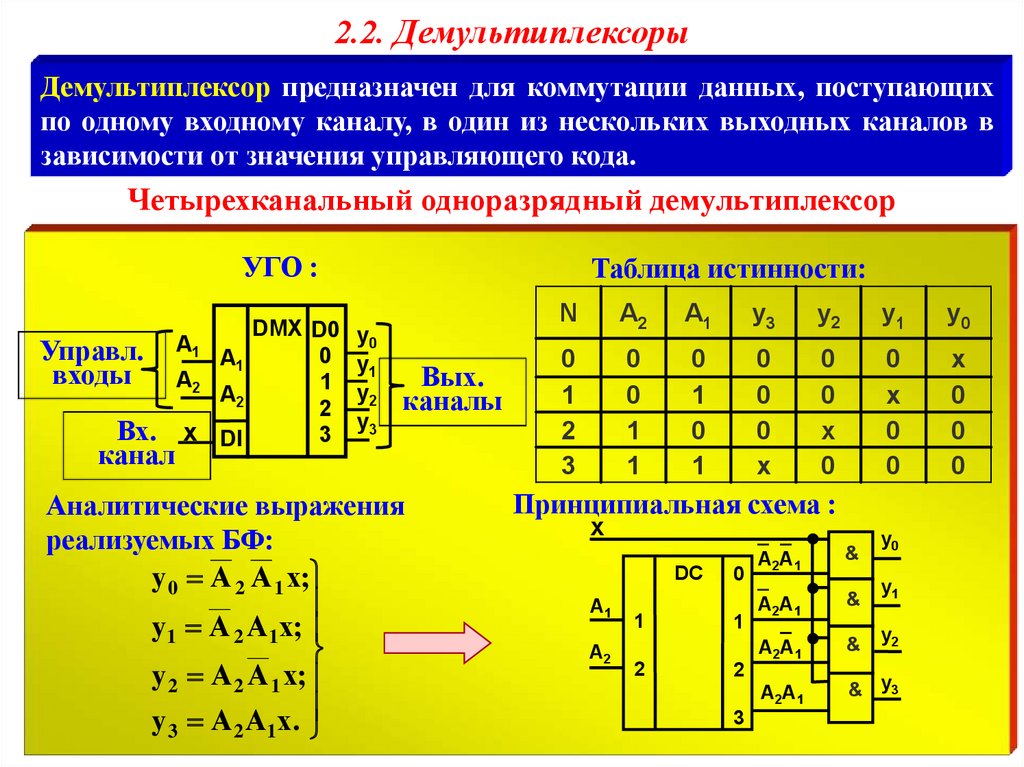

2.2. ДемультиплексорыДемультиплексор предназначен для коммутации данных, поступающих

по одному входному каналу, в один из нескольких выходных каналов в

зависимости от значения управляющего кода.

Четырехканальный одноразрядный демультиплексор

УГО :

Управл.

входы

Вх.

канал

DMX D0 y

0

A1

0 y

A1

1

A2

1 y

A2

2

2

y3

x DI

3

Таблица истинности:

Вых.

каналы

Аналитические выражения

реализуемых БФ:

y 0 А 2 А 1 х;

y 1 А 2 А1х;

y 2 А 2 А 1 х;

y 3 А 2 А1х.

N

А2

А1

y3

y2

y1

y0

0

1

2

3

0

0

1

1

0

1

0

1

0

0

0

x

0

0

x

0

0

x

0

0

x

0

0

0

Принципиальная схема :

x

DC

А1

А2

1

2

_ _

A2A1

0 _

A2A1

1

_

A2A1

2

A2A1

3

&

&

y0

y1

& y2

& y3

26.

Мультиплексоры коммутируют данные, поступающие понескольким входным каналам в один выходной канал, а

демультиплексоры

выполняют

противополож-ную

функцию.

27.

3. Сумматоры и арифметикологические устройства28.

НазначениеУГО и назначение выводов

Функции, реализуемые на выходах

Наращивание разрядности

Выводы по вопросу

29.

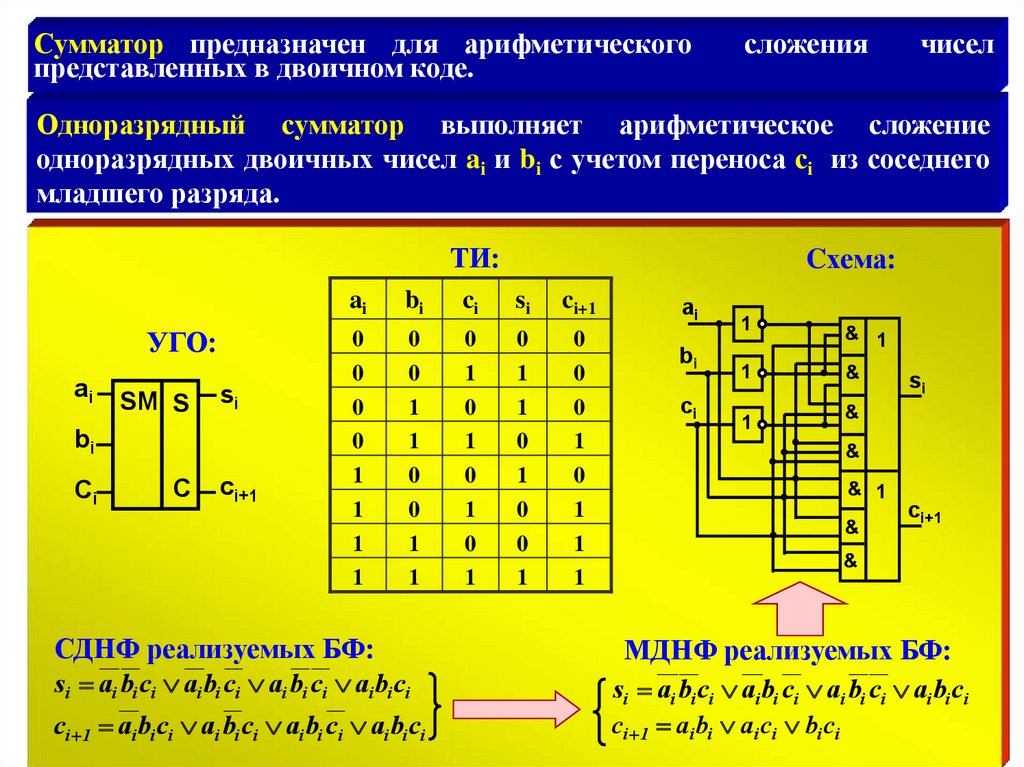

Сумматор предназначен для арифметическогопредставленных в двоичном коде.

сложения

чисел

Одноразрядный сумматор выполняет арифметическое сложение

одноразрядных двоичных чисел ai и bi с учетом переноса сi из соседнего

младшего разряда.

ТИ:

УГО:

ai

SM S

si

bi

Ci

C

ci+1

Cхема:

ai

bi

ci

si

ci+1

0

0

0

0

1

1

1

1

0

0

1

1

0

0

1

1

0

1

0

1

0

1

0

1

0

1

1

0

1

0

0

1

0

0

0

1

0

1

1

1

СДНФ реализуемых БФ:

si ai bi ci ai bi ci ai bi ci ai bi ci

сi 1 ai bi ci ai bi ci ai bi ci ai bi ci

ai

bi

ci

1

& 1

1

&

1

&

si

&

& 1

&

ci+1

&

МДНФ реализуемых БФ:

si ai bi ci ai bi ci ai bi ci ai bi ci

сi 1 ai bi ai ci bi ci

30.

Многоразрядный сумматор с последовательным переносом строится наоснове одноразрядных сумматоров путем соединения их по цепям

переноса.

Cхема:

c0

a0

b0

SM S

C

SM S

a1

b1

s0

C

s1

c2

Слагаемые А = aia0 и В = bib0 подаются

на вх. сумматора в параллельном коде, т.е

одновременно. На вых. сумматора

образуется сумма s = s1s0. Cигнал переноса последовательно распространяется

от младшего разряда к старшему. На

выходе с2

вырабатывается единица

переноса в следующий старший разряд.

УГО:

a0

a1

b0

b1

c0

A0

s

A1 SM S0 0

B0

B1

C0

S1

s1

C2

c2

Условные графические обозначения ИМС сумматоров

A0 SM S0

B0

С1

С0

A0

B0

С0

S0

С1

Сумматор 555ИМ5

содержит в одном

корпусе два независимых одноразрядных сумматора.

A0 SM S0

А1

S1

S2

А2

S3

A3

B0

В1

В2

В3

С0

C4

ИМС 133ИМЗ представляет собой четырехразрядный

сумматор

с

параллельным

переносом. Для наращивания

разрядности

используются выводы С0 и С4.

31.

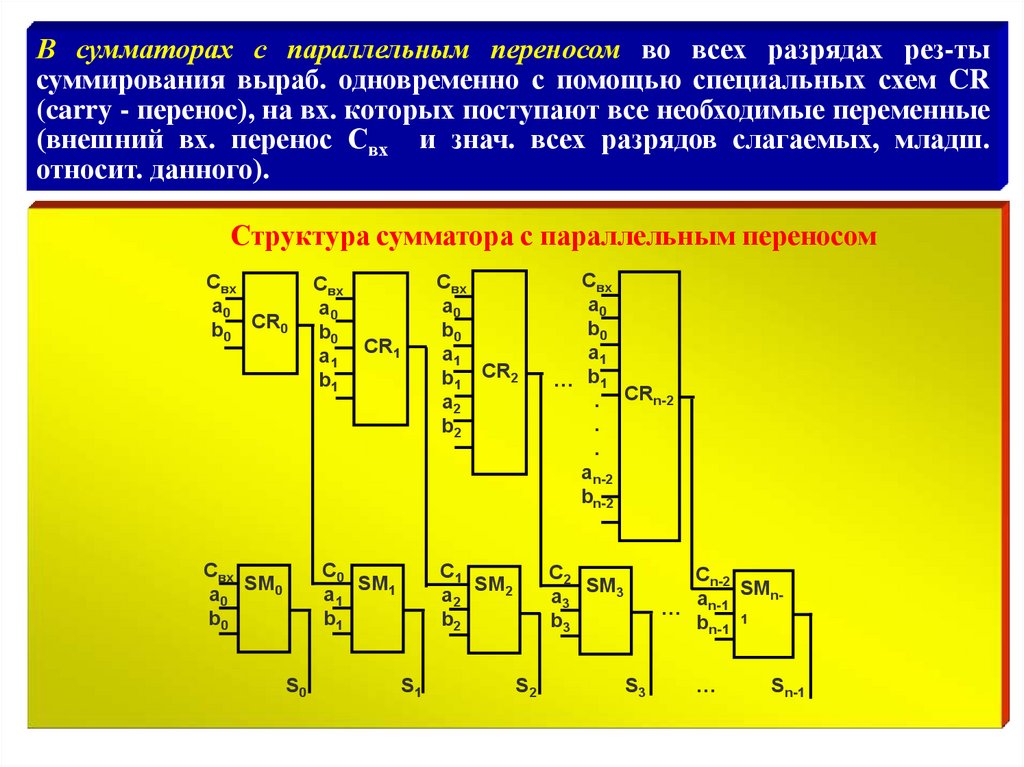

В сумматорах с параллельным переносом во всех разрядах рез-тысуммирования выраб. одновременно с помощью специальных схем CR

(carry - перенос), на вх. которых поступают все необходимые переменные

(внешний вх. перенос Свх и знач. всех разрядов слагаемых, младш.

относит. данного).

Структура сумматора с параллельным переносом

Свх

a0

b0 СR0

Свх

SM0

a0

b0

S0

СR1

Свх

a0

b0

a1

b1 СR2

a2

b2

Свх

a0

b0

a1

… b1

. СRn-2

.

.

an-2

bn-2

С0

SM1

a1

b1

С1

SM2

a2

b2

С2

SM3

a3

b3

Свх

a0

b0

a1

b1

S1

S2

Сn-2

SMna

n-1

…

bn-1 1

S3

…

Sn-1

32.

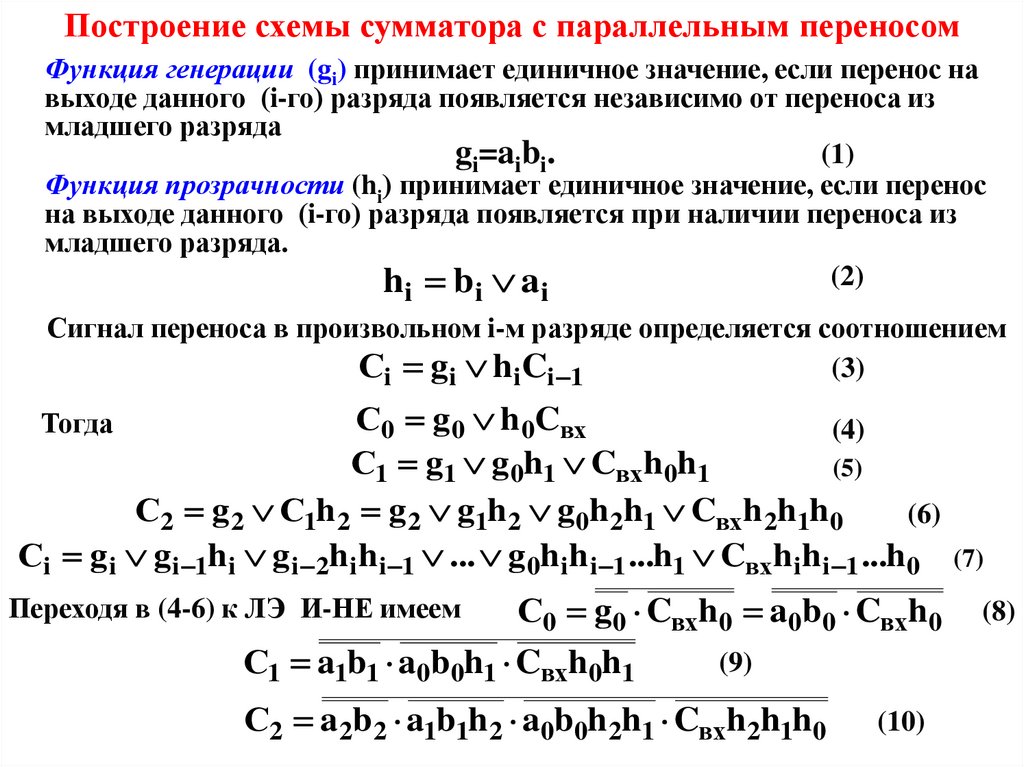

Построение схемы сумматора с параллельным переносомФункция генерации (gi) принимает единичное значение, если перенос на

выходе данного (i-го) разряда появляется независимо от переноса из

младшего разряда

gi=aibi.

(1)

Функция прозрачности (hi) принимает единичное значение, если перенос

на выходе данного (i-го) разряда появляется при наличии переноса из

младшего разряда.

(2)

h b a

i

i

i

Сигнал переноса в произвольном i-м разряде определяется соотношением

(3)

Сi g i hiCi 1

С0 g 0 h 0Cвх

(4)

С1 g1 g 0h1 Cвхh 0h1

(5)

С2 g 2 С1h 2 g 2 g1h 2 g 0h 2h1 Cвхh 2h1h 0

(6)

Сi g i g i 1h i g i 2h i h i 1 ... g 0h i h i 1 ...h1 Cвхh i h i 1 ...h 0

Тогда

С0 g 0 Cвхh0 a0b0 Cвхh0

(9)

С1 a1b1 a0b0h1 Cвхh0h1

Переходя в (4-6) к ЛЭ И-НЕ имеем

С2 a 2b 2 a1b1h 2 a0b0h 2h1 Cвхh 2h1h0

(10)

(7)

(8)

33.

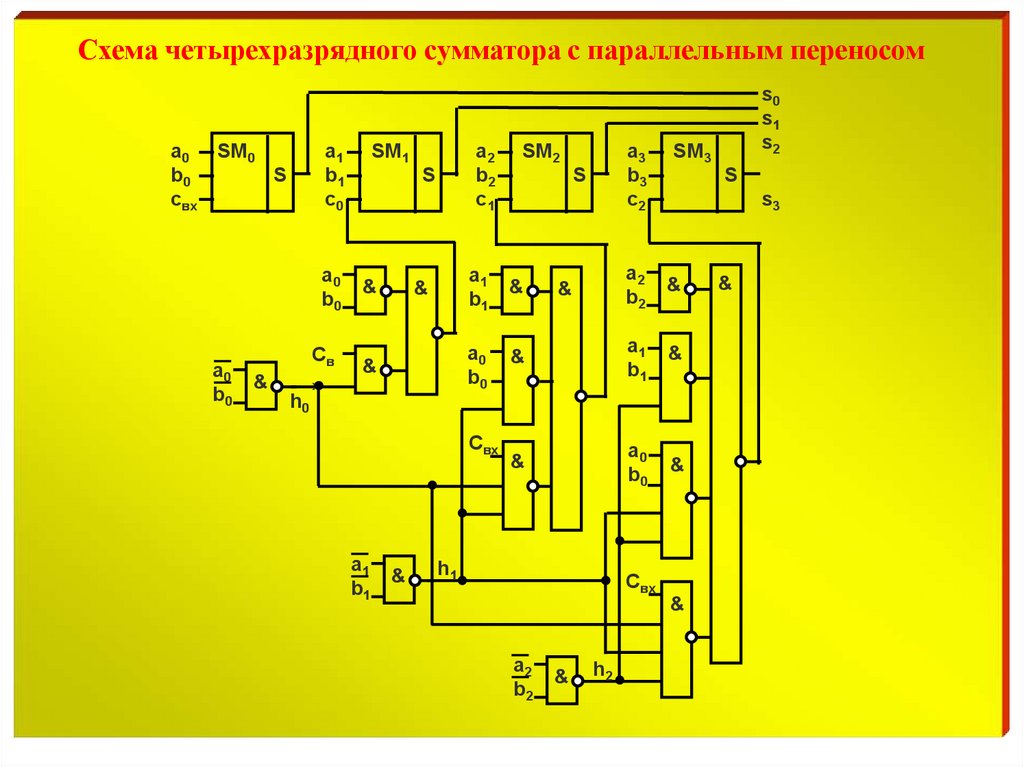

Схема четырехразрядного сумматора с параллельным переносомa0 SM0

b0

S

cвх

a1

b1

c0

a0

b0

a0

b0

Св

&

SM1

a2

b2

c1

S

&

a1

b1

&

a0

b0

&

х

SM2

a3

b3

c2

S

SM3

S

s3

a2

b2

&

&

a1

b1

&

&

a0

b0

&

&

&

h0

Свх

a1

b1

&

h1

Свх

&

a2

b2

&

h2

s0

s1

s2

&

34.

Арифметическо-логические устройства (АЛУ)АЛУ предназначены для выполнения арифметических и логических

операций над двумя многоразрядными словами (операндами).

Вход для учёта

сигналов переноса из

младших разрядов

1-й операнд

А={а3,а2 ,а1,а0}

2-й операнд

В={b3,b2 ,b1,b0}

Выбор выполняемой

операции (код упр.)

S={S3,S2 ,S1,S0}

Тип выполняемой

операции:

М=1- логические;

М=0 – арифметикологические

ИМС АЛУ К155ИП3

C0

ALU

C4

a0

a1

a2

a3

G

b0

b1

b2

b3

f0

f1

f2

f3

s0

s1

s2

s3

A=B

M

H

Выход для учёта сигналов

переноса в старшие разряды

функции G и H, для

организации параллельных

переносов

Результат операции

F={f3,f2 ,f1,f0}

Выход сравнения на

равенство с открытым

коллектором.

35.

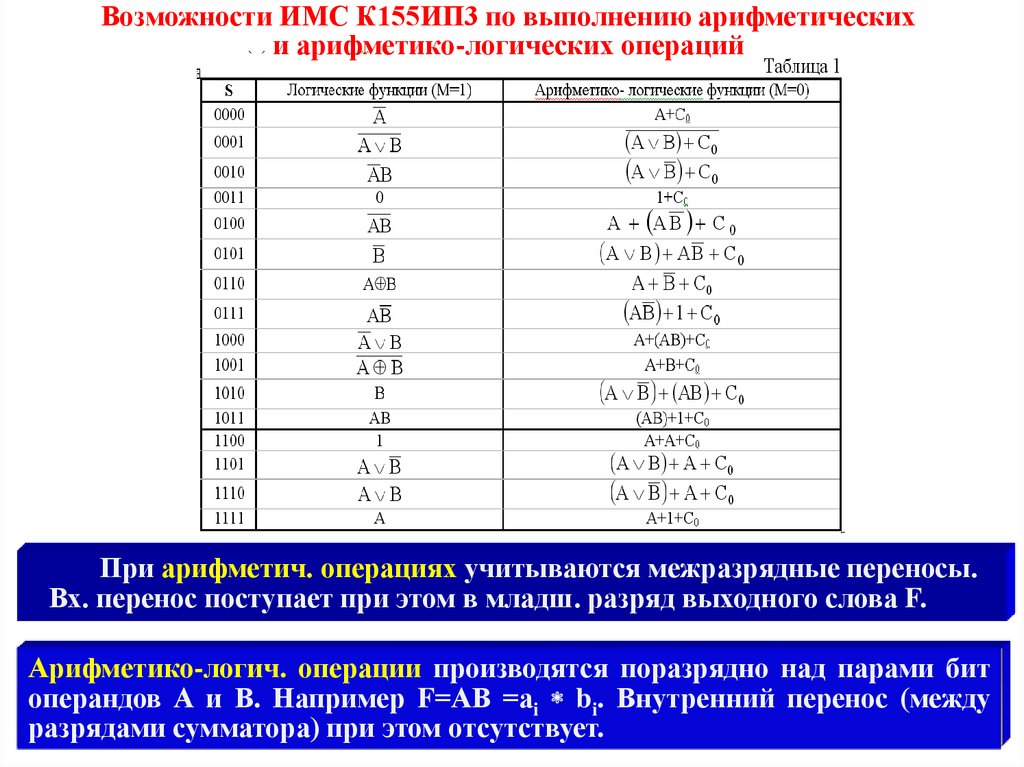

Возможности ИМС К155ИП3 по выполнению арифметическихи арифметико-логических операций

При арифметич. операциях учитываются межразрядные переносы.

Вх. перенос поступает при этом в младш. разряд выходного слова F.

Арифметико-логич. операции производятся поразрядно над парами бит

операндов А и В. Например F=АВ =аi bi. Внутренний перенос (между

разрядами сумматора) при этом отсутствует.

36.

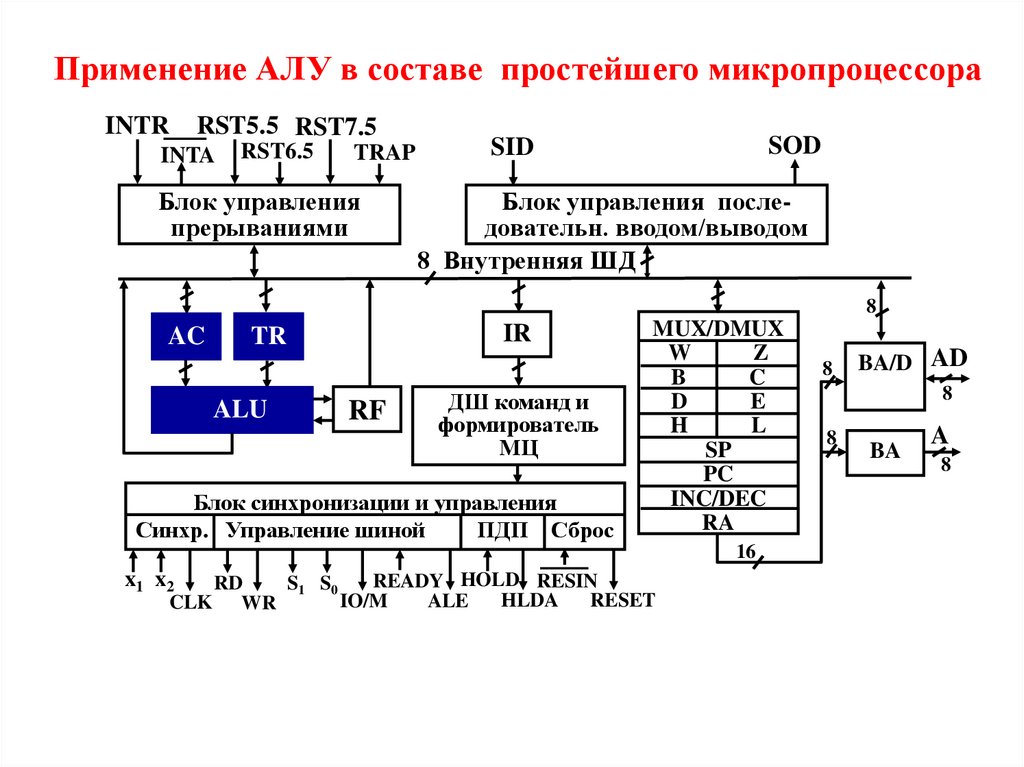

Применение АЛУ в составе простейшего микропроцессораINTR

RST5.5 RST7.5

INTA

RST6.5

TRAP

Блок управления

прерываниями

SOD

SID

Блок управления последовательн. вводом/выводом

8 Внутренняя ШД

8

AC

IR

TR

ALU

RF

ДШ команд и

формирователь

МЦ

Блок синхронизации и управления

Синхр. Управление шиной

ПДП Сброс

MUX/DMUX

W

Z

B

C

D

E

H

L

SP

PC

INC/DEC

RA

16

x1 x2

CLK

READY HOLD RESIN

RD

S1 S0

RESET

HLDA

IO/M

ALE

WR

8

BA/D AD

8

8

BA

A

8

37.

Сумматоры служат для арифметического сложениядвоичных чисел. Многоразрядные сумматоры строятся

на основе одноразрядных. Наибольшим быстродействием обладают сумматоры с параллельным

переносом, однако они имеют наиболее сложную схему.

Арифметико-логические

устройства

наряду

с

арифметическими операциями способны выполнять

логические операции

38.

4. Схемы контроля четности39.

НазначениеСущность метода контроля по М2

Схема контроля четности свертки по М2

Пример применения схемы контроля

четности

Выводы по вопросу

40.

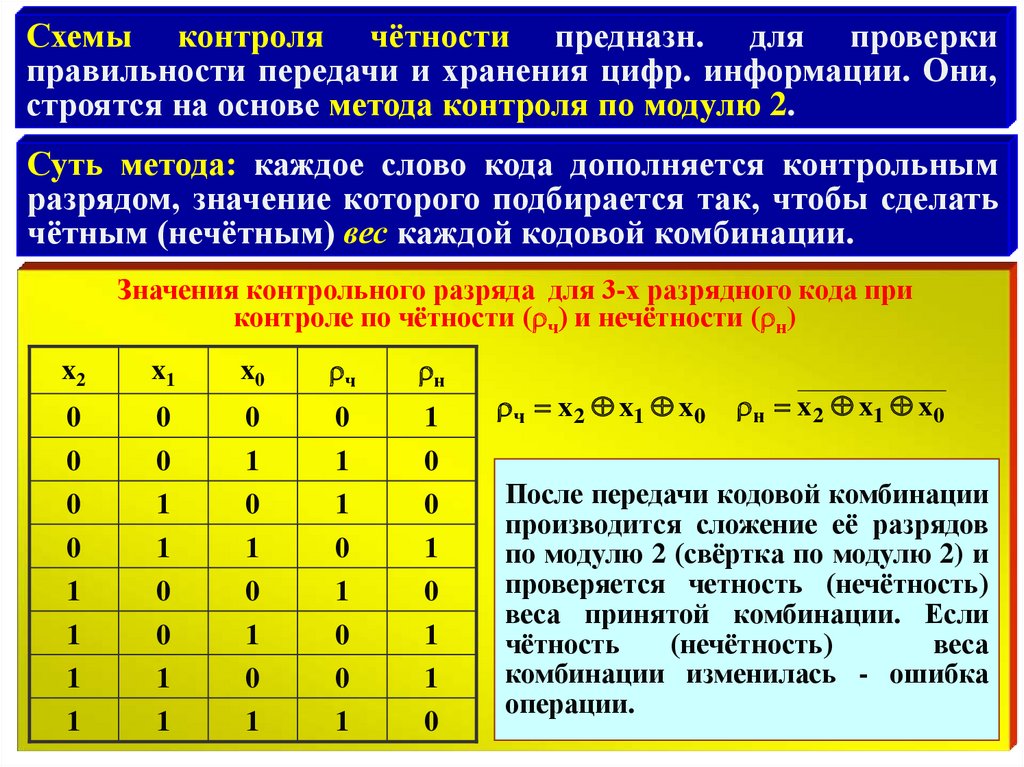

Схемы контроля чётности предназн. для проверкиправильности передачи и хранения цифр. информации. Они,

строятся на основе метода контроля по модулю 2.

Суть метода: каждое слово кода дополняется контрольным

разрядом, значение которого подбирается так, чтобы сделать

чётным (нечётным) вес каждой кодовой комбинации.

Значения контрольного разряда для 3-х разрядного кода при

контроле по чётности (rч) и нечётности (rн)

x2

x1

x0

rч

rн

0

0

0

0

1

0

0

1

1

0

0

1

0

1

0

0

1

1

0

1

1

0

0

1

0

1

0

1

0

1

1

1

0

0

1

1

1

1

1

0

rч x 2 x1 x0

rн x 2 x1 x 0

После передачи кодовой комбинации

производится сложение её разрядов

по модулю 2 (свёртка по модулю 2) и

проверяется четность (нечётность)

веса принятой комбинации. Если

чётность

(нечётность)

веса

комбинации изменилась - ошибка

операции.

41.

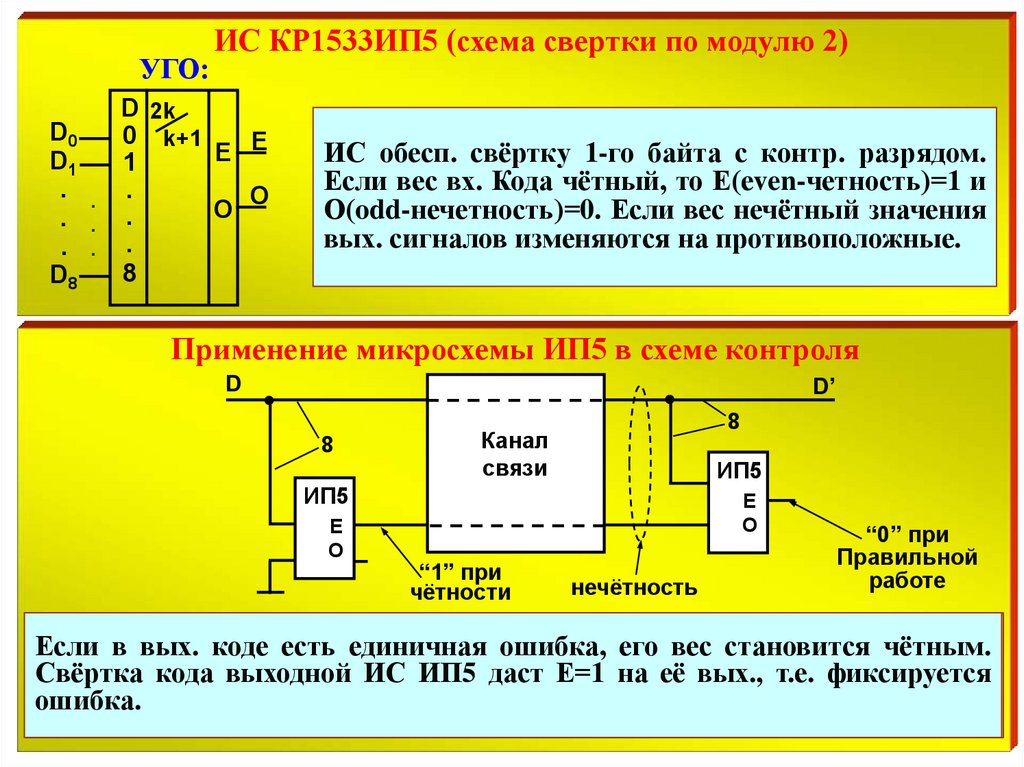

УГО:D0

D1

.

.

.

D8

.

.

.

ИС КР1533ИП5 (схема свертки по модулю 2)

D 2k

0 k+1

Е

Е

1

.

О

О

.

.

8

ИС обесп. свёртку 1-го байта с контр. разрядом.

Если вес вх. Кода чётный, то Е(еven-четность)=1 и

О(odd-нечетность)=0. Если вес нечётный значения

вых. сигналов изменяются на противоположные.

Применение микросхемы ИП5 в схеме контроля

D’

D

8

8

Канал

связи

ИП5

ИП5

Е

О

Е

О

“1” при

чётности

нечётность

“0” при

Правильной

работе

Вх. ИС

ИП5 коде

форм.

сигнал

в 9-м ошибка,

контр. разряде

т.о.,

чтобы вес

9-ти

Если

в

вых.

есть

единичная

его

вес

становится

чётным.

разрядного

вх.выходной

кода был нечётным.

Если

в вых.

коде

нетт.е.

ошибок,

его вес

Свёртка

кода

ИС

ИП5

даст

Е=1

на

её

вых.,

фиксируется

остаётся нечётным. Свёртка по модулю 2 такого кода выходной ИС ИП5

ошибка.

даст Е=0 на её вых., т.е. ошибка отсутствует.

42.

5. Методы расчета типовыхкомбинационных цифровых

устройств

43.

НазначениеМетодика построения и расчета

устройства дешифрации кодов

Методика построения и расчета

коммутатора параллельных кодов

Выводы по вопросу

44.

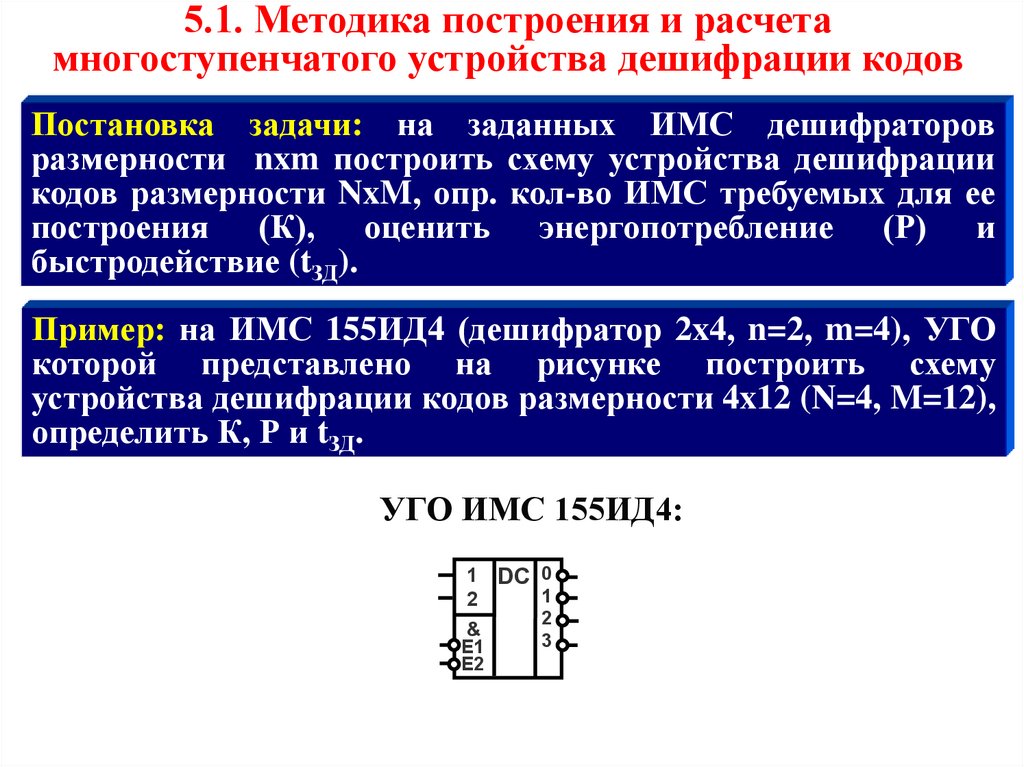

5.1. Методика построения и расчетамногоступенчатого устройства дешифрации кодов

Постановка задачи: на заданных ИМС дешифраторов

размерности nxm построить схему устройства дешифрации

кодов размерности NxM, опр. кол-во ИМС требуемых для ее

построения (К), оценить энергопотребление (Р) и

быстродействие (tЗД).

Пример: на ИМС 155ИД4 (дешифратор 2x4, n=2, m=4), УГО

которой представлено на рисунке построить схему

устройства дешифрации кодов размерности 4x12 (N=4, M=12),

определить К, Р и tЗД.

УГО ИМС 155ИД4:

1 DC 0

1

2

&

E1

E2

2

3

45.

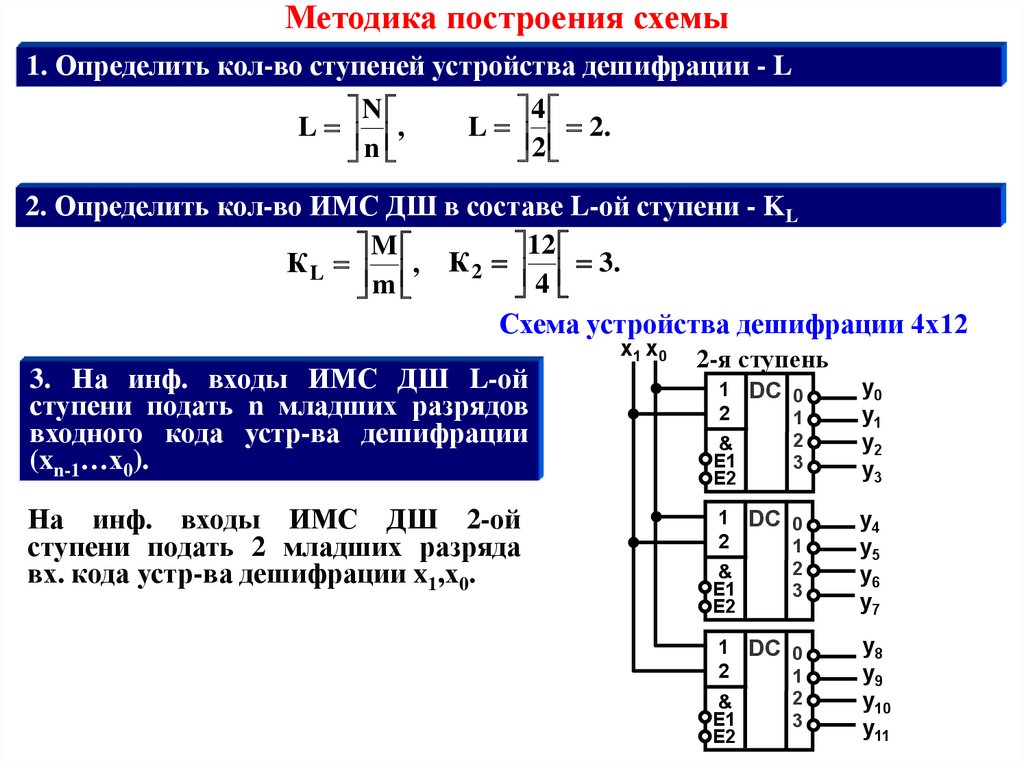

Методика построения схемы1. Определить кол-во ступеней устройства дешифрации - L

4

N

L 2.

L ,

n

2

2. Определить кол-во ИМС ДШ в составе L-ой ступени - KL

12

M

К

3.

К L ,

2

4

m

Схема устройства дешифрации 4х12

3. На инф. входы ИМС ДШ L-ой

ступени подать n младших разрядов

входного кода устр-ва дешифрации

(xn-1…х0).

На инф. входы ИМС ДШ 2-ой

ступени подать 2 младших разряда

вх. кода устр-ва дешифрации x1,х0.

x1 x0

2-я ступень

1 DC 0

2

1

2

&

E1

E2

3

1 DC 0

2

1

&

E1

E2

2

3

1 DC 0

2

1

2

&

E1

E2

3

y0

y1

y2

y3

y4

y5

y6

y7

y8

y9

y10

y11

46.

Методика построения схемы (продолжение)Схема устройства дешифрации 4х12

x 1 x0

2-я ступень

1 DC 0

2

1

x2

x3

1 DC 0

2

1

&

E1

E2

2

3

&

E1

E2

2

3

1 DC 0

2

1

2

&

E1

E2

3

1 DC 0

2

1

&

E1

E2

2

3

y0

y1

y2

y3

y4

y5

y6

y7

y8

y9

y10

y11

4. Определить

количество

ИМС ДШ в составе (L-1)-ой

ступени – KL-1.

K

3

K

К L 1 L , К 1 2 1.

m 4

m

5. На инф. вх. ИМС ДШ (L-1)-ой ступени подать следующие n младших

разрядов вх. кода устройства дешифрации (x2n-1…хn). Инф. выходы ДШ

(L-1)-ой ступени подкл. к разрешающим входам ДШ L-ой ступени

На инф. вх. ИМС ДШ 1-ой ступени подать следующие 2 мл. разряда вх.

кода - x3,х2. Инф. выходы ДШ 1-ой ступени подкл. к разрешающим входам

ДШ 2-ой ступени

47.

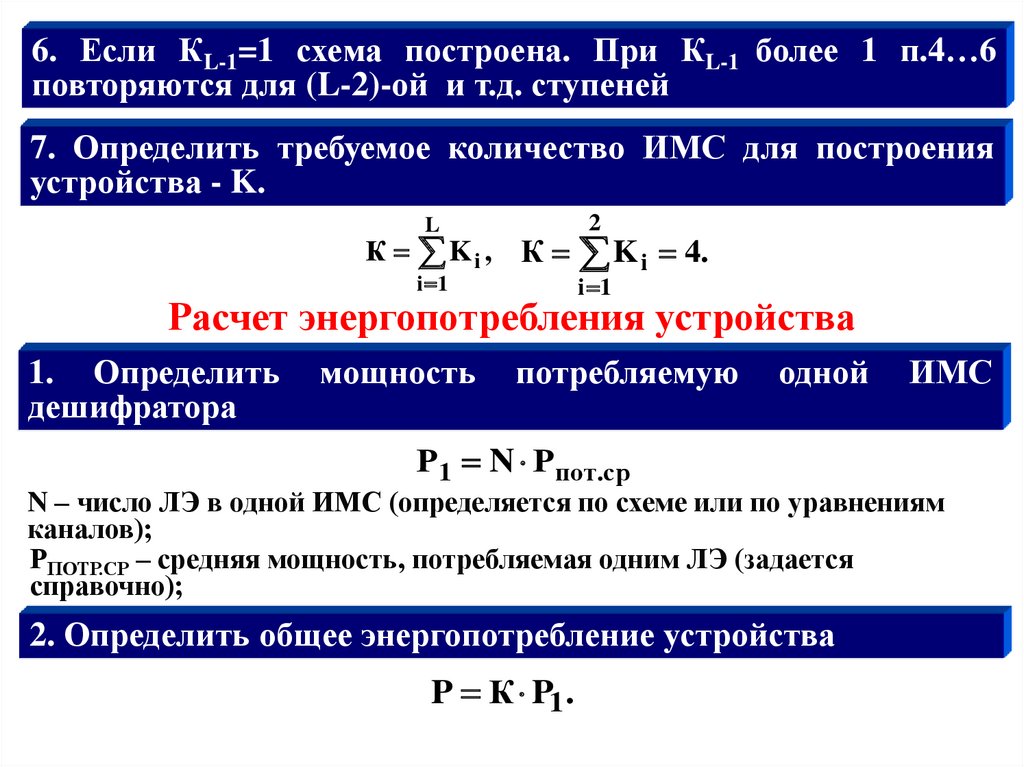

6. Если КL-1=1 схема построена. При КL-1 более 1 п.4…6повторяются для (L-2)-ой и т.д. ступеней

7. Определить требуемое количество ИМС для построения

устройства - K.

К

L

2

i 1

i 1

K i , К K i 4.

Расчет энергопотребления устройства

1. Определить

дешифратора

мощность

потребляемую

одной

Р1 N Р пот .ср

ИМС

N – число ЛЭ в одной ИМС (определяется по схеме или по уравнениям

каналов);

РПОТР.СР – средняя мощность, потребляемая одним ЛЭ (задается

справочно);

2. Определить общее энергопотребление устройства

P К P1 .

48.

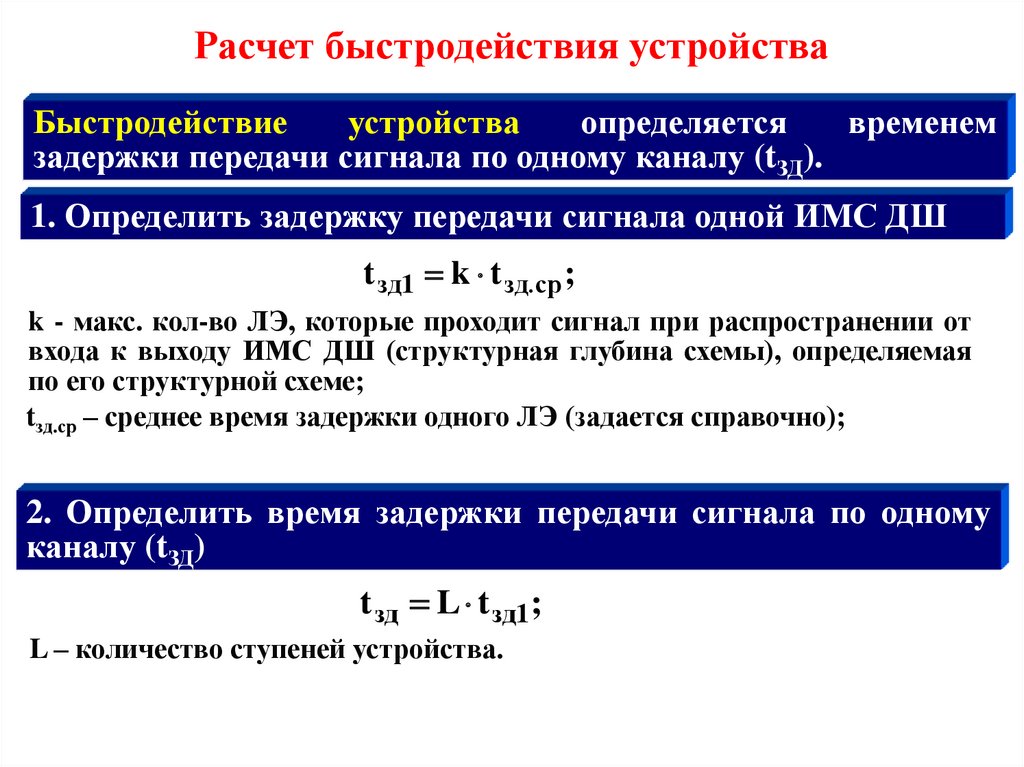

Расчет быстродействия устройстваБыстродействие

устройства

определяется

временем

задержки передачи сигнала по одному каналу (tЗД).

1. Определить задержку передачи сигнала одной ИМС ДШ

t зд1 k t зд.ср ;

k - макс. кол-во ЛЭ, которые проходит сигнал при распространении от

входа к выходу ИМС ДШ (структурная глубина схемы), определяемая

по его структурной схеме;

tзд.ср – среднее время задержки одного ЛЭ (задается справочно);

2. Определить время задержки передачи сигнала по одному

каналу (tЗД)

t зд L t зд1;

L – количество ступеней устройства.

49.

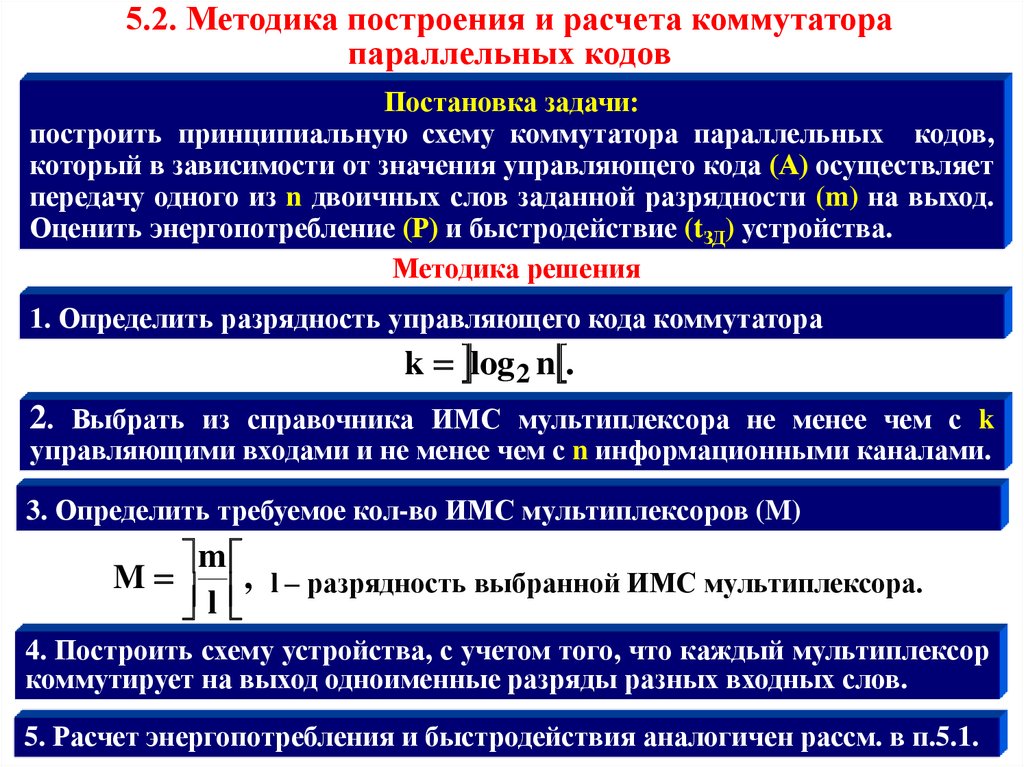

5.2. Методика построения и расчета коммутаторапараллельных кодов

Постановка задачи:

построить принципиальную схему коммутатора параллельных кодов,

который в зависимости от значения управляющего кода (А) осуществляет

передачу одного из n двоичных слов заданной разрядности (m) на выход.

Оценить энергопотребление (Р) и быстродействие (tЗД) устройства.

Методика решения

1. Определить разрядность управляющего кода коммутатора

k log 2 n .

2. Выбрать из справочника ИМС мультиплексора не менее чем с k

управляющими входами и не менее чем с n информационными каналами.

3. Определить требуемое кол-во ИМС мультиплексоров (M)

m

M , l – разрядность выбранной ИМС мультиплексора.

l

4. Построить схему устройства, с учетом того, что каждый мультиплексор

коммутирует на выход одноименные разряды разных входных слов.

5. Расчет энергопотребления и быстродействия аналогичен рассм. в п.5.1.

50.

Пример: построить схему коммутатора параллельных кодов, который взависимости от значения управляющего кода (А) передает одного из 4-х

(n=4) 2-х разрядных (m=2) двоичных слов (B,C,D,E) на выход (F).

Схема четырехканального двухразрядного коммутатора

k log 2 4 2.

DI

B

b1

b0

C

c1

c0

ИМС – 155КП2

2

M 2.

l

D

E

A

d1

d0

MUX

0

1

2

3

f1

f0

A1

A2

E

e1

e0

DI

a1

a2

A1

A2

0

1

2

3

E

MUX

F

51.

1. Отработать лекцию, используя:эл.1/о м.2.2;

л.1/д с.44-55, 96-108;

л.2/д с.540-553, 621-626.

Основное внимание обратить на назначение и принцип

функционирования рассмотренных цифровых узлов и

устройств комбинационного типа.

2. Быть готовыми к практическому занятию № 2 на тему

«Анализ и расчет типовых комбинационных цифровых

узлов ЭВМ».

Электроника

Электроника