Похожие презентации:

Цифровые устройства и микропроцессоры. Тема 1. Основы схемотехники и элементная база цифровых электронных устройств

1.

ВОЕННАЯ АКАДЕМИЯ ВОЗДУШНО-КОСМИЧЕСКОЙ ОБОРОНЫимени МАРШАЛА СОВЕТСКОГО СОЮЗА Г.К. ЖУКОВА

Кафедра основ построения радиоэлектронных средств и систем

Учебная дисциплина ДС-1321

«ЦИФРОВЫЕ УСТРОЙСТВА И

МИКРОПРОЦЕССОРЫ»

Тверь 2020

2.

СТРУКТУРА УЧЕБНОЙ ДИСЦИПЛИНЫ ДС-1321Номера и наименование

разделов и тем

Всего

часов

Из них по видам занятий

Лекции Лаб.раб. Пр.зан.

Зачет

5 семестр

Введение

2

2

Тема 1. Основы схемотехники и элементная база

комбинационных цифровых электронных

устройств

14

6

4

4

Тема 2. Основы схемотехники и элементная база

последовательностных цифровых электронных

устройств

24

10

8

6

Тема 3. Аналого-цифровые и цифро-аналоговые 10

преобразователи

4

4

2

Тема 4. Запоминающие устройства ЭВМ и МПС

8

4

2

2

Тема 5. Микропроцессоры и микропроцессорные

системы

26

16

Заключение

2

2

Зачет с оценкой в конце 5-го семестра

4

Всего по дисциплине

90

10

4

44

18

24

4

3.

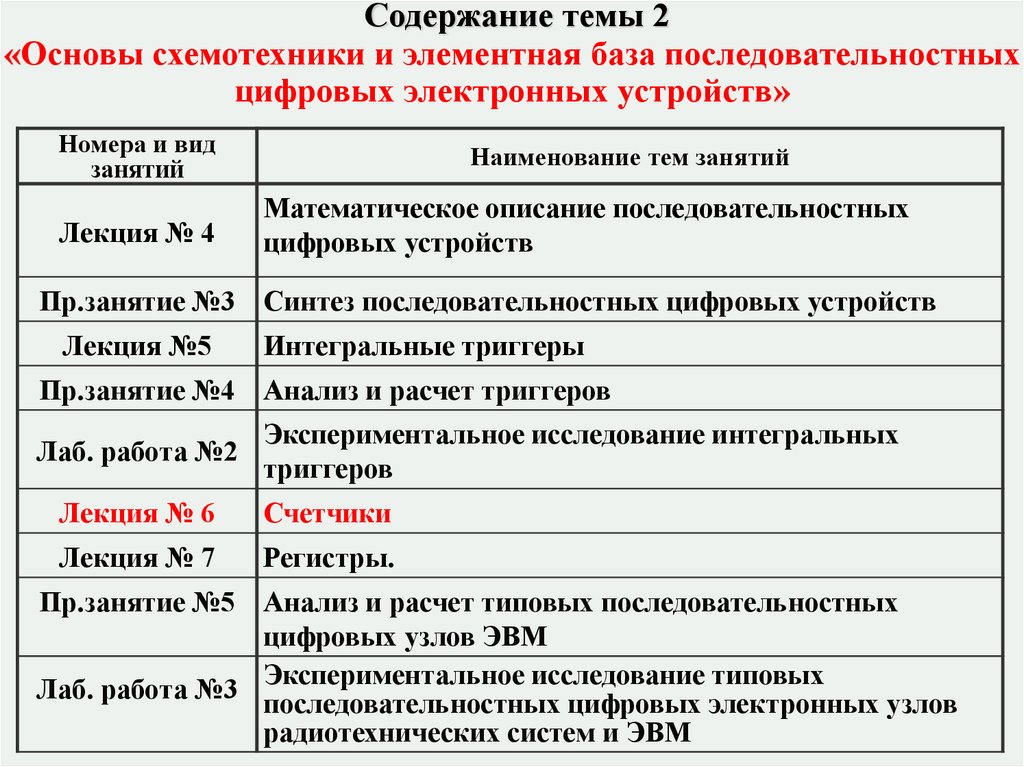

Содержание темы 2«Основы схемотехники и элементная база последовательностных

цифровых электронных устройств»

Номера и вид

занятий

Лекция № 4

Наименование тем занятий

Математическое описание последовательностных

цифровых устройств

Пр.занятие №3 Синтез последовательностных цифровых устройств

Лекция №5

Интегральные триггеры

Пр.занятие №4 Анализ и расчет триггеров

Лаб. работа №2

Экспериментальное исследование интегральных

триггеров

Лекция № 6

Счетчики

Лекция № 7

Регистры.

Пр.занятие №5 Анализ и расчет типовых последовательностных

цифровых узлов ЭВМ

исследование типовых

Лаб. работа №3 Экспериментальное

последовательностных цифровых электронных узлов

радиотехнических систем и ЭВМ

4.

Лекция № 7РЕГИСТРЫ

5.

ФОРМИРУЕМАЯ КОМПЕТЕНЦИЯСпособность учитывать в профессиональной деятельности

современные

тенденции

развития

электроники,

измерительной и вычислительной техники (ПК-7).

ПЛАНИРУЕМЫЕ РЕЗУЛЬТАТЫ ОБУЧЕНИЯ

ЗНАТЬ:

принципы построения, функционирование и основные

параметры, типовых цифровых узлов и устройств, цифроаналоговых и аналого-цифровых преобразователей;

УЧЕБНАЯ ЦЕЛЬ ЛЕКЦИИ

Систематизировать основы научных знаний по цифровым

устройствам, рассмотрев принципы построения и

функционирование и параметры основных разновидностей

регистров.

6.

УЧЕБНЫЕ ВОПРОСЫ ЛЕКЦИИ1. Общие сведения о регистрах.

2. Основные типы регистров.

7.

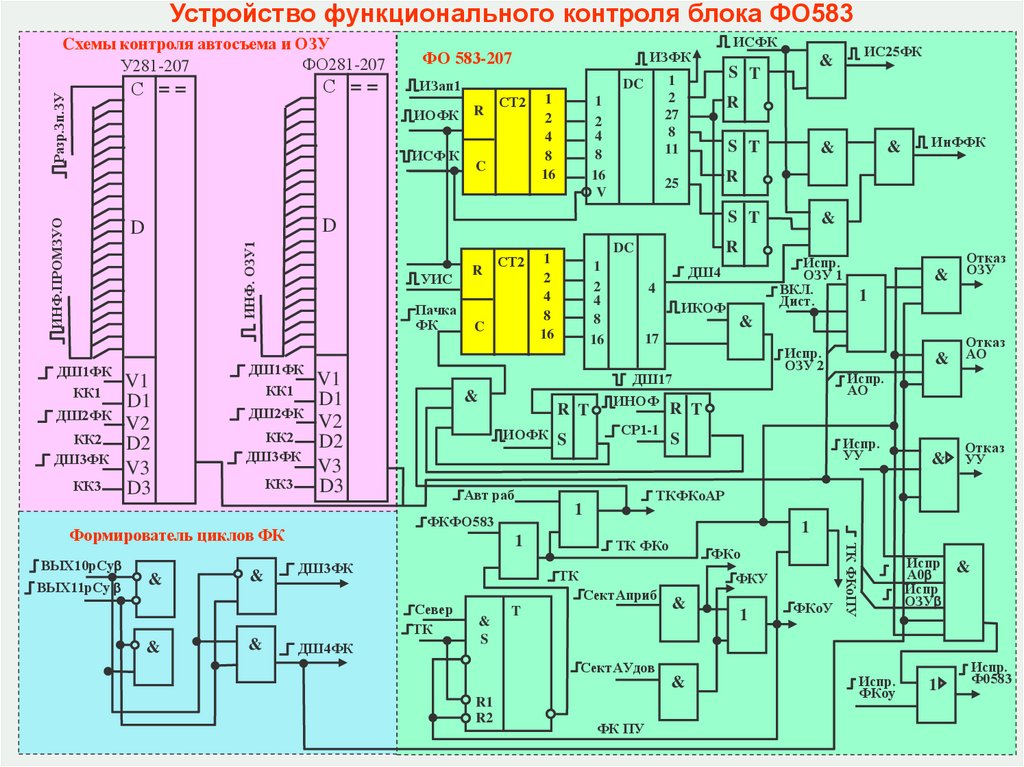

Устройство функционального контроля блока ФО583Cхемы контроля автосъема и ОЗУ

ФО281-207

У281-207

С ==

Разр.Зп.ЗУ

С ==

ФО 583-207

ИЗап1

ИОФК

ИНФ.ПРОМЗУО

ИСФ К

ИНФ. ОЗУ1

ДШ2ФК

КК2

ДШ3ФК

КК3

S T

V1

D1

V2

D2

V3

D3

Пачка

ФК

ДШ1ФК

КК1

ДШ2ФК

КК2

ДШ3ФК

КК3

V1

D1

V2

D2

V3

D3

&

&

&

C

1

2

4

8

16

ИОФК

4

ИКОФ

СР1-1

S

Испр.

ОЗУ 2

Отказ

& АО

Испр.

АО

R T

S

ТК ФКо

Испр.

УУ

ФКо

ТК

ФКУ

СектАприб

T

&

СектАУдов

&

R1

R2

1

&

Отказ

УУ

1

1

&

S

Отказ

ОЗУ

ТКФКоАР

1

ДШ3ФК

&

&

17

ИНОФ

&

Испр.

ОЗУ 1

ВКЛ.

Дист.

ДШ4

Авт раб

ФКФО583

ДШ4ФК

R

ДШ17

R T

ИнФФК

R

25

DC

1

2

4

8

16

&

Север

ТК

&

R

СТ2

&

&

ФК ПУ

1

ФКоУ

ТК ФКоПУ

ВЫХ11рСу

R

S T

УИС

Формирователь циклов ФК

ВЫХ10рСу

C

1

2

4

8

16

V

D

D

ДШ1ФК

КК1

СТ2

1

2

4

8

16

ИС25ФК

&

S T

1

2

27

8

11

DC

R

ИСФК

ИЗФК

Испр.

ФКоу

Испр

А0

Испр

ОЗУ

1

&

Испр.

Ф0583

8.

ЛИТЕРАТУРАЦифровые

устройства

и

микропроцессоры

[Электронный ресурс] : Учебное пособие/ Жидков Е.Н. и

[др.].

Тверь:

ВА

ВКО,

2016.

URL:

http://ibook.akademy.org/book/46.

(ЭЛ.1/о м.3.4)

2. Цифровые устройства и микропроцессоры. Учебнометодическое пособие./ Е.Н.Жидков, [ и др.]. Тверь: ВА

ВКО., 2019 168с.

(Л.1/д,с.80-85)

3. Цифровые устройства: Учеб.пособие для вузов / Ю.А.

Браммер, И.Н. Пащук. - М.: Высш. шк., 2004.

(\\10.55.13.1\учебные

пособия\13

кафедра\ДС1321\дополнительная литература\л2_д.pdf)

(Л.2/д,с. 89-94)

1.

9.

1. Общие сведения орегистрах

10.

Определение регистраКлассификация

регистров

Выводы по вопросу

11.

Регистром называется цифровое устройство, предназначенное дляприёма, хранения и выдачи двоично-кодированной информации.

Количество триггеров (n) в регистре называют его разрядностью.

Классификация регистров

По способу хранения и выдачи информации:

параллельного действия (памяти), в которых приём и выдача

информации осуществляется параллельным кодом;

последовательного действия (сдвигающие), в которых приём и выдача

информации производится последовательным кодом;

комбинированные, в которых сочетаются возможности регистров

последовательного и параллельного действия.

По количеству информационных каналов:

Парафазные - приём и выдача информации производится по двум

каналам - прямому и инверсному,

Однофазные - по одному прямому каналу.

По направлению сдвига информации:

со сдвигом вправо (в сторону младших разрядов),

со сдвигом влево (в сторону старших разрядов)

реверсивные, обладающие возможностью сдвига и вправо, и влево.

12.

Регистромназывается

цифровое

устройство,

предназначенное для приёма, хранения и выдачи

двоично-кодированной

информации.

Способность

регистров хранить информацию обусловлена тем, что

они строятся на триггерах

13.

2. Основные типы регистров14.

Регистры параллельного действия(памяти)

Регистры последовательного

действия (сдвига)

Реверсивные регистры

Комбинированные регистры

Выводы по вопросу

15.

2.1. Регистры памятиВ регистрах памяти триггеры информационно не связаны друг с

другом, а имеют только общие цепи управления

Парафазный регистр памяти

на RS-триггерах

Схема:

УГО:

D0

D RG Q

D0

D0

D1

D1

C

Q0

0

1

C

0

1

Однофазный регистр памяти

на D-триггерах

Q0

Q1

Q1

S

Т

Q0

R

S

Т

Q0

Q1

C

D1

R

D1

C

Q1

C

По фронту синхроимпульса в регистр

принимается парафазный двоичный код,

действующий на информационных входах. По срезу этого импульса регистр переходит в режим хранения информации.

D0

D RG Q

D0

C

D0

D1

Схема:

УГО:

0

1

0

1

D

Т

Q0

Q0

Q1

D1

C

D

Т

Q1

C

C

C

По фронту синхроимпульса в регистр

принимается однофазный двоичный код,

действующий на информационных входах. По срезу этого импульса регистр переходит в режим хранения информации.

16.

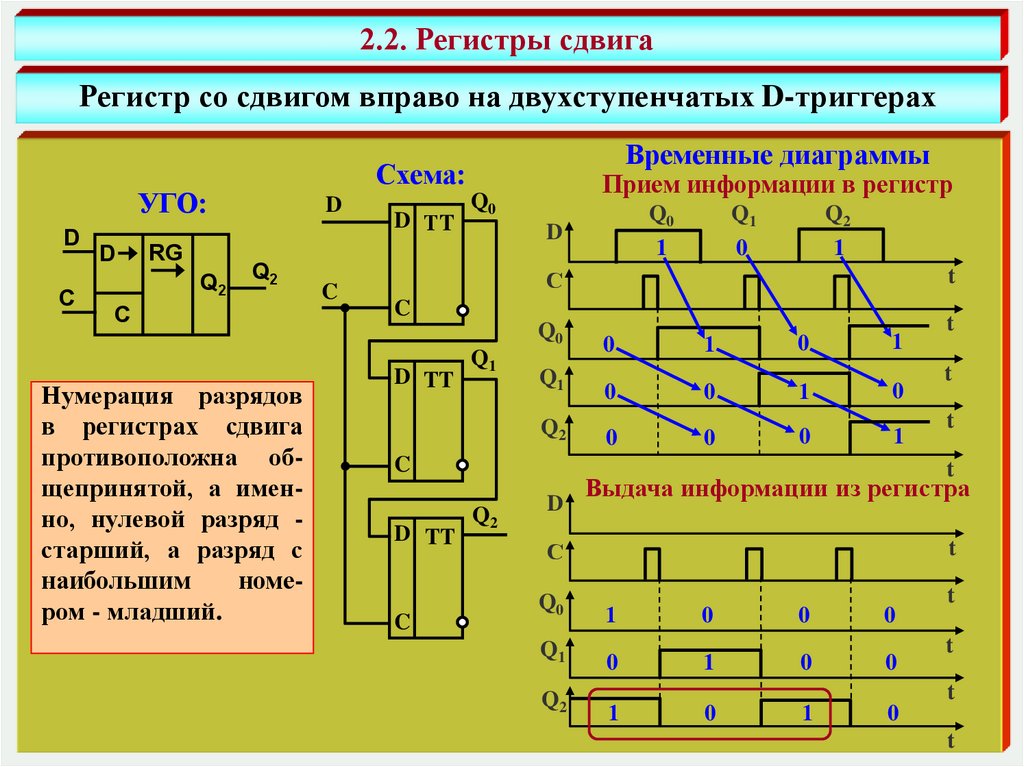

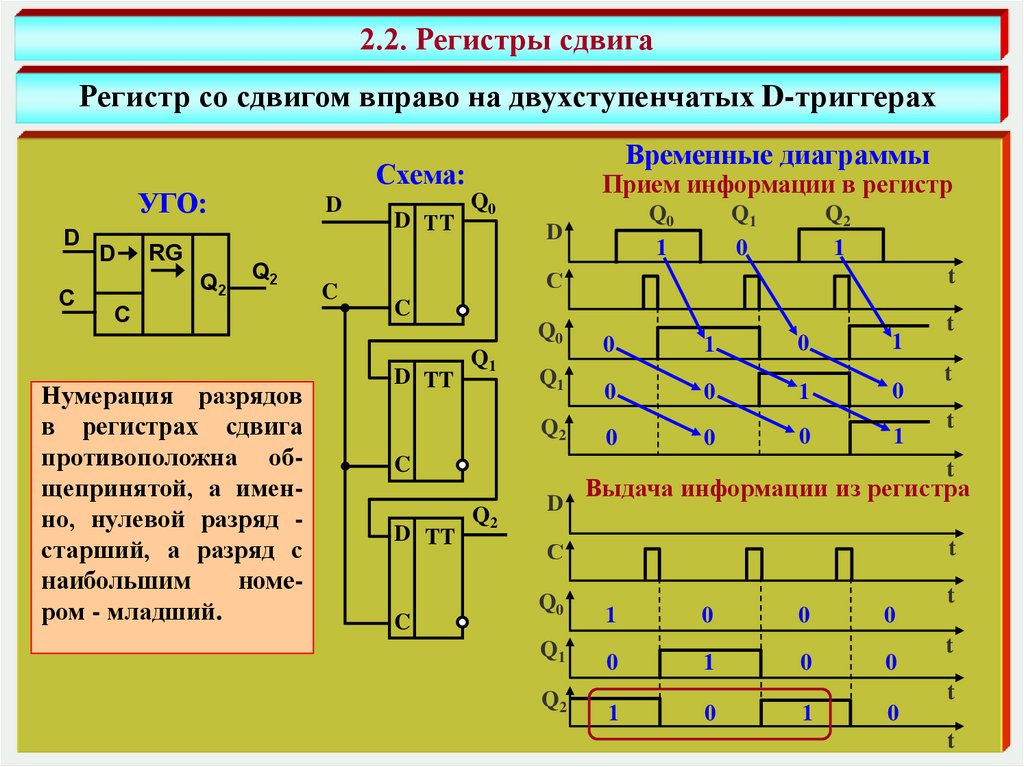

2.2. Регистры сдвигаРегистр со сдвигом вправо на двухступенчатых D-триггерах

УГО:

D

C

D

RG

Q2

Временные диаграммы

Схема:

D

Q2

C

Нумерация разрядов

в регистрах сдвига

противоположна общепринятой, а именно, нулевой разряд старший, а разряд с

наибольшим

номером - младший.

C

D ТT

Прием информации в регистр

Q0

D

Q0

Q1

Q2

1

0

1

С

t

C

Q0

D TT

Q1

C

1

0

1

Q1

0

0

1

0

Q2

0

0

0

1

C

D TT

0

t

t

t

t

Q2

D

Выдача информации из регистра

С

t

Q0

1

0

0

0

t

Q1

0

1

0

0

Q2

t

t

1

0

1

0

t

17.

2.2. Регистры сдвигаРегистр со сдвигом вправо на двухступенчатых D-триггерах

УГО:

D

C

D

RG

Q2

Временные диаграммы

Схема:

D

Q2

C

Нумерация разрядов

в регистрах сдвига

противоположна общепринятой, а именно, нулевой разряд старший, а разряд с

наибольшим

номером - младший.

C

D ТT

Прием информации в регистр

Q0

D

Q0

Q1

Q2

1

0

1

С

t

C

Q0

D TT

Q1

C

1

0

1

Q1

0

0

1

0

Q2

0

0

0

1

C

D TT

0

t

t

t

t

Q2

D

Выдача информации из регистра

С

t

Q0

1

0

0

0

t

Q1

0

1

0

0

Q2

t

t

1

0

1

0

t

18.

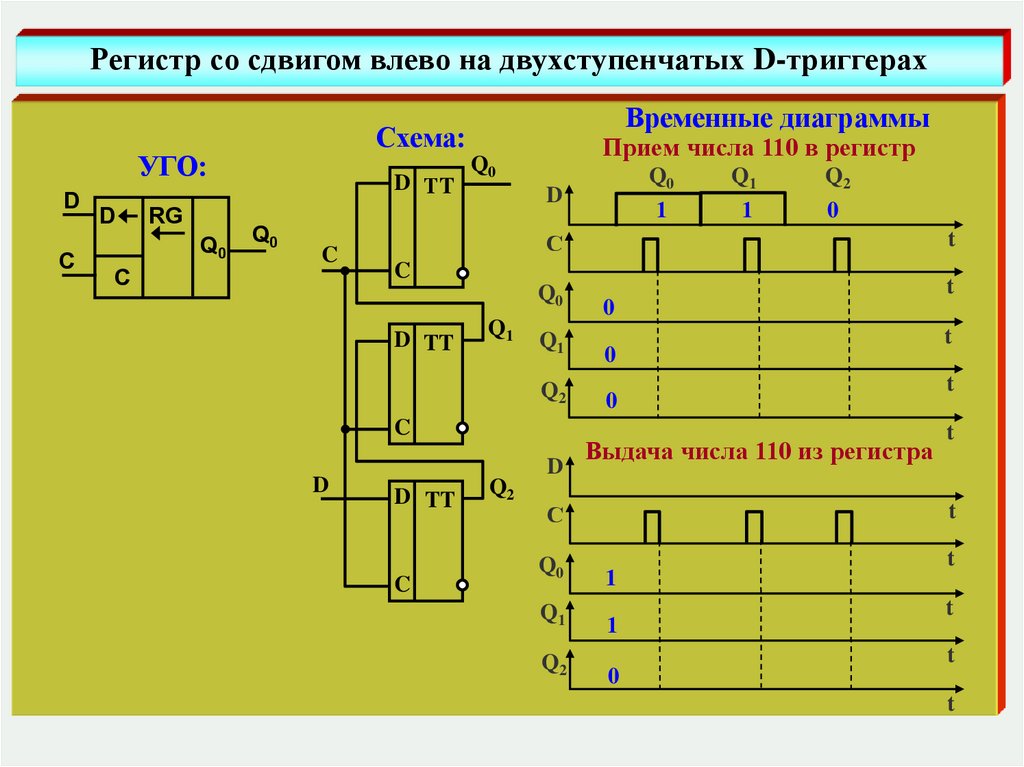

Регистр со сдвигом влево на двухступенчатых D-триггерахУГО:

D

C

D

RG

Q0

Временные диаграммы

Схема:

D ТT

Q0

C

C

Прием числа 110 в регистр

Q0

D

Q1

Q2

1

1

0

С

t

Q0

t

0

Q1

0

Q2

0

C

D TT

Q1

C

D

Q0

D TT

C

Q2

D

Выдача числа 110 из регистра

С

t

t

t

Q0

1

Q1

1

Q2

t

t

t

t

0

t

19.

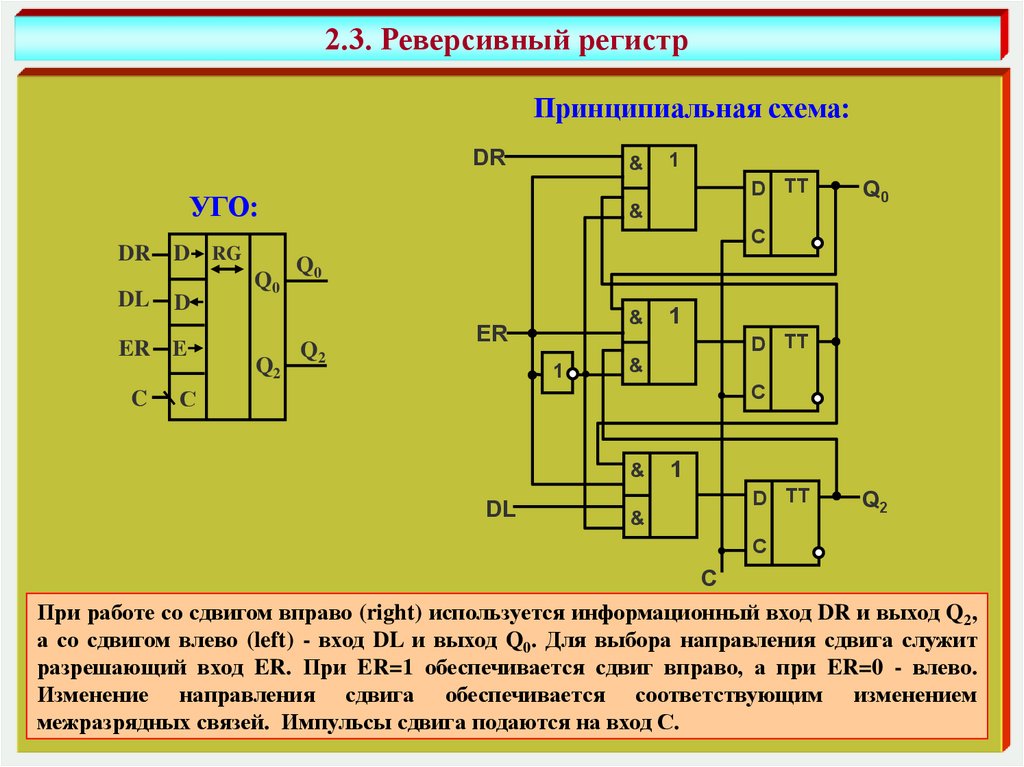

2.3. Реверсивный регистрПринципиальная схема:

DR

&

D TТ

УГО:

D

ER Е

C

&

Q0

C

DR D RG

DL

1

Q0

Q2

Q0

Q2

&

ER

1

D TТ

1

&

C

С

&

DL

1

D TТ

&

Q2

C

C

При работе со сдвигом вправо (right) используется информационный вход DR и выход Q2,

а со сдвигом влево (left) - вход DL и выход Q0. Для выбора направления сдвига служит

разрешающий вход ER. При ER=1 обеспечивается сдвиг вправо, а при ER=0 - влево.

Изменение направления сдвига обеспечивается соответствующим изменением

межразрядных связей. Импульсы сдвига подаются на вход С.

20.

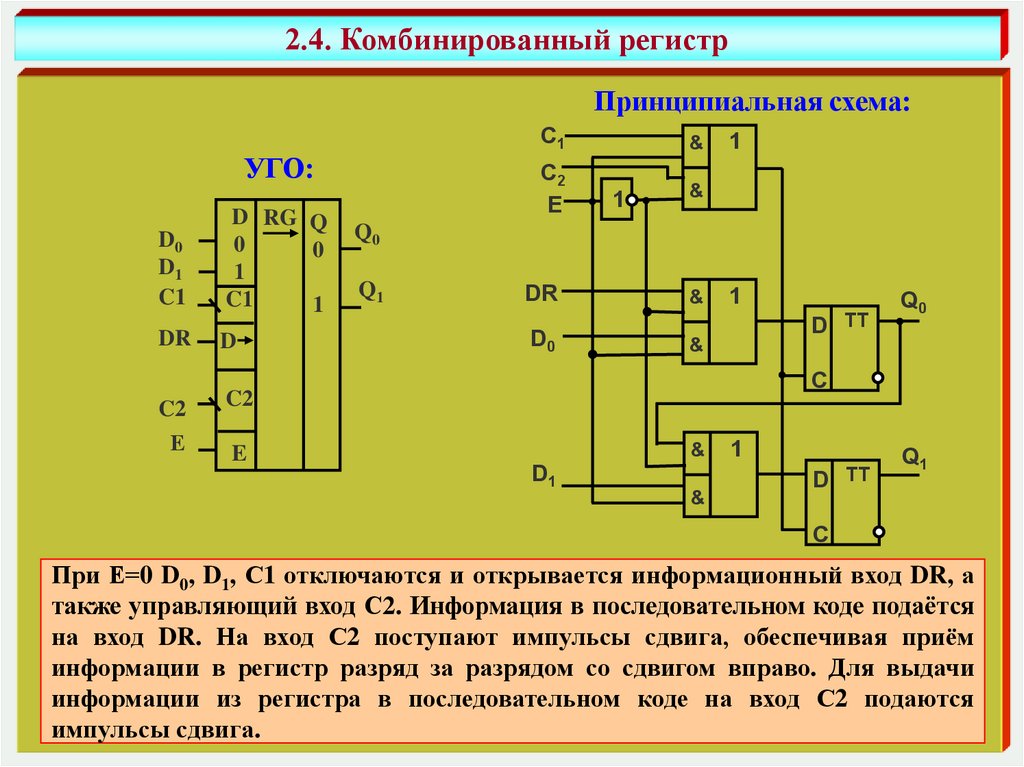

2.4. Комбинированный регистрПринципиальная схема:

C1

УГО:

D0

D1

C1

D RG Q

0

0

1

C1

1

DR

D

C2

C2

Е

E

C2

E

&

1

1

&

Q0

Q1

DR

D0

&

1

D TТ

&

Q0

C

&

D1

&

1

D TТ

Q1

C

При Е=0 D0, D1, С1 отключаются и открывается информационный вход DR, а

также

управляющийсигнале

вход С2.Е=1

Информация

в последовательном

коде

подаётся

При разрешающем

открываются

информационные

входы

D0 и

на

вход

DR. На вход

С2С1.

поступают

импульсы всдвига,

приём

D1 и

управляющий

вход

Приём информации

регистробеспечивая

осуществляется

в

информации

в коде

регистр

со синхронизирующего

сдвигом вправо. Для

выдачи

параллельном

черезразряд

входызаD0разрядом

, D1 по срезу

импульса

информации

на входе С1. из регистра в последовательном коде на вход С2 подаются

импульсы сдвига.

21.

Основным назначением регистров является хранение и выдачадвоично-кодированной информации. В регистрах памяти разряды

информационно не связаны, но имеют общие цепи синхронизации,

разрешения записи и др. Приём и выдача информации в этих

регистрах осуществляется в параллельном коде. Регистры сдвига

принимают и выдают информацию в последовательном коде со

сдвигом вправо или влево, а реверсивные регистры могут работать

в любом из этих режимов. Комбинированные регистры могут

преобразовывать параллельный код в последовательный и

наоборот.

22.

1. Отработать лекцию, используя:ЭЛ. 1/о. м. 3.4;

Л.1/д. с.80-85;

Л.2/д. с.89-94;

2. Подготовиться к пр. зан. №5 «Анализ и расчет типовых

последовательностных цифровых узлов ЭВМ».

Электроника

Электроника