Похожие презентации:

Основы микропроцессорной техники (лекция 1)

1.

Лекция 1 на тему:«Основы микропроцессорной техники»

Леонов С.В., доцент ОАР, к.т.н.

2021 г.

2. Математическая логика. Булева алгебра

2 ноября 1815 – 8 декабря 1864• Английский математик и логик.

Профессор математики

Королевского колледжа Корка (ныне

Университетский колледж Корк).

• Один из основателей

математической логики.

• В честь него назван тип данных

Boolean в программировании

3. Простые логические элементы

4.

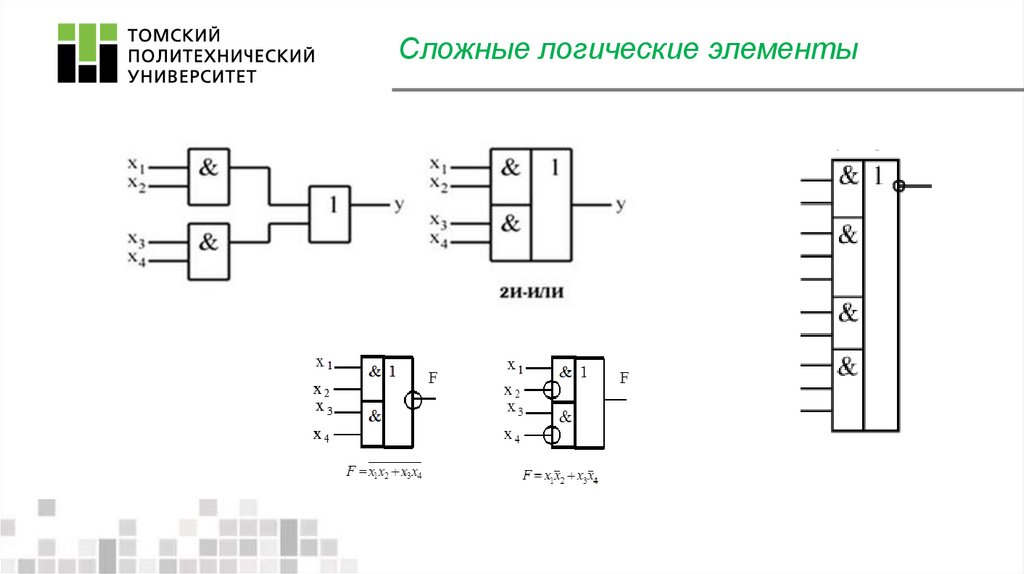

Сложные логические элементы5.

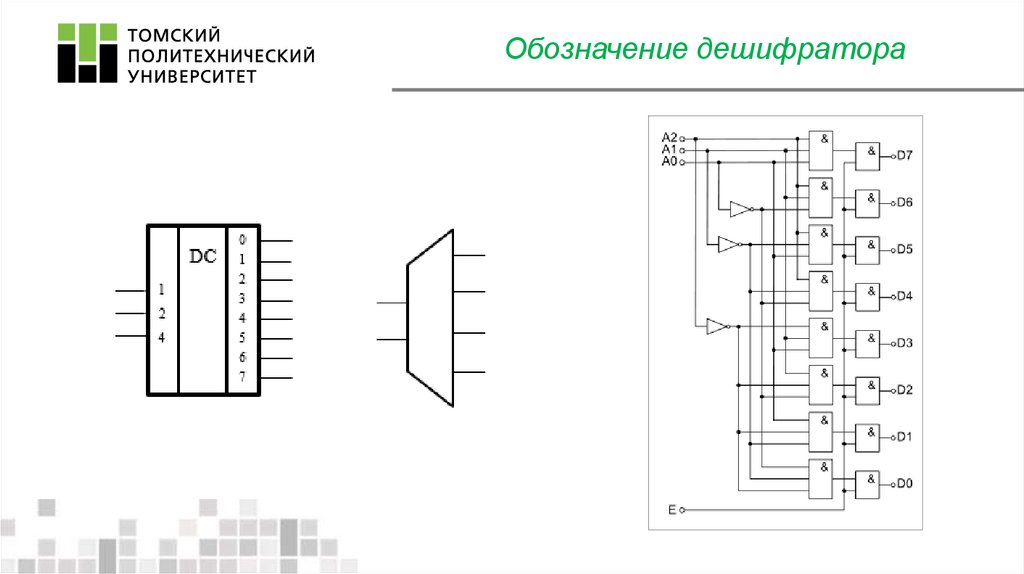

Обозначение дешифратора6.

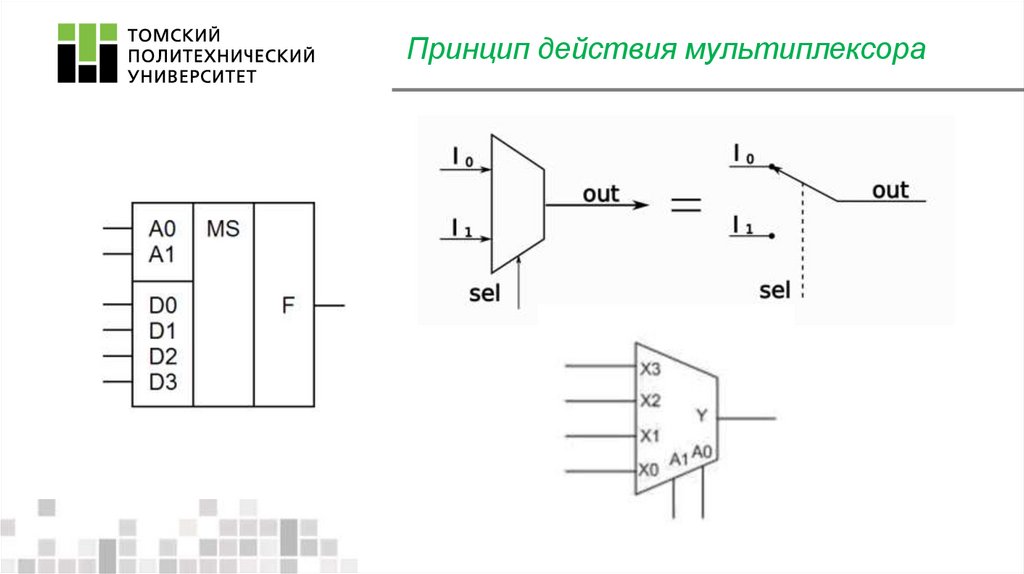

Принцип действия мультиплексора7.

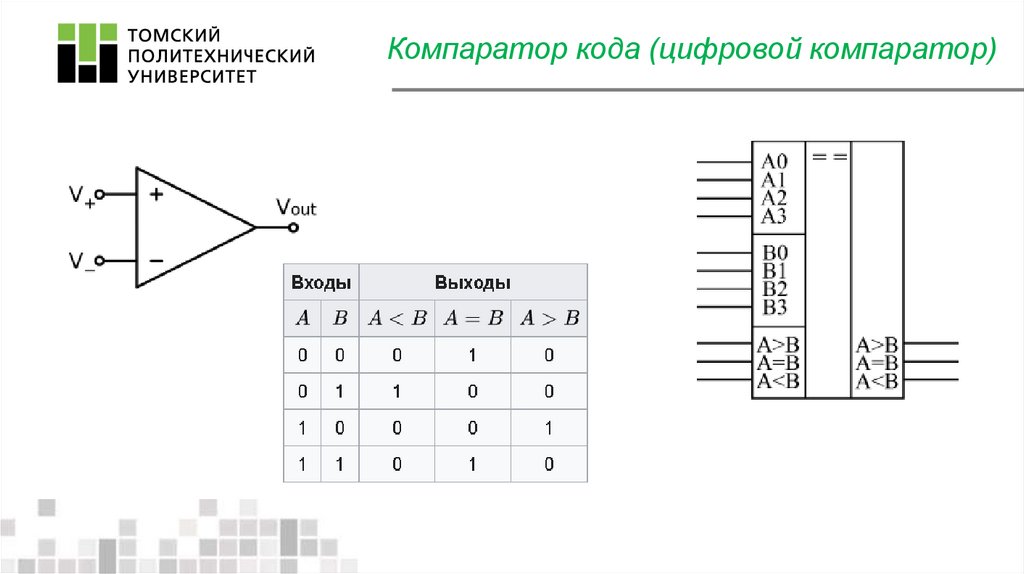

Компаратор кода (цифровой компаратор)8.

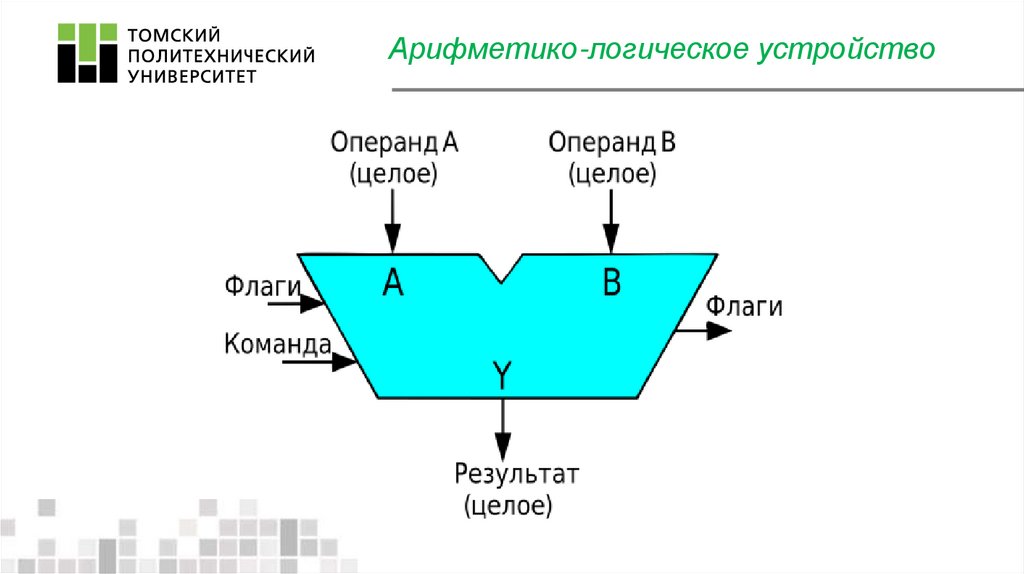

Арифметико-логическое устройство9.

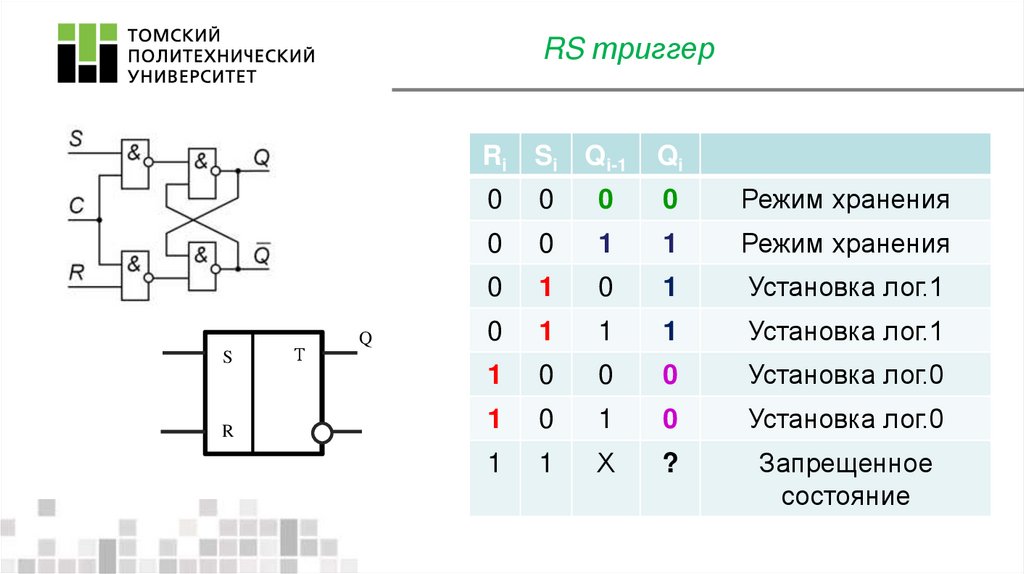

RS триггерS

R

Т

Q

Ri

Si Qi-1

Qi

0

0

0

0

Режим хранения

0

0

1

1

Режим хранения

0

1

0

1

Установка лог.1

0

1

1

1

Установка лог.1

1

0

0

0

Установка лог.0

1

0

1

0

Установка лог.0

1

1

Х

?

Запрещенное

состояние

10.

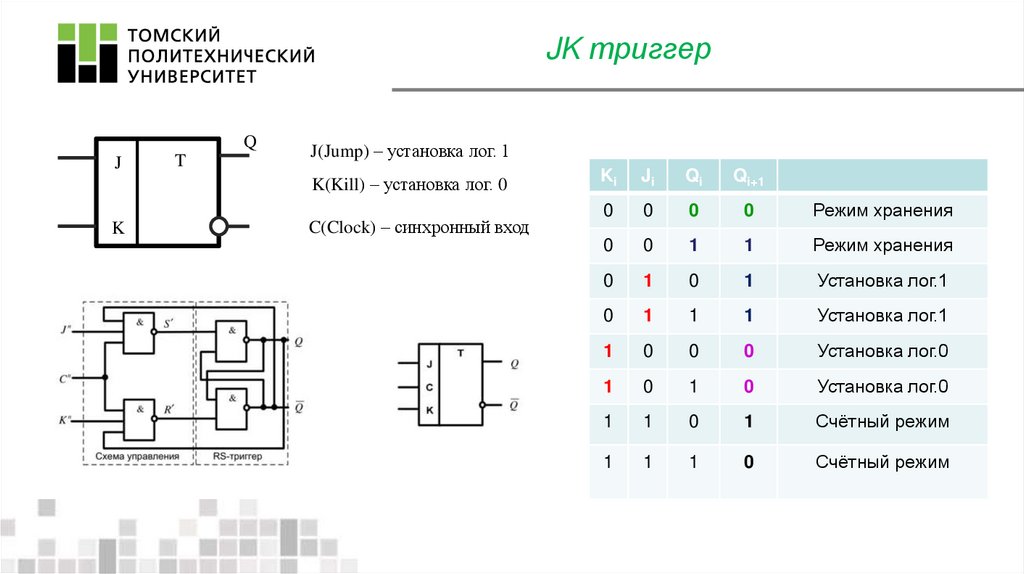

JK триггерQ

J

T

J(Jump) – установка лог. 1

K(Kill) – установка лог. 0

K

C(Clock) – синхронный вход

Ki

Ji

Qi

Qi+1

0

0

0

0

Режим хранения

0

0

1

1

Режим хранения

0

1

0

1

Установка лог.1

0

1

1

1

Установка лог.1

1

0

0

0

Установка лог.0

1

0

1

0

Установка лог.0

1

1

0

1

Счётный режим

1

1

1

0

Счётный режим

11.

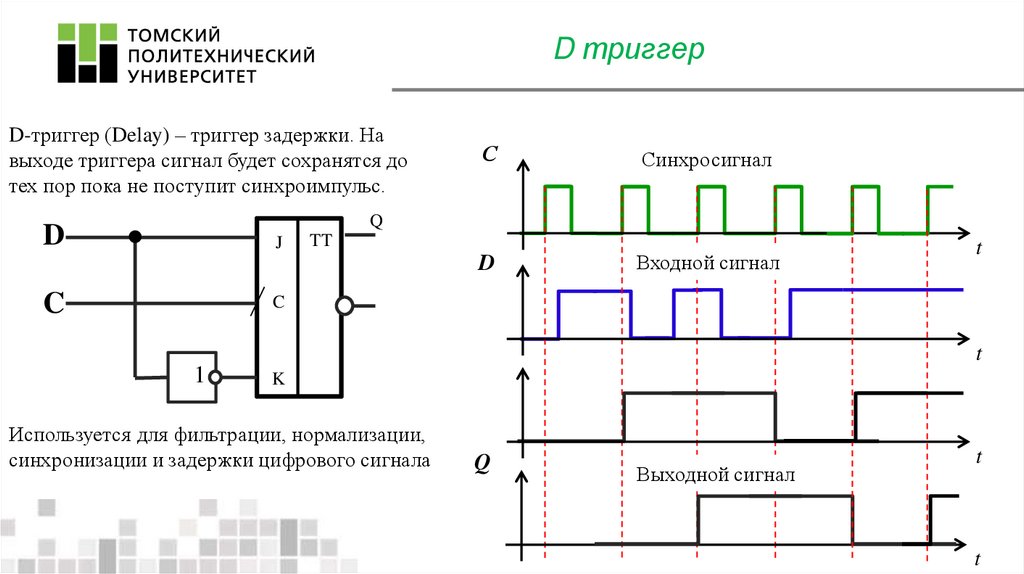

D триггерD-триггер (Delay) – триггер задержки. На

выходе триггера сигнал будет сохранятся до

тех пор пока не поступит синхроимпульс.

С

Синхросигнал

D

Входной сигнал

Q

D

J

C

TT

t

C

t

1

K

Используется для фильтрации, нормализации,

синхронизации и задержки цифрового сигнала

Q

Выходной сигнал

t

t

12.

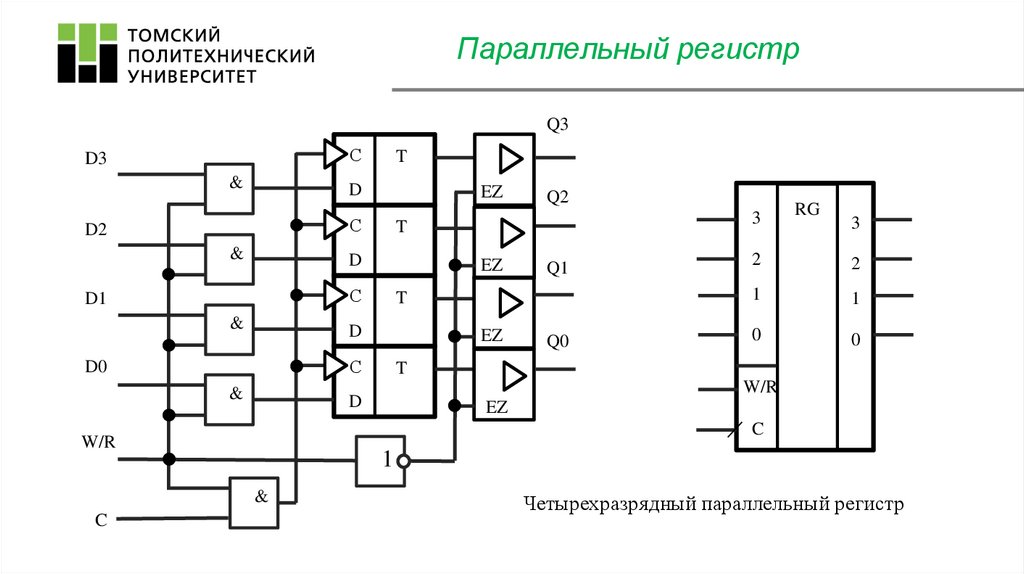

Параллельный регистрQ3

С

D3

&

D

EZ

С

D2

&

EZ

С

&

Q1

T

D

D0

3

EZ

С

&

Q2

T

D

D1

Q0

RG

3

2

2

1

1

0

0

T

W/R

D

EZ

C

W/R

1

&

C

T

Четырехразрядный параллельный регистр

13.

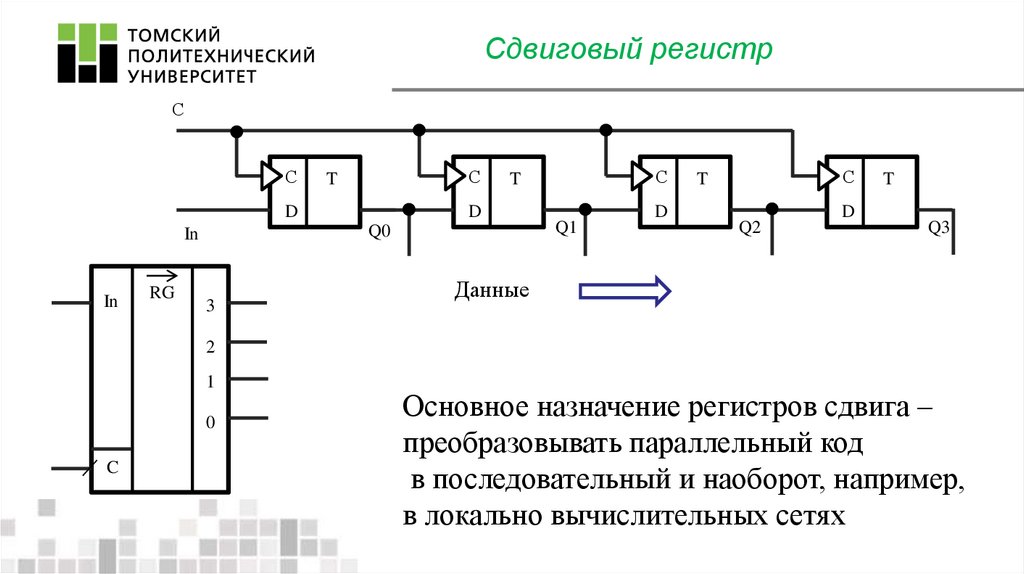

Сдвиговый регистрС

С

С

T

D

In

RG

D

Q0

In

3

С

T

Q1

D

С

T

Q2

D

T

Q3

Данные

2

1

0

C

Основное назначение регистров сдвига –

преобразовывать параллельный код

в последовательный и наоборот, например,

в локально вычислительных сетях

14.

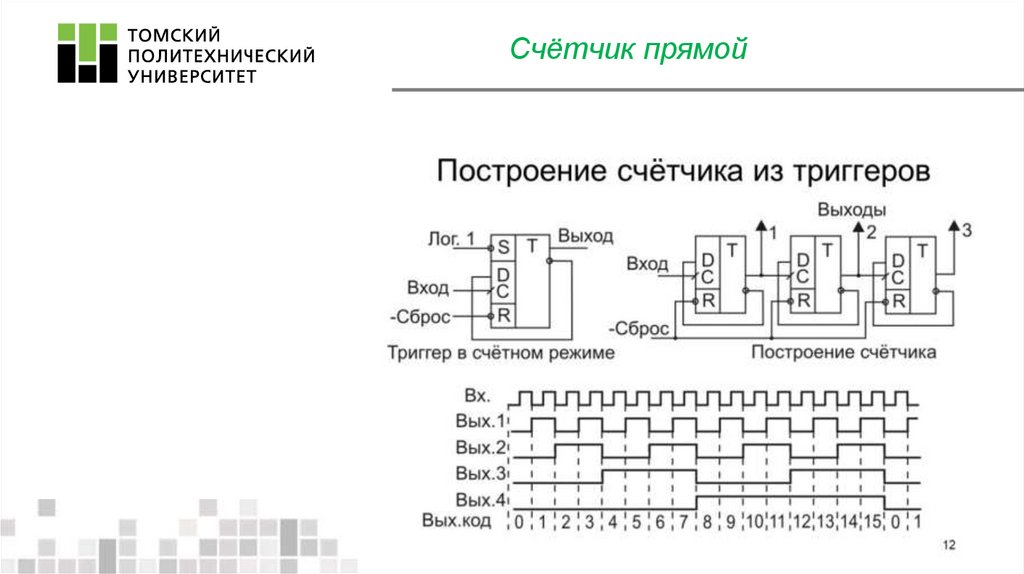

Счётчик прямой15.

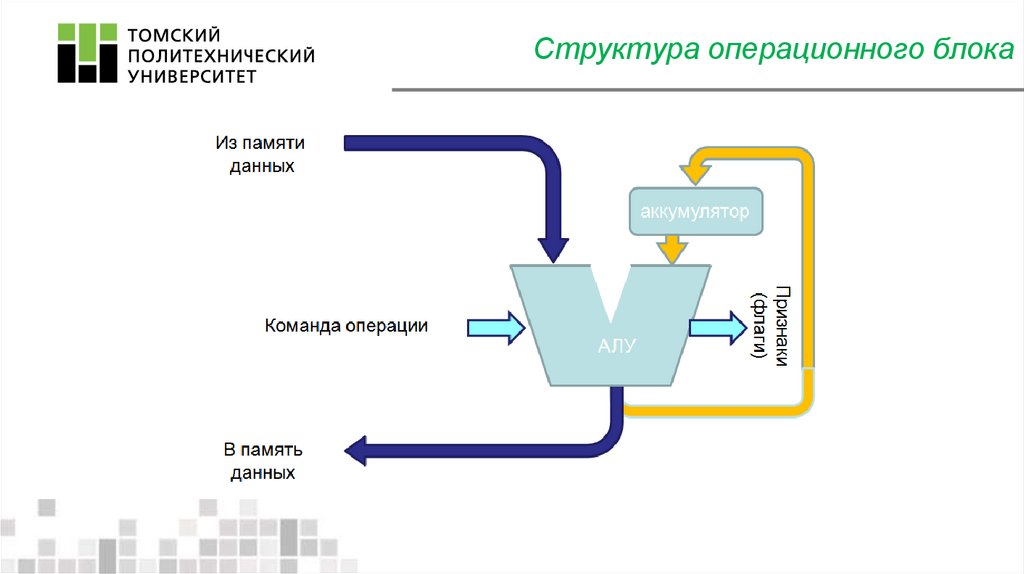

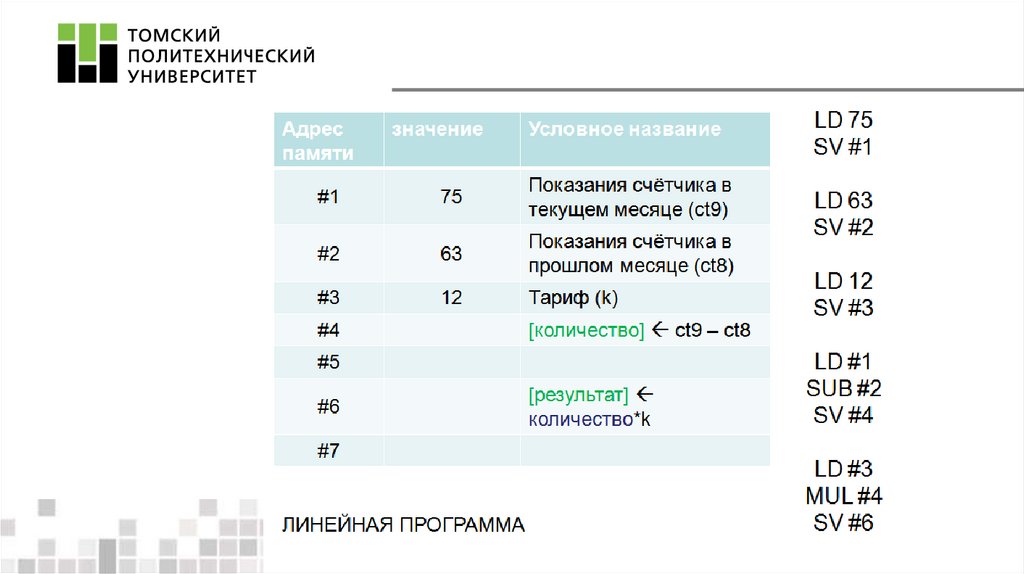

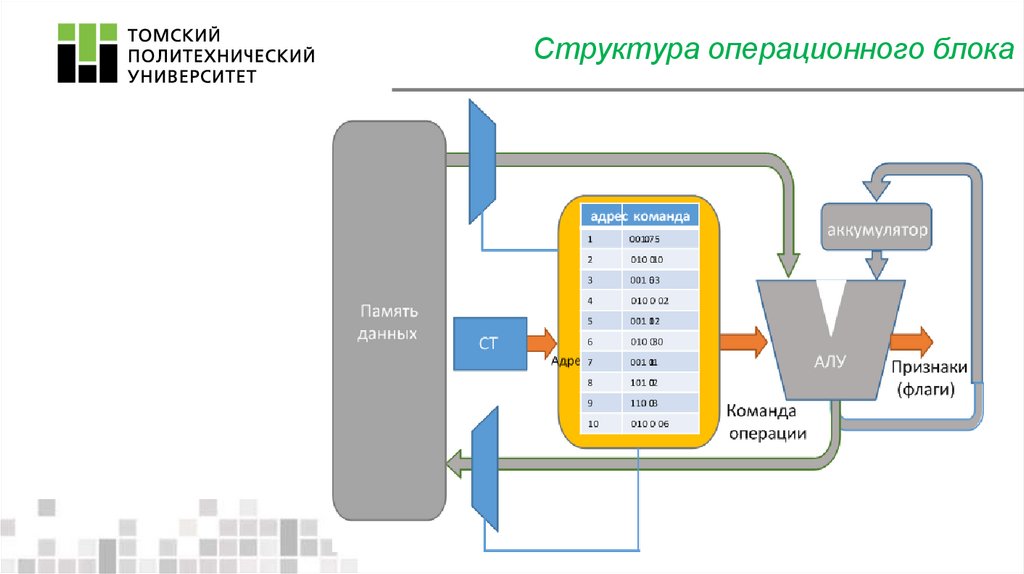

Структура операционного блока16.

17.

Структура операционного блока18.

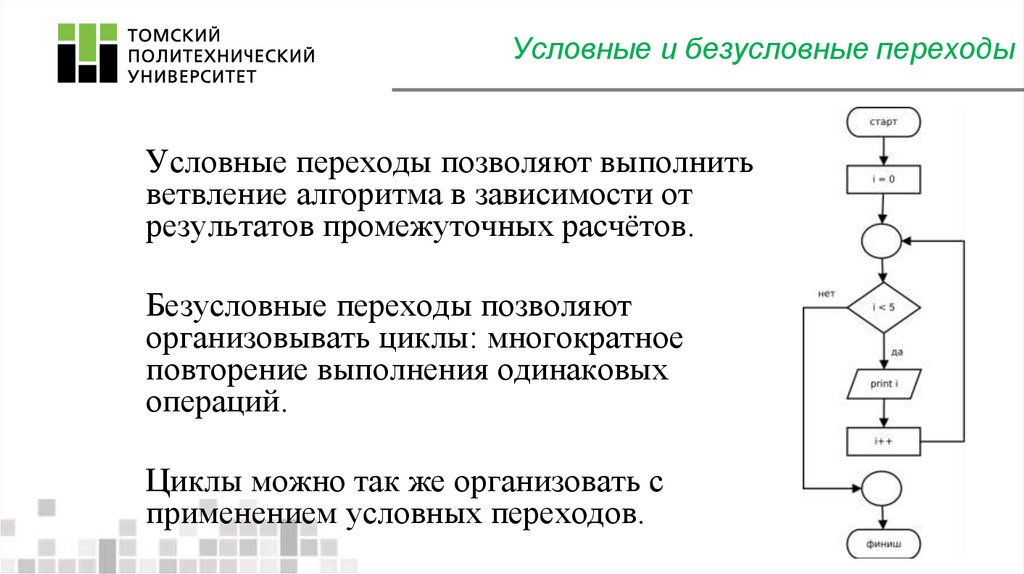

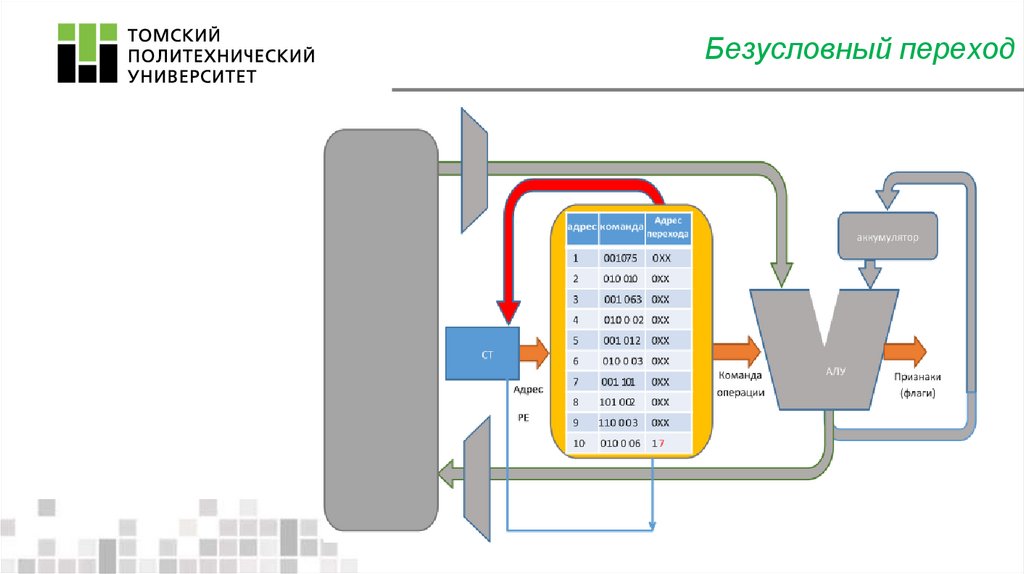

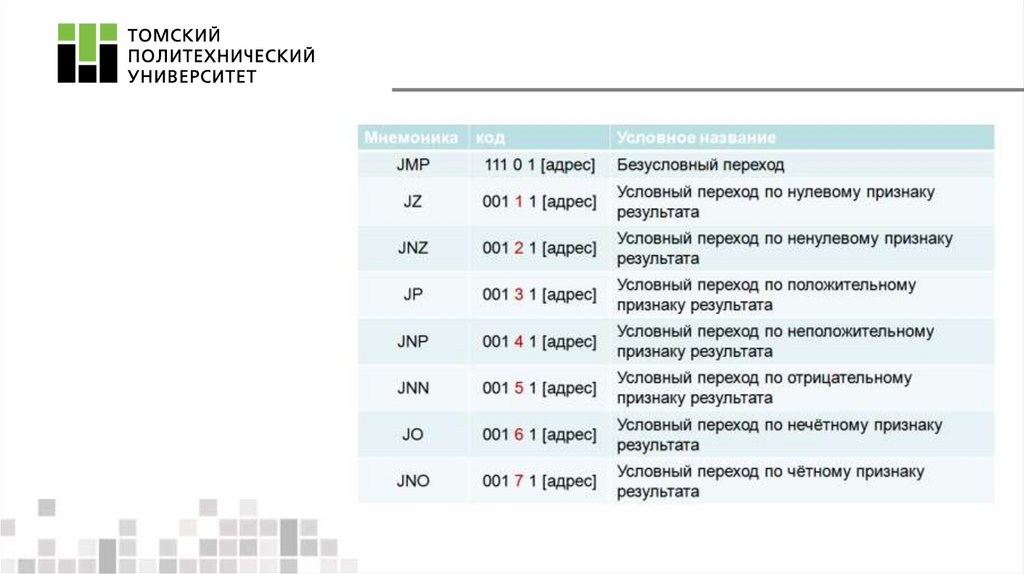

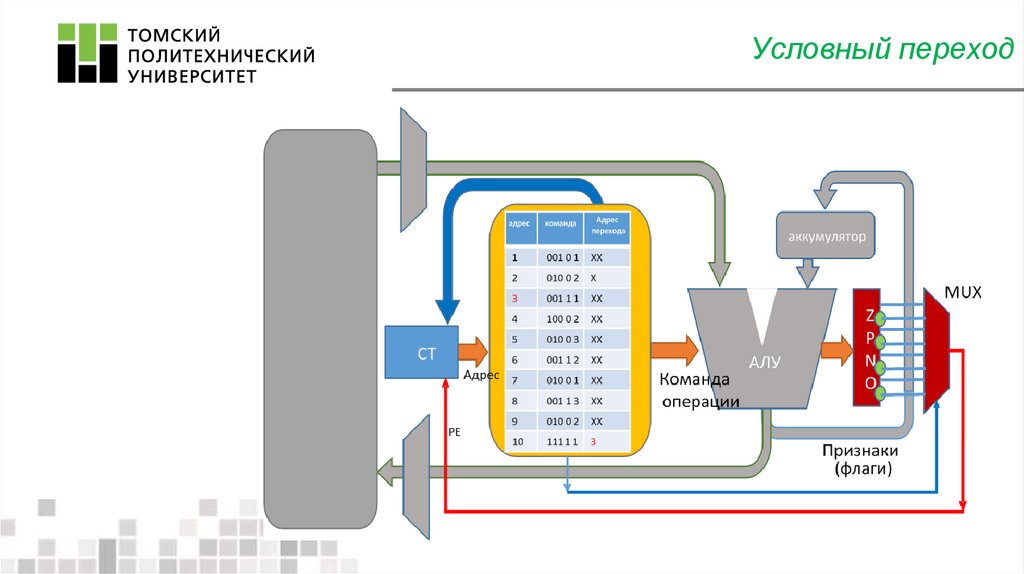

Условные и безусловные переходыУсловные переходы позволяют выполнить

ветвление алгоритма в зависимости от

результатов промежуточных расчётов.

Безусловные переходы позволяют

организовывать циклы: многократное

повторение выполнения одинаковых

операций.

Циклы можно так же организовать с

применением условных переходов.

Электроника

Электроника