Похожие презентации:

Основные устройства цифровой электроники

1.

Дисциплина «Основы цифровой электроники»Основные устройства

цифровой электроники

2. Литература

1.Опадчий Ю.Ф., Глудкин О.П., Гуров А.И. Аналоговая и цифроваяэлектроника: Учебник для вузов.-М.: Горячая линия – Телеком.-2007

2. Марченко А.Л. Основы электроники: Учеб. пособие для вузов.- М.: ДМК

Пресс.- 2012.

3. Гусев В.Г. Электроника и микропроцессорная техника: Учебник для

вузов.- М., 2017.

4. Миленина С.А. Электроника и схемотехника: Учеб пособие для вузов.М.: ЮРАЙТ.- 2017.

5. Скаржепе В.А., Сенько В.И. Электроника и микросхемотехника: Сборник

задач.- Киев: Вища школа.- 1989.

6. Хокинс Г. Цифровая электроника для начинающих.-М.: Мир.- 1989.

7. Тули М. Справочное пособие по цифровой электронике.-М.:

Энергоатомиздат.- 1989.

8. Артемов К.С., Солдатова Н.Л. Основы цифровой электроники: Учеб.

пособие для вузов.-Ярославль, ЯрГУ.- 2013.

9. Кириченко П.Г. Цифровая электроника для начинающих.- СПб: БХВ,

Петербург.- 2019.

3. Литература (продолжение)

10. Богомолов С.А. Основы электроники и цифровой схемотехники:Учеб. пособие для вузов.- М.: Академия.- 2014.

11. Игошин В.И. Сборник задач по математической логике и теории

алгоритмов: Учеб. пособие для вузов.- М.: ООО»КУРС».-2017.

12. Янсен Й. Курс цифровой электроники. В 4-х томах. Пер. с голл. –

М.: Мир.-1987.

13. Потемкин И.С. Функциональные узлы цифровой автоматики.- М.:

Энергоатомиздат, 1988

14. Токхейм Р. Основы цифровой электроники.- М.: Мир, 1988

15. Ермағанбетов Қ.Т. Цифрлық электроника: Оқу құралы.- КарГУ,

2001

4. План

1.2.

3.

4.

5.

6.

7.

8.

9.

10.

Классификации цифровых устройств

(комбинационные/последовательностные,

асинхронные/синхронные)

Последовательностные цифровые устройства:

Триггеры (RS-, D-, JK-триггеры).

Регистры.

Счетчики.

Комбинационные цифровые устройства:

Шифраторы и дешифраторы.

Мультиплексоры и демультиплексоры.

Компараторы.

Сумматоры.

5.

Цифровые устройства (ЦУ), т.е. устройства, формирующиеФАЛ, классифицируются по различным признакам.

По характеру информации на входах и выходах ЦУ

подразделяют на последовательностные (или

последовательные) и комбинационные устройства.

Элементной базой современных ЦУ и систем являются

цифровые интегральные схемы.

6. Триггеры и регистры

Триггеры и регистры относятся к последовательностным(последовательным) устройствам.

Это простейшие представители цифровых микросхем, имеющих

внутреннюю память.

Выходные сигналы микросхем с внутренней памятью зависят не только от

текущих входных сигналов, но и от того, какие входные сигналы и в какой

последовательности поступали на них в прошлом.

Триггеры и регистры сохраняют свою память только до тех пор, пока на

них подается напряжение питания, т.е. их память относится к типу

оперативной.

После отключения питания и его последующего включения триггеры и

регистры переходят в случайное состояние, т.е. их выходные сигналы

могут устанавливаться как в уровень логической единицы, так и в уровень

логического нуля.

7.

Преимущество триггеров и регистров перед другими микросхемамис памятью – максимально высокое быстродействие (минимальные

времена задержек срабатывания и максимально допустимая

рабочая частота)

Поэтому триггеры и регистры иногда называют сверхоперативной

памятью.

Недостаток триггеров и регистров в том, что объем их внутренней

памяти очень мал.

Триггеры могут хранить только отдельные сигналы, биты

Регистры могут хранить отдельные коды, байты, слова

Триггер можно рассматривать как одноразрядную ячейку памяти.

Регистр – можно рассматривать как многоразрядную ячейку

памяти, которая состоит из нескольких триггеров.

Триггеры в регистре могут быть соединены параллельно (обычный,

параллельный регистр) или последовательно (сдвиговый регистр

или регистр сдвига).

8. Триггеры

В основе любого триггера («trigger» или «flip-flop») лежит схема издвух логических элементов, охваченных положительной обратной

связью, когда сигналы с выходов подаются на входы

В результате такого включения схема может находиться в одном из

двух устойчивых состояний сколь угодно долго, пока на нее подано

напряжение питания

Триггер переключается из одного состояния в другое под

действием входных сигналов, при этом напряжение на его выходе

изменяется скачкообразно

Как правило, триггер имеет два выхода: прямой и инверсный

Число входов зависит от структуры и функций, выполняемых

триггером

Триггеры классифицируют по способу записи информации и по

функциональному признаку

9. Классификация триггеров

может проводиться по разным определяющим признакам:по способу организации логических связей;

по способу записи информации;

по способу синхронизации;

по количеству информационных входов;

по количеству тактовых входов;

по виду выходных сигналов;

по способу запоминания информации;

по способу сохранения информации;

по организации структуры.

10. По способу организации логических связей

различают триггеры:С раздельной установкой состояний «0» и «1» (RS-триггеры)

Со счетным входом (Т-триггеры)

Универсальные с раздельной установкой состояний «0» и «1» (JKтриггеры)

С приемом информации с одного входа (D-триггеры)

Универсальные с управляемым приемом информации с одного

входа (DV-триггеры)

Комбинированные (напр., RST, JKRS, DRS-триггеры)

Со сложной входной логикой

11.

По способу записи информации триггеры подразделяются на:Несинхронизированные (асинхронные, не тактовые)

Синхронизированные (синхронные, тактовые)

По способу синхронизации различают триггеры:

Синхронные со статическим управлением записью

Синхронные с динамическим управлением записью

По количеству информационных входов триггеры могут быть с

одним входом, с двумя входами и с многими входами

По количеству тактовых входов различают триггеры

однотактные, двухтактные и многотактные

По виду выходных сигналов триггеры разделяются на

статические и динамические

12.

По способу запоминания информации триггеры могут быть слогической и физической организацией памяти

По способу сохранения информации различают триггеры с

активным сохранением информации и с пассивным

сохранением информации

По организации структуры выделяют триггеры прямы и

дуальные триггеры, с неизменной структурой и

программируемые

13.

По способу записи информации триггеры делятся наасинхронные и синхронные (синхронизируемые или

тактируемые)

В асинхронных триггерах информация может записываться

непрерывно и определяется информационными сигналами,

действующими на входах в данный момент времени

В тактируемых триггерах информация заносится только в

моменты действия синхронизирующего сигнала

Тактируемые триггеры имеют кроме информационных

входов также тактовый вход синхронизации

По функциональному признаку триггеры подразделяют по

состоянию входов и выходов триггера в момент

срабатывания (в исходном состоянии) и после срабатывания

По функциональному признаку триггеры подразделяют на

триггеры типа RS, D, T, JK, R и др.

14.

Триггеры как устройства относятся к генераторампрямоугольных импульсов

Логический уровень, действующий на входе логического

элемента и однозначно определяющий логический уровень

выходного сигнала (независимо от логических уровней,

действующих на остальных входах) называется активным

Уровни, подача которых на один из входов не приводит к

изменению логического уровня на выходе элемента,

называются пассивными

Наибольшее распространение в цифровых устройствах

получили: RS – триггер с двумя установочными входами,

тактируемый D – триггер и счетный T – триггер

Из-за низкой помехоустойчивости самостоятельно RS –

триггеры в устройствах цифровой электроники практически

не используются

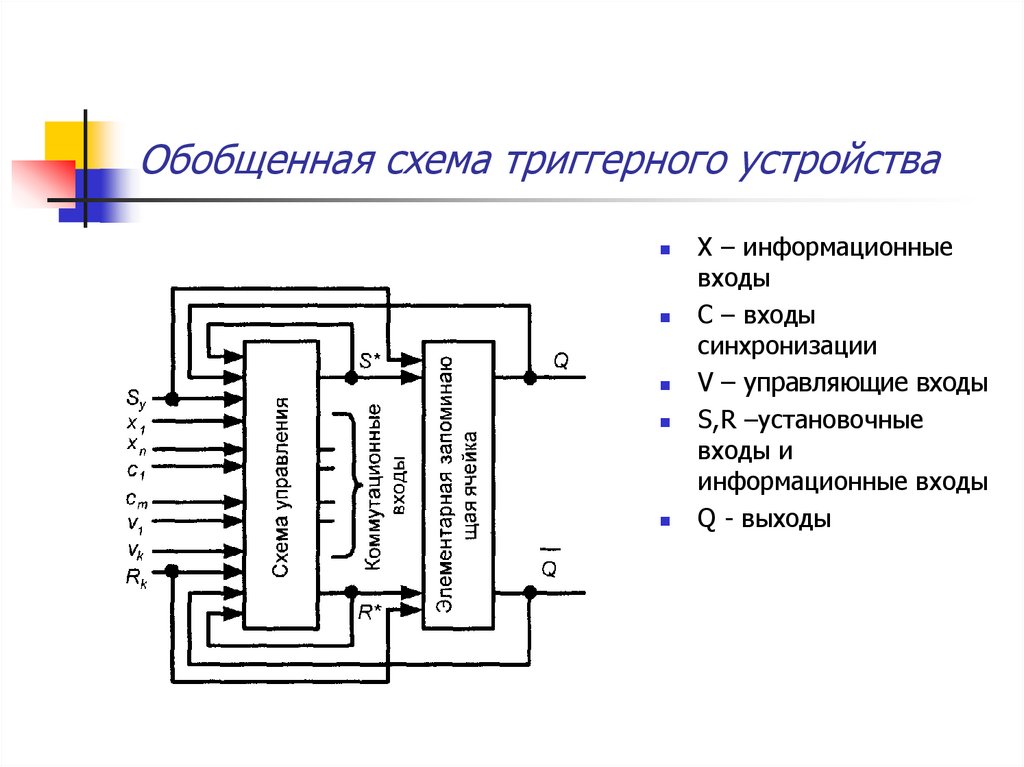

15. Обобщенная схема триггерного устройства

Х – информационныевходы

С – входы

синхронизации

V – управляющие входы

S,R –установочные

входы и

информационные входы

Q - выходы

16. Обозначения входов триггеров

S (Set - установка) – раздельный вход установки в единичное состояние(напряжение высокого уровня на прямом выходе Q)

R (Reset- сброс) - раздельный вход установки в нулевое состояние

(напряжение низкого уровня на прямом выходе Q)

D (Delay - задержка, Drive - передача ) – информационный вход для установки

триггера в состояние «0» или «1»

C (Clock – первичный источник сигналов синхронизации) – тактовый вход,

разрешает схеме управления запись информации в триггер)

T (Toggle - релаксатор)– счетный вход триггера

J (Jerk – внезапное включение) – вход для раздельной установки триггера в

состояние «1» в универсальном JK-триггере

K (Kill – внезапное отключение) – вход для раздельной установки триггера в

состояние «0» в универсальном JK-триггере

V (Valve – клапан, вентиль) – управляющий вход для разрешения приема

информационных или тактовых сигналов

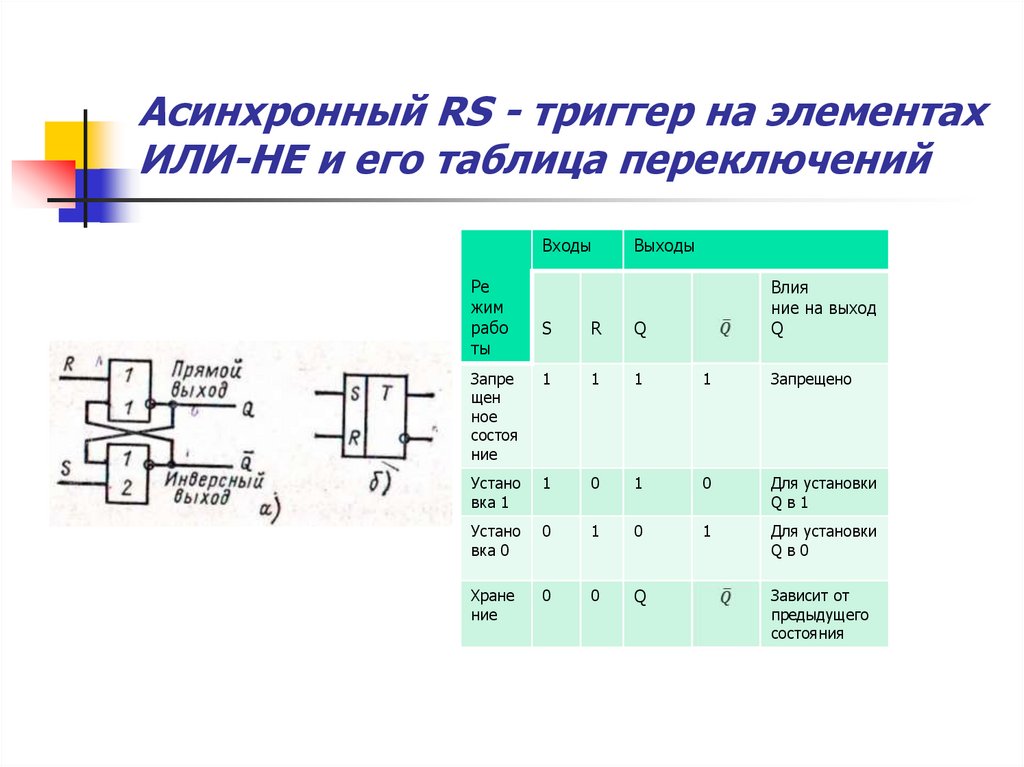

17. Асинхронный RS - триггер на элементах ИЛИ-НЕ и его таблица переключений

ВходыРе

жим

рабо

ты

Выходы

Влия

ние на выход

Q

S

R

Q

Запре

щен

ное

состоя

ние

1

1

1

1

Запрещено

Устано

вка 1

1

0

1

0

Для установки

Qв1

Устано

вка 0

0

1

0

1

Для установки

Qв0

Хране

ние

0

0

Q

Зависит от

предыдущего

состояния

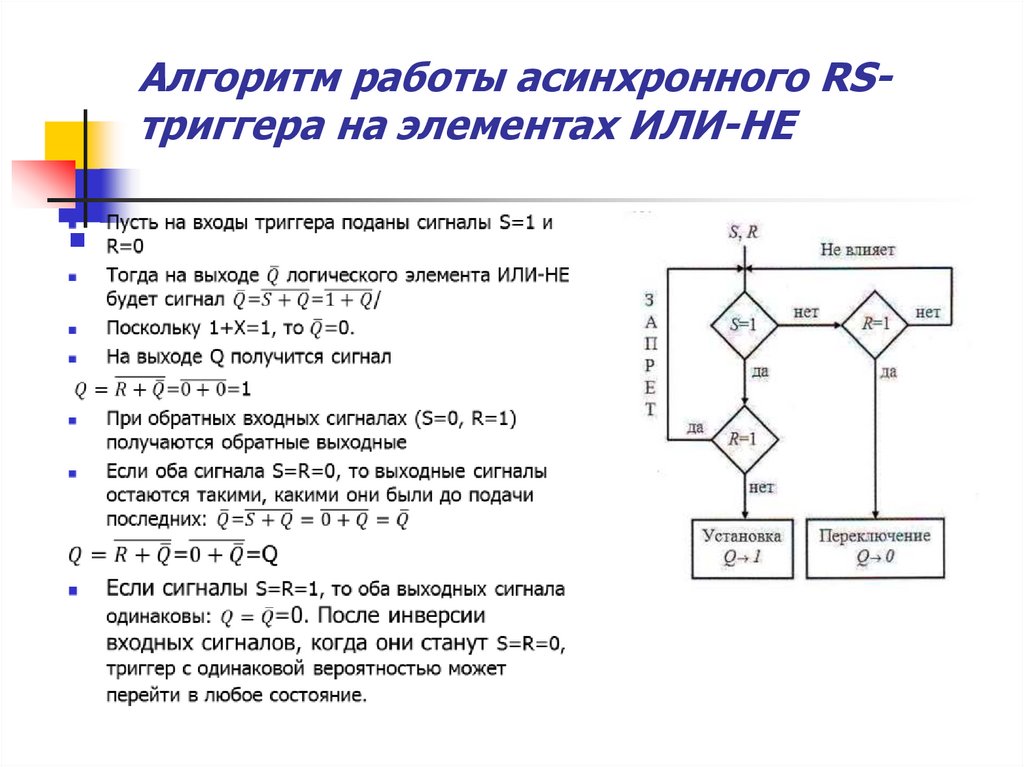

18. Алгоритм работы асинхронного RS- триггера на элементах ИЛИ-НЕ

Алгоритм работы асинхронного RSтриггера на элементах ИЛИ-НЕ19.

При описании работы последовательностных логическихсхем часто используются временные диаграммы сигналов

Эти диаграммы показывают уровни напряжения и

временные интервалы между входными и выходными

сигналами

По горизонтали откладывается время, по вертикали –

уровень напряжения

20. Временная диаграмма сигналов асинхронного RS- триггера на элементах ИЛИ-НЕ

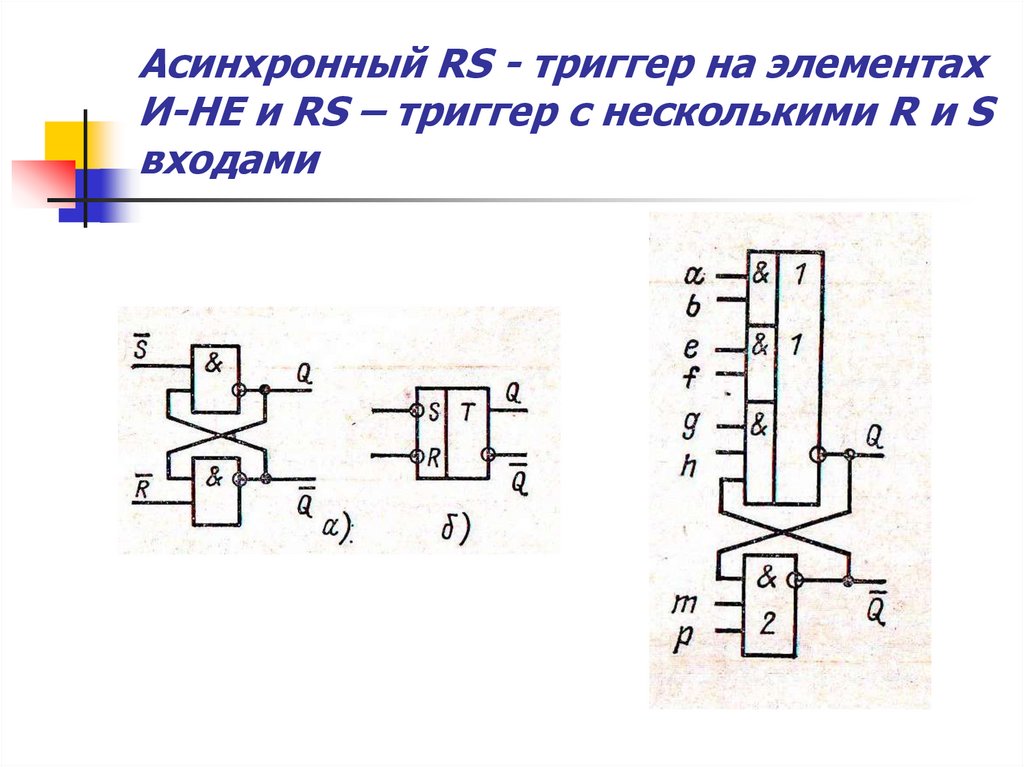

21. Асинхронный RS - триггер на элементах И-НЕ и RS – триггер с несколькими R и S входами

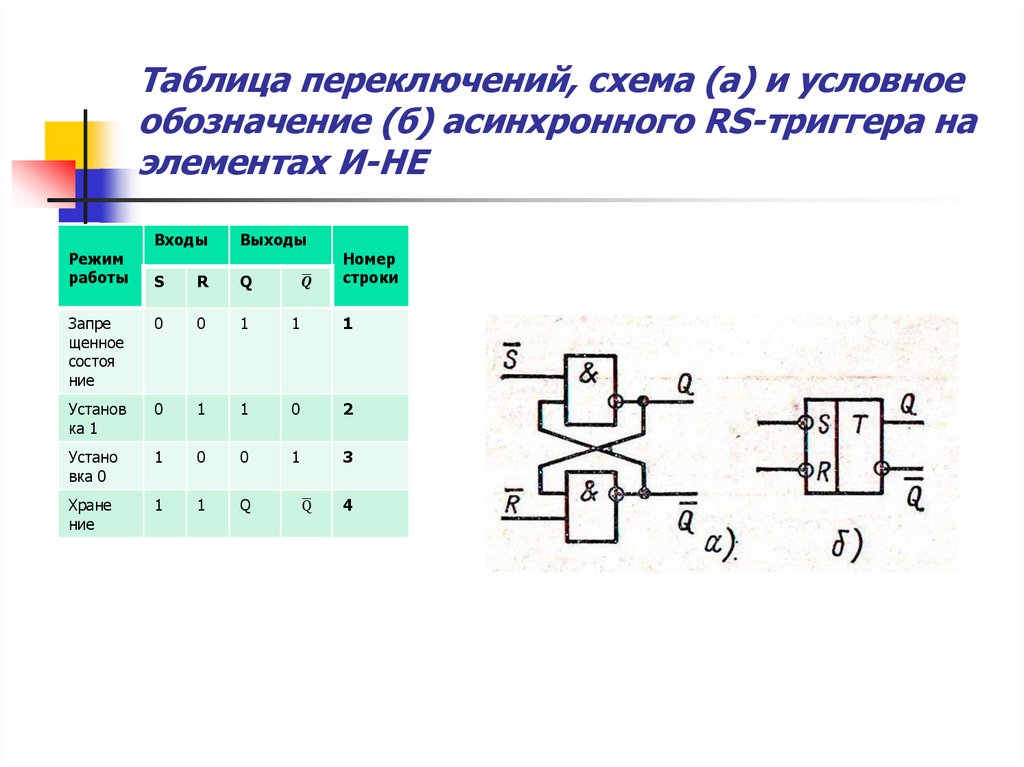

22. Таблица переключений, схема (а) и условное обозначение (б) асинхронного RS-триггера на элементах И-НЕ

ВходыВыходы

S

R

Q

Запре

щенное

состоя

ние

0

0

1

1

1

Установ

ка 1

0

1

1

0

2

Устано

вка 0

1

0

0

1

3

Хране

ние

1

1

Q

Режим

работы

Номер

строки

4

23. Временные диаграммы сигналов и таблица переключений для асинхронного RS-триггера на элементах И-НЕ

ВходыВыходы

S

R

Q

Запре

щенное

состоя

ние

0

0

1

1

1

Установ

ка 1

0

1

1

0

2

Устано

вка 0

1

0

0

1

3

Хране

ние

1

1

Q

Режим

работы

Номер

строки

4

24. Синхронный RS-триггер

Получается добавлением кобычному RS- триггеру двух

логических элементов И или И-НЕ

Входные сигналы проходят через

элементы И-НЕ только в те

моменты времени, когда на

другие входы этих элементов

(вход С) поступают

синхронизирующие импульсы

Поэтому состояния триггера могут

изменяться только в моменты

появления синхронизирующих

импульсов, т.е. моменты смены

состояния задаются внешними

синхронизирующими импульсами

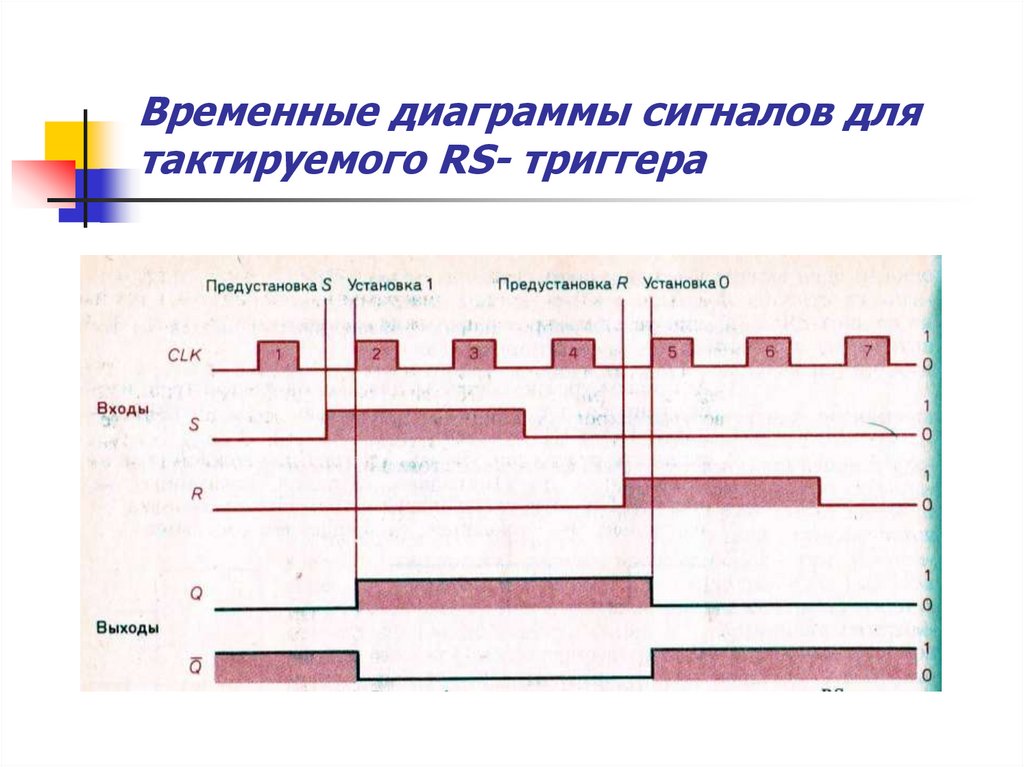

25. Временные диаграммы сигналов для тактируемого RS- триггера

26.

Различают синхронные RS- триггеры со статическим идинамическим управлением

Триггер со статическим управлением синхронизируется

уровнем синхронизирующего напряжения

Во время действия одного синхронизирующего импульса

такой триггер может изменить свое состояние, если

изменяются сигналы на R- и S- входах

Состояние триггеров с динамическим управлением меняется

только во время нарастания (перепада) синхроимпульса и

не может изменяться во время действия этого импульса

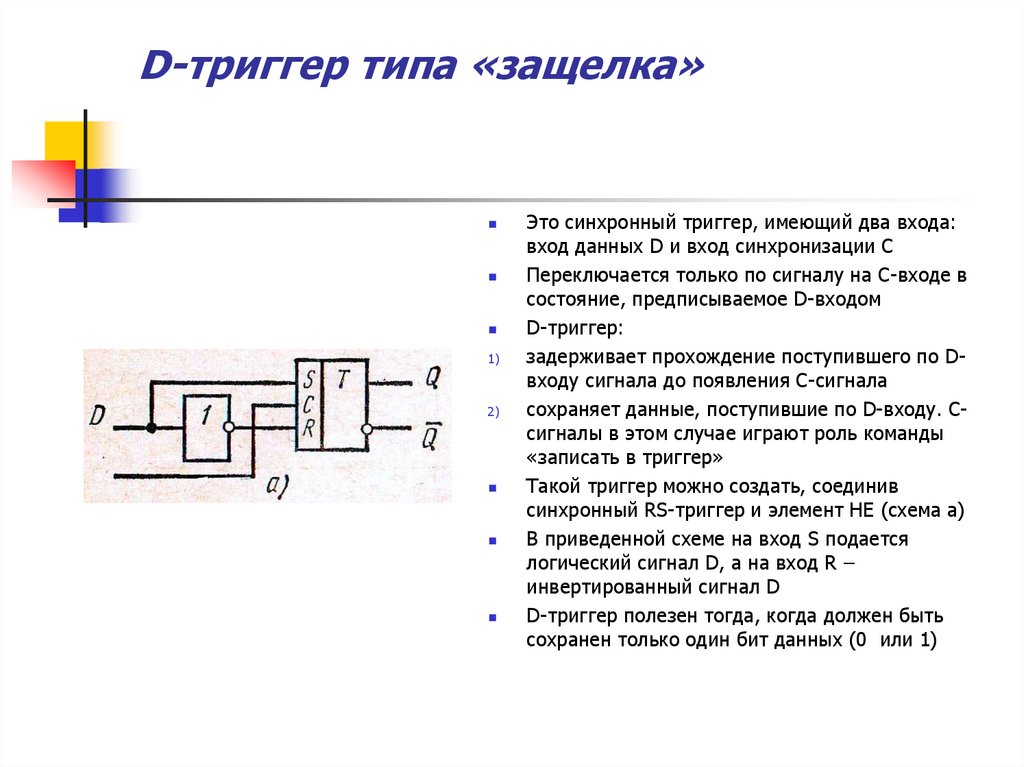

27. D-триггер типа «защелка»

1)2)

Это синхронный триггер, имеющий два входа:

вход данных D и вход синхронизации С

Переключается только по сигналу на С-входе в

состояние, предписываемое D-входом

D-триггер:

задерживает прохождение поступившего по Dвходу сигнала до появления С-сигнала

сохраняет данные, поступившие по D-входу. Ссигналы в этом случае играют роль команды

«записать в триггер»

Такой триггер можно создать, соединив

синхронный RS-триггер и элемент НЕ (схема а)

В приведенной схеме на вход S подается

логический сигнал D, а на вход R –

инвертированный сигнал D

D-триггер полезен тогда, когда должен быть

сохранен только один бит данных (0 или 1)

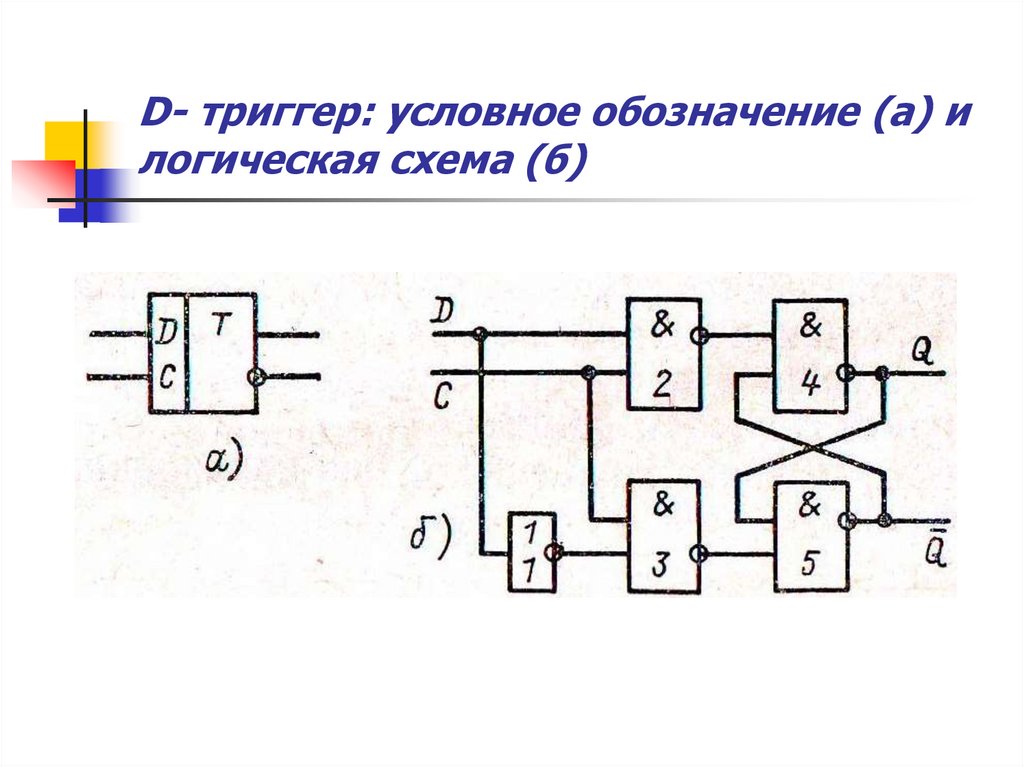

28. D- триггер: условное обозначение (а) и логическая схема (б)

29. Временная диаграмма сигналов D - триггера

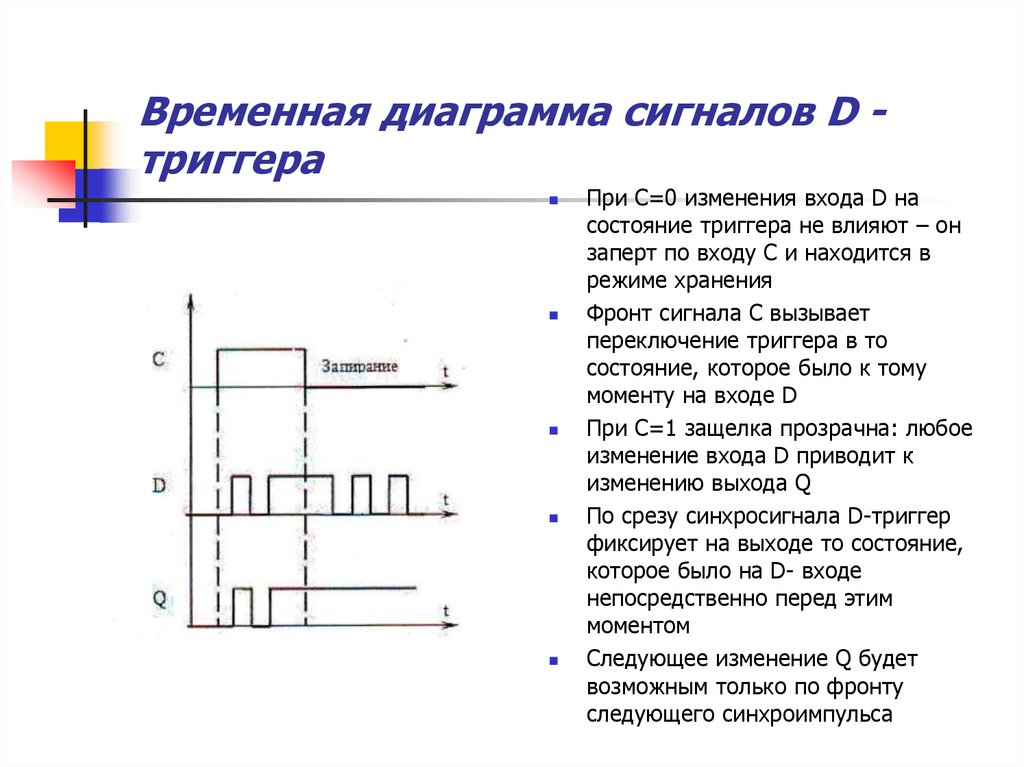

Временная диаграмма сигналов D триггераПри С=0 изменения входа D на

состояние триггера не влияют – он

заперт по входу С и находится в

режиме хранения

Фронт сигнала С вызывает

переключение триггера в то

состояние, которое было к тому

моменту на входе D

При С=1 защелка прозрачна: любое

изменение входа D приводит к

изменению выхода Q

По срезу синхросигнала D-триггер

фиксирует на выходе то состояние,

которое было на D- входе

непосредственно перед этим

моментом

Следующее изменение Q будет

возможным только по фронту

следующего синхроимпульса

30. Таблица переключений триггера- защелки

Таблица переключений триггеразащелкиРежим

Управление

Хранение

Входы

Выходы

С

D

Q

1

0

0

1

1

1

1

0

0

X

Q

31. JK- триггер

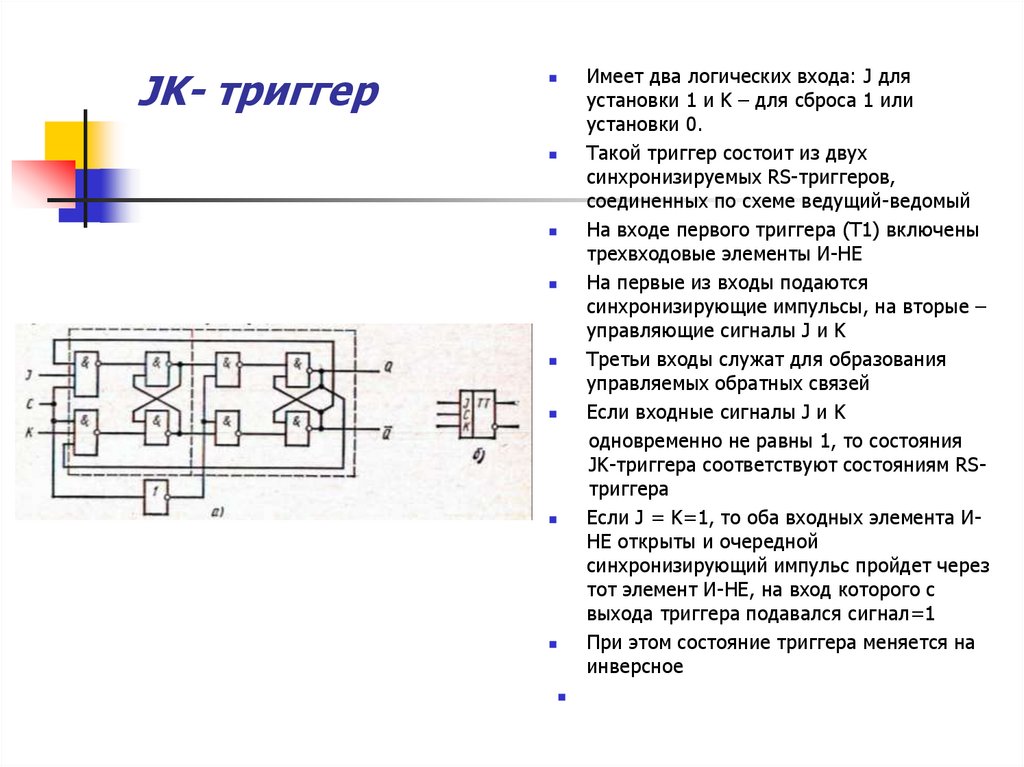

Имеет два логических входа: J дляустановки 1 и K – для сброса 1 или

установки 0.

Такой триггер состоит из двух

синхронизируемых RS-триггеров,

соединенных по схеме ведущий-ведомый

На входе первого триггера (Т1) включены

трехвходовые элементы И-НЕ

На первые из входы подаются

синхронизирующие импульсы, на вторые –

управляющие сигналы J и K

Третьи входы служат для образования

управляемых обратных связей

Если входные сигналы J и K

одновременно не равны 1, то состояния

JK-триггера соответствуют состояниям RSтриггера

Если J = K=1, то оба входных элемента ИНЕ открыты и очередной

синхронизирующий импульс пройдет через

тот элемент И-НЕ, на вход которого с

выхода триггера подавался сигнал=1

При этом состояние триггера меняется на

инверсное

32.

Особенность JK –триггера: когда на оба входа J и K подан высокий уровень,повторяющиеся тактовые импульсы заставляют выход переключаться или

изменять состояние

Таблица переключений JK –триггера:

J

K

Q

0

0

Сохраняется

прежнее состояние

0

1

0

1

0

1

1

1

Устанавливается

состояние,

инверсное

предшествующему

состоянию

33. Временная диаграмма JK-триггера

34. Т-триггер

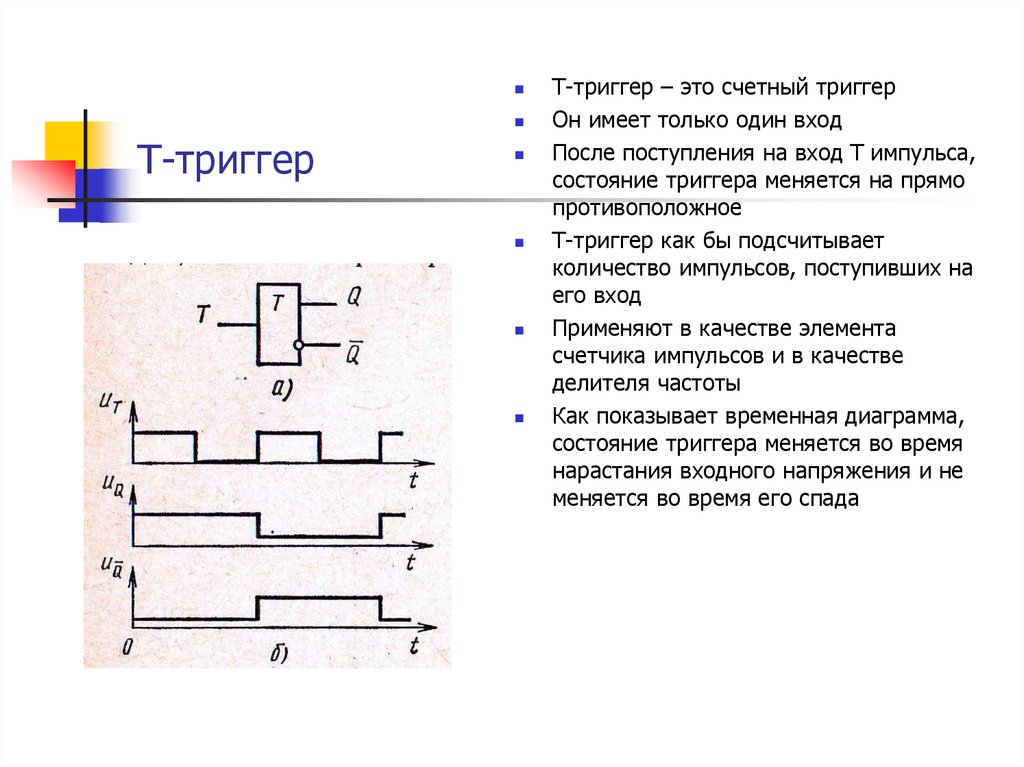

Т-триггер – это счетный триггерОн имеет только один вход

После поступления на вход Т импульса,

состояние триггера меняется на прямо

противоположное

Т-триггер как бы подсчитывает

количество импульсов, поступивших на

его вход

Применяют в качестве элемента

счетчика импульсов и в качестве

делителя частоты

Как показывает временная диаграмма,

состояние триггера меняется во время

нарастания входного напряжения и не

меняется во время его спада

35.

Считает только до одногоПри поступлении второго импульса Т-триггер сбрасывается в исходное

состояние

Строятся Т-триггеры только на базе двухступенчатых триггеров,

используются при построении схем различных счетчиков

В составе БИС различного назначения обычно есть готовые модули этих

триггеров

Электроника

Электроника