Похожие презентации:

Схемотехника цифровых устройств. Последовательные схемы

1. СХЕМОТЕХНИКА ЦИФРОВЫХ УСТРОЙСТВ ПОСЛЕДОВАТЕЛЬНЫЕ СХЕМЫ

УрФУЕкатеринбург

2018

2. Терминология и определение

Варианты названия:• Последовательностные (последовательность)

• Последовательные

• Схемы с памятью

• Конечные автоматы

• Состоят из логических элементов и элементов

памяти.

• Сигналы на выходе определяются не только

комбинацией входных сигналов в данный момент

времени, но и предыдущим состоянием схемы.

2

3. Способ описания

• Любая последовательная схемаописывается таблицей переключения

(переходов).

• В отличие от используемых ранее

таблиц истинности таблицы

переключений отражают переходы от

предыдущего состояния к следующему.

3

4. Триггеры Определение и применение

Триггер – это устройство, имеющее дваустойчивых состояния и способное под

воздействием управляющего импульса

скачкообразно переходить из одного

состояния в другое.

Применение

• формирование импульсов

• элементарный автомат в цифровых

устройствах

• Однобитовая ячейка памяти в счетчиках и

регистрах

4

5. Выходы и входы триггеров

Два выхода (Quit):• прямой ( Q)

• инверсный ( Q).

Состояние триггера отождествляется с состоянием его выхода Q:

Q = 1 – триггер в единичном состоянии, Q = 0 – в нулевом

состоянии.

Число входов зависит от структуры и функций триггера.

Входы триггера и сигналы на них обозначают:

• S (Set) – раздельный вход установки в единичное состояние

(напряжение высокого уровня на прямом выходе Q);

• R (Reset) – раздельный вход установки в нулевое состояние

(напряжение низкого уровня на прямом выходе Q);

• D (Data) – информационный вход (на него передается

информация, предназначенная для занесения в триггер);

• С – вход синхронизации;

• Т – счетный вход.

5

6. Классификация триггеров

По функциональным возможностям:• с раздельной установкой «0» и «1» (RS–триггеры);

• с приемом информации по одному входу (D–триггеры);

• счетный (Т–триггер);

• универсальный (JK – триггер);

• и многие другие.

По способу приема информации:

• асинхронные триггеры реагируют на информационные сигналы

в момент их появления на входе;

• синхронные – только при наличии разрешающего сигнала на

специально предусмотренном входе синхронизации С.

6

7. Асинхронный RS-триггер

• имеет два информационных входа:S и R для установки в 1 и в 0

соответственно

• два выхода: прямой и инверсный

• является элементом памяти для

всех остальных типов триггеров

• имеет устойчивое состояние для

любой разрешенной комбинации

значений входных сигналов

• бывают с прямым и инверсным

управлением

7

8. Таблица переходов асинхронного RS-триггера

Если на входах R = 0, S = 0,

состояние триггера не

изменяется (Qn = Qn+1); режим

хранения информации;

R = 0, S = 1 – триггер

устанавливается в единичное

состояние Qn+1 = 1;

R = 1, S = 0 – триггер

устанавливается в нулевое

состояние Qn+1 = 0;

R = 1, S = 1 – состояние

триггера будет

неопределенным, триггер может

равновероятно принять любое

из устойчивых состояний,

поэтому такая комбинация

является запрещенной.

S

R

Qn+1

0

0

Qn

0

1

0

1

0

1

1

1

x

S

R

Qn

Qn+1

0

0

0

0

0

0

1

1

0

1

0

0

0

1

1

0

1

0

0

1

1

0

1

1

1

1

0

x

1

1

1

x

8

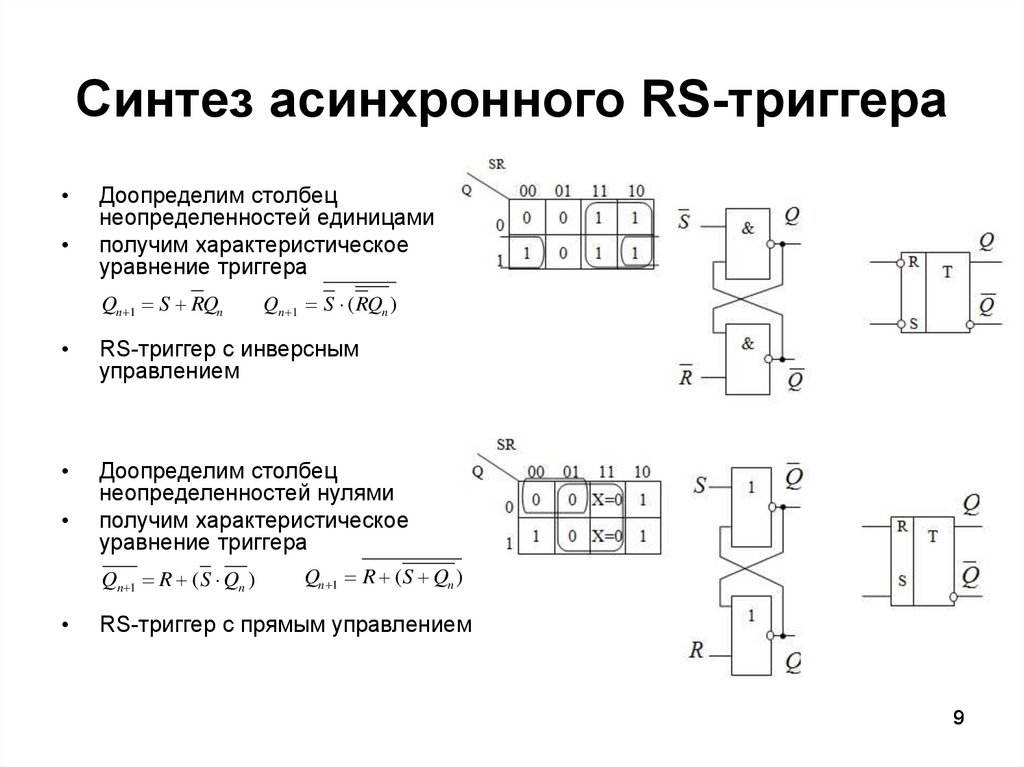

9. Синтез асинхронного RS-триггера

Доопределим столбец

неопределенностей единицами

получим характеристическое

уравнение триггера

Qn 1 S RQn

Qn 1 S ( RQn )

RS-триггер с инверсным

управлением

Доопределим столбец

неопределенностей нулями

получим характеристическое

уравнение триггера

Qn 1 R (S Qn )

Qn 1 R (S Qn )

RS-триггер с прямым управлением

9

10. Синхронный RS-триггер

Получается из асинхронного путем подключения к еговходам схемы управления.

Такт n

Такт n+1

S

С

Rn

Sn

Qn+1

C

0

0

0

Qn

R

0

1

0

Qn

0

0

1

Qn

0

1

1

Qn

1

0

0

Qn

1

1

0

0

1

0

1

1

1

1

1

х

&

&

S

R

T

Q

Q

10

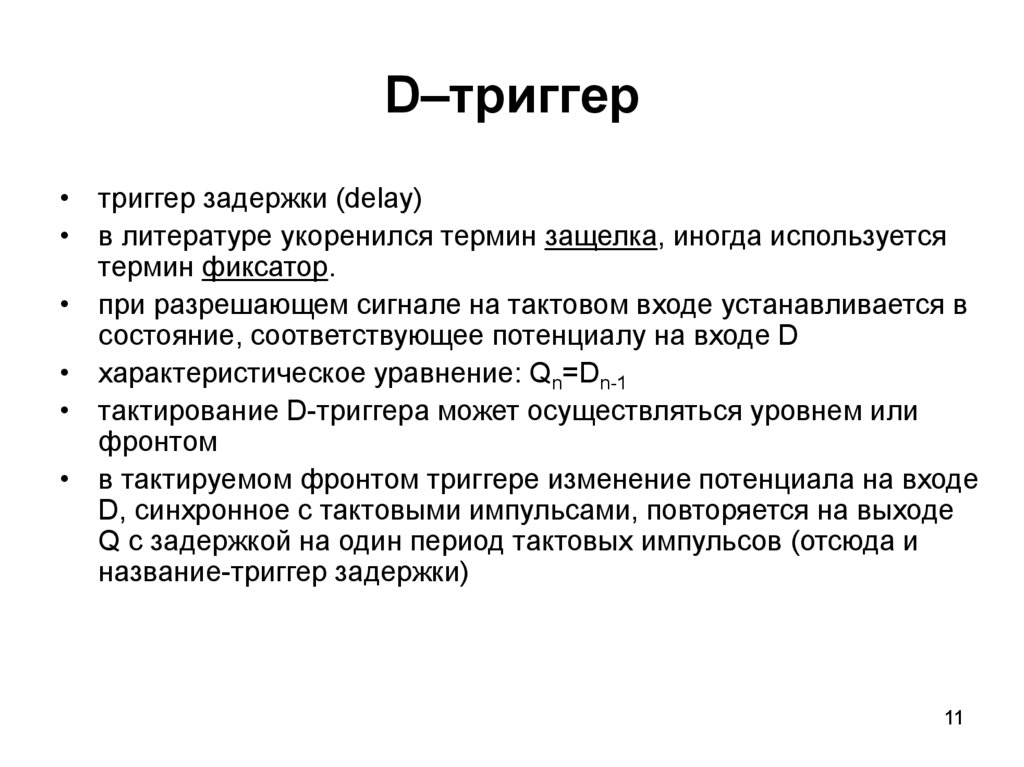

11. D–триггер

• триггер задержки (delay)• в литературе укоренился термин защелка, иногда используется

термин фиксатор.

• при разрешающем сигнале на тактовом входе устанавливается в

состояние, соответствующее потенциалу на входе D

• характеристическое уравнение: Qn=Dn-1

• тактирование D-триггера может осуществляться уровнем или

фронтом

• в тактируемом фронтом триггере изменение потенциала на входе

D, синхронное с тактовыми импульсами, повторяется на выходе

Q с задержкой на один период тактовых импульсов (отсюда и

название-триггер задержки)

11

12. Тактируемый уровнем D–триггер

на рисунке показаны: структурная схема, условное обозначение и

временная диаграмма тактируемого уровнем D-триггера.

благодаря инвертору невозможно запрещенное соотношение сигналов

на входах S и R.

12

13. Тактируемый фронтом D–триггер

Выходной сигнал Q сохраняется до прихода очередного тактового импульса.

Эта информация хранится в D-триггере, пока не придет следующий бит (0 или 1)

информации. По сути это ячейка памяти.

Если вход D замкнуть с инверсным выходом, то останется только один вход С.

При подаче на вход С импульсов триггер переключается в противоположное

состояние. Таким образом, триггер осуществляет деление частоты входных

импульсов на 2. В таком режиме D-триггер работает счетным или Т-триггером.

13

14. Т-триггер

• Триггер со счетным входом.• Имеет один управляющий вход Т и два

выхода Q и Q.

• Изменяет свое состояние на

Q

противоположное при каждом

положительном (или при каждом

отрицательном) перепаде напряжения на

входе Т.

• Характеристическое уравнение такого

триггера

n

T

Qn+1

0

Qn

1

Qn

Qn 1 T Qn

• Частота сигнала на выходе Т-триггера в

два раза ниже частоты сигнала на входе

(можно использовать как делитель

частоты и двоичный счетчик).

14

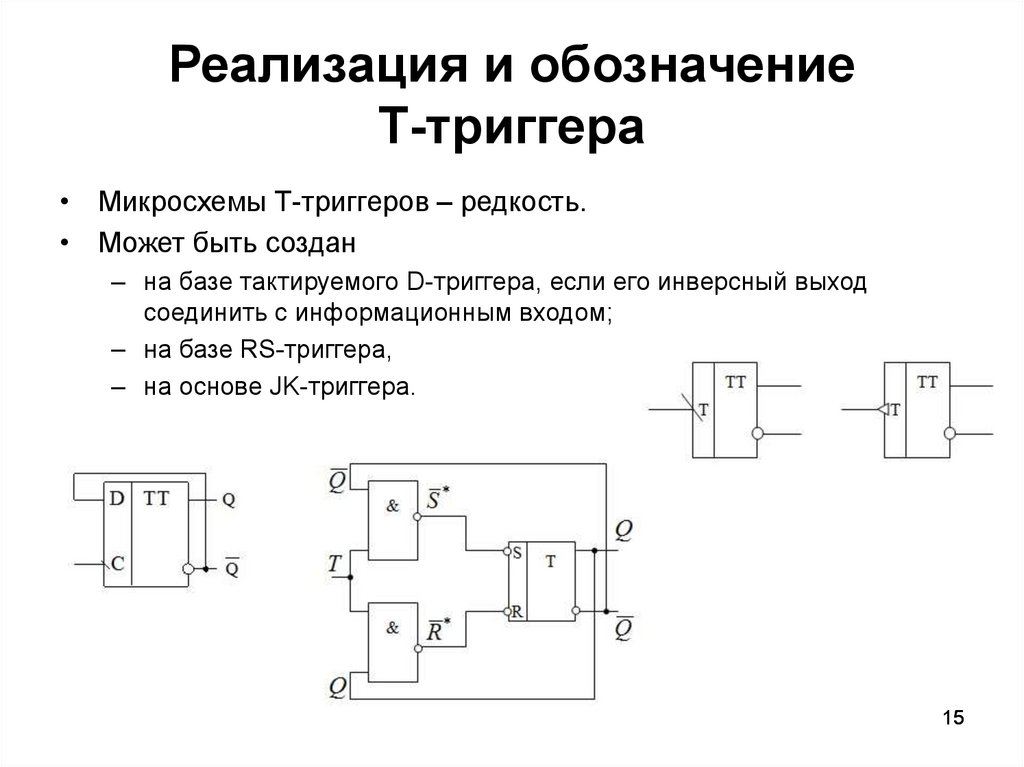

15. Реализация и обозначение Т-триггера

• Микросхемы Т-триггеров – редкость.• Может быть создан

– на базе тактируемого D-триггера, если его инверсный выход

соединить с информационным входом;

– на базе RS-триггера,

– на основе JK-триггера.

15

16. Универсальный JK-триггер

Не имеет неопределенных состояний:• при всех входных комбинациях, кроме

J = K = 1, подобен RS-триггеру, причем

вход J аналогичен S, а К - R-входу.

• при входной комбинации J = K = 1 в

каждом такте происходит

опрокидывание триггера, и выходные

сигналы меняют свое значение.

16

17. Функциональная схема, описание и обозначение JK-триггера

&&

J

S

T

S

T

Q

C

&

K

R

&

R

Q

J

K

Qn+1

0

0

Qn

0

1

0

1

0

1

1

1

Qn

Характеристическое уравнение

Qn 1 J Qn KQn

17

18. Универсальность JK-триггера

• Может использоваться в регистрах, счетчиках, делителяхчастоты и других узлах.

• Путем определенного соединения выходов он легко обращается

в триггеры других типов.

• Это позволяет промышленности сократить номенклатуру

триггеров, не сковывая в тоже время разработчиков

аппаратуры.

• Примеры: T-триггер, D-триггер.

T

J

C

K

T

Q

Q

D

1

J

C

K

T

Q

Q

18

19. Регистры

• Назначение – хранение и преобразованиемногоразрядных двоичных чисел.

• Используются в качестве:

– управляющих и запоминающих устройств,

– Являются составной частью регистровых файлов

в микропроцессорах (блоков регистров общего

назначения),

– генераторов и преобразователей кодов, счетчиков,

– делителей частоты,

– узлов временной задержки.

19

20. Классификация регистров

• По количеству линий передачи переменных– Однофазные

– Парафазные

• По системе синхронизации

– Однотактные

– Двухтактные

– Многотактные.

• По способу приема и выдачи данных

– параллельные (статические, регистры памяти)

– последовательные (регистры сдвига) регистры

– параллельно-последовательные.

20

21. По способу приема и выдачи данных

• В параллельных прием и выдача слов производится по всемразрядам одновременно. В них хранятся слова, которые могут

быть подвергнуты поразрядным логическим преобразованиям.

• В последовательных прием и считывание информации

производится в последовательном коде. Слова принимаются в

регистр поразрядно (т.е. последовательно во времени).

Считывание производится так же. Различают нереверсивные

(со сдвигом в одну сторону) и реверсивные регистры

(осуществляют сдвиг информации влево или вправо).

• Параллельно-последовательные имеют входы/выходы

одновременно последовательного и параллельного типа.

• Существуют варианты:

– с последовательным входом и параллельным выходом,

– с параллельным входом и последовательным выходом.

21

22. Параллельные регистры

• Cхемы разрядов необмениваются данными

между собой.

• Общими являются цепи

управления (тактирование,

сброс/установка,

разрешение на

запись/считывание,

• Здесь:

– D – входная шина данных;

– Q – выходная шина данных;

– С – разрешение на запись.

22

23. Пример с разрешением чтения

Здесь:• D – входная шина данных;

• Q – выходная шина данных;

• Y1 – разрешение на запись;

• Y1 – разрешение на чтение.

23

24. Пример со сбросом

2425. Условные обозначения регистров

В стандартные серии входит несколько типов параллельных регистров, срабатывающих по

фронту.

Различаются

–

–

–

–

–

количеством разрядов,

наличием или отсутствием инверсных выходов,

наличием или отсутствием входа сброса R,

наличием или отсутствием разрешения записи WE,

наличием или отсутствием входа разрешения выхода EZ.

Иногда на схемах тактовый вход С обозначается как WR - сигнал записи в регистр.

25

26. Схема вычисления разности двух последовательных значений входного кода

2627. Накапливающий сумматор

2728. Вычислитель экстремального значения входного кода

2829. Последовательные регистры (регистры сдвига)

• В регистрах сдвига триггеры соединены в последовательнуюцепочку (выход каждого предыдущего соединен со входом D

следующего.

• Тактовые входы С объединены между собой.

• Регистр может рассматриваться как линия задержки, входной

сигнал которой последовательно перезаписывается из триггера

в триггер по фронту тактового сигнала С.

• Информационные входы и выходы триггеров могут быть

выведены наружу.

29

30. Условные обозначения и разновидности

ИР8 - 8-разрядов. Входы объединены по функции И. Сдвиг в сторону выходов со старшими

номерами - по переднему фронту С. Вход сброса – R.

ИР9 - функция, обратная ИР8. Преобразует входной параллельный код в

последовательный Запись кода в регистр - по нулевому сигналу на WR. Сдвиг - по

положительному фронту на одном из двух тактовых входов С1 и С2. Вход расширения DR,

сигнал с которого перезаписывается в освободившийся разряд.

ИР13 имеет управляющие входы SR (правый) и SL (левый сдвиг).

ИР24 - близок к ИР13, но имеет двунаправленную параллельную шину данных с

повышенной нагрузочной способностью. Это позволяет легко сопрягать его с

многоразрядными микросхемами памяти. Сдвиг в обоих направлениях. Входы расширения

DR и DL, а также выходы расширения Q0 и Q7 для наращивания разрядности.

30

31. Объединение регистров для увеличения разрядности

3132. Последовательная передача информации

3233. Генератор псевдослучайной последовательности

Практическая схема генератора псевдослучайной последовательности на 31-разрядном

сдвиговом регистре.

Обратная связь осуществляется с выходов 30 и 17 регистра через двухвходовой элемент

Исключающее ИЛИ с инвертором.

Генератор выдает квазислучайную последовательность 31-разрядных кодов со всех

выходов регистра, а также квазислучайную последовательность нулей и единиц на любом

из выходов регистра.

Такой генератор использовала известная фирма Hewlett–Packard в своем генераторе шума.

33

34. Счетчики

• Счетчик - устройство, на выходе которого в заданномкоде отображается количество импульсов,

поступивших на счетный вход.

• Пример простейшего счетчика – Т-триггер (считает

до двух).

• Счетчик, образованный цепочкой из m-триггеров

(разрядов), сможет посчитать в двоичном коде 2m

импульсов.

• Каждый из триггеров цепочки называют разрядом

счетчика.

• Число Ксч=2m называют коэффициентом (модулем)

счета.

34

35. Пример работы 4-разрядного двоичного счетчика

Информация снимается с прямых и (или) инверсных выходов всех

триггеров. В паузах между входными импульсами триггеры сохраняют

свое состояние.

Второе назначение счетчиков - деление числа входных импульсов.

Если частота импульсов fвх , то частота выходных импульсов

fвых= fвх/Ксч.

На схемах обозначают буквами СТ (от counter – счетчик), иногда

проставляют модуль СТ2.

35

36. Основные параметры счетчиков

Основные эксплуатационные показатели: емкость ибыстродействие:

• Емкость равна коэффициенту счета – число импульсов,

доступное счету за единицу цикла.

• Быстродействие определяется разрешающей способностью tразр

– минимальное время между двумя входными сигналами пока

не возникают сбои в работе счетчика.

• Обратная величина fmax=1/tразр. называется максимальной

частотой счета.

• Время установки кода tуст равно времени между моментом

поступления входного сигнала и переходом счетчика в новое

состояние.

Временные свойства зависят от временных характеристик

триггеров и способа их соединения между собой.

36

37. Классификация счетчиков

• По коэффициенту счета:–

–

–

–

двоичные;

двоично-десятичные (декадные) или с другим основанием счета;

с произвольным постоянным модулем;

с переменным модулем.

• По направлению счета:

– суммирующие;

– вычитающие;

– реверсивные.

• По способу организации внутренних связей:

–

–

–

–

с последовательным переносом;

с параллельным переносом;

с комбинированным переносом;

кольцевые.

37

38. Двоичные счетчики

Ксч=2m.

В суммирующем счетчике каждый

входящий импульс увеличивает

состояние счетчика на 1.

В вычитающем – уменьшает на 1.

Реверсивный счетчик может работать в

качестве сумматора и вычитателя. Эти

счетчики имеют дополнительные входы

управления.

Из таблицы видно, что триггер каждого

разряда переключается с частотой в 2

раза меньшей, чем триггер предыдущего

разряда.

В случае прямого счета это переключение

осуществляется по перепаду 1→0, а в

случае обратного счета - по перепаду

0→1.

Следовательно, счетчик можно построить

как цепочку последовательно

соединенных счетных триггеров

N

состояние

Суммирование

Q3

Q2

Q

0

0

0

0

1

0

0

2

0

3

Вычитание

Q3

Q2

Q1

0

0

0

0

1

7

1

1

1

1

0

6

1

1

0

0

1

1

5

1

0

1

4

1

0

0

4

1

0

0

5

1

0

1

3

0

1

1

6

1

1

0

2

0

1

0

7

1

1

1

1

0

0

1

0

0

0

0

0

0

0

0

38

39. Прямой и обратный счет с последовательным переносом

• Цепочка триггеров, в которой импульсы, подлежащие счету,поступают на вход первого триггера, а сигнал переноса

передается последовательно от одного разряда к другому.

• Главное достоинство таких счетчиков – простота схемы.

• Такой счетчик мало нагружает предыдущий каскад.

• Недостаток – сравнительно низкое быстродействие.

39

40. Счетчик с параллельным переносом

• При поступлении входного сигнала переключаются те триггеры,для которых все предыдущие триггеры находились в единичном

состоянии.

• Конъюнкторы анализируют состояние предыдущих разрядов.

• Время установления кода определяется временем

переключения одного триггера и одного конъюнктора.

40

41. Счетчик со сквозным переносом

Здесь время установления кода tУСТ = tТР + (m-1)tИ.41

42. Счетчики – делители

• Направление счета не имеет значения.• Имеются в составе многих серий МС.

• Номенклатуру счетчиков отличает большое

разнообразие.

• Многие из них обладают универсальными

свойствами и позволяют управлять:

–

–

–

–

коэффициентом и направлением счета,

вводить до начала цикла исходное число,

прекращать счет по команде,

наращивать число разрядов и т. п.

42

43. Десятичные счетчики

• Введением дополнительных логических связей (обратных ипрямых) двоичные счетчики могут быть обращены в недвоичные

– десятичные (декадные).

• Десятичный счет осуществляется в двоично-десятичном коде.

• Десятичные счетчики организуют из 4-разрядных двоичных

счетчиков. Избыточные 6 состояний исключаются введением

дополнительных связей.

• Счет циклически идет от 0000 до 1001.

43

44. Кольцевой счетчик

Может быть использован сдвигающий регистр, замкнутый в кольцо цепью

обратной связи.

Продвигается одна единица, которая при подаче очередного продвигающего

импульса передается в следующую по порядку ячейку.

Дойдя до конца регистра, единица записывается в первую ячейку и счет

повторяется.

Число импульсов фиксируется позицией единицы в регистре (унитарный код).

Такой счетчик носит название кольцевой регистр с простой обратной связью.

Модуль счета равен числу триггеров.

1

D TT

D TT

D TT

C

C

C

2

D TT

3

C

44

45. Условные обозначения и разновидности счетчиков

• 4-х разрядный двоично-десятичный ИЕ2–

Имеет две части: один триггер (С1, выход 1) и три триггера (С2, выходы 2, 4, 8). Таким

образом, он состоит из одноразрядного и трехразрядного счетчиков. При объединении

выхода 1 с С2 мы получаем 4-разрядный двоично-десятичный счетчик.

• 4-х разрядный двоичный ИЕ5

–

Имеет две части: одноразрядный счетчик со входом С1 и выходом 1 и трехразрядный

счетчик с С2 и выходами 2, 4, 8. При объединении С2 с 1 получается 4-разрядный

двоичный счетчик, считающий до 16.

• 8-и разрядный (сдвоенный 4-х разрядный) двоичный ИЕ19

– можно считать сдвоенным вариантом счетчика ИЕ5

45

46. Наращивание разрядности счетчиков

Нужно выход предыдущего счетчика соединить со входом С1 следующего.

Показано соединение трех счетчиков для получения 12-разрядного

асинхронного счетчика со сбросом в нуль.

При объединении надо помнить, что добавление каждого нового разряда

увеличивает общую задержку переключения полученного счетчика.

46

47. Делитель частоты на 10, выдающий меандр

В делителе использован счетчик ИЕ2, у которого одноразрядный внутренний

счетчик включен после трехразрядного внутреннего счетчика.

Трехразрядный счетчик делит частоту на 5, но выходные импульсы имеют

скважность, не равную двум (она равна 5).

Одноразрядный счетчик делит частоту еще вдвое и одновременно формирует

меандр.

47

48. Делитель частоты на 9

• При достижении выходным кодом значения 9 (1001) счетчикавтоматически сбрасывается в нуль по входам R1 и R2, и счет

начинается снова.

• В результате частота выходного сигнала в 9 раз меньше частоты

входного сигнала. При этом скважность выходного сигнала не

равна двум.

48

49. Управляемый делитель частоты

Делитель на 2n, где n - целое.

Выходной 8-входовый мультиплексор передает на выход схемы один

из 7 разрядов счетчика или же входной сигнал.

Выбор номера канала производится входным управляющим 3разрядным кодом.

При тактовой частоте fT = 10 МГц, то есть при периоде входного

сигнала 100 нс период выходного сигнала может составлять 100 нс,

200 нс, 400 нс, 800 нс, 1,6 мкс, 3,2 мкс, 6,4 мкс, 12,8 мкс.

49

50. Реверсивные счетчики

5051. Формирователь временного интервала

Если входной код равен 1, то длительность выходного сигнала

составит от Т до 2Т, где Т - период тактового сигнала.

Если входной код равен N (до 255), то длительность выходного сигнала

составит от NT до (N+1)T в зависимости от момента прихода входного

сигнала по отношению к тактовому сигналу.

Абсолютная погрешность выдержки длительности выходного сигнала в

любом случае не превышает периода тактового сигнала Т.

51

52. Измеритель длительности входного сигнала

Отсчитываем импульсы

тактового кварцевого

генератора в течение

длительности входного

сигнала.

После окончания

входного сигнала в

счетчике остается код,

пропорциональный

длительности этого

сигнала.

t = NT, где T - период

тактового сигнала.

Абсолютная

погрешность измерения

не превышает величины

±Т. Для уменьшения

относительной

погрешности

необходимо

увеличивать частоту

тактового генератора и

увеличивать

разрядность счетчика.

52

53. Арифметическое устройство

Если на все управляющие входы подать низкий потенциал, то к входу

сумматора будут подключены коды A и B без инверсии. Будет

производиться операция суммирования (первые две строки таблицы).

Вычитание осуществляется во 2, 3, 8 и 9 строке. Один из операндов

поступает на вход сумматора через блок инверторов. Для получения

дополнительного кода не хватает единицы, но её можно подать на вход

переноса сумматора PI.

Увеличение числа на единицу или уменьшение числа на единицу (строки

4, 7, 16 и 25.

Схема может передавать на выход любой из входных кодов без

изменения, что позволяет осуществлять копирование данных

(суммирование с константой ноль) через это устройство без

дополнительных схем коммутации.

53

54. Схема арифметического устройства

5455. Арифметико-логическое устройство

№ операцииСостояние входов S

Состояние входа М

S3

S2

S1

S0

M=1

M=0 (С=0)

1

0

0

0

0

А

А\/1

2

0

0

0

1

А+B

(А+B)\/1

3

0

0

1

0

А+B

(А+B)\/1

4

0

0

1

1

0

0

5

0

1

0

0

А+B

(А\/A)x(B\/1)

6

0

1

0

1

B

(А+B)\/A(B\/1)

7

0

1

1

0

АxB\/AxB

A-B

8

0

1

1

1

AxB

AxB

9

1

0

0

0

A+B

A\/AxB\/1

10

1

0

0

1

AxB+AxB

A\/B\/1

11

1

0

1

0

B

(A+B)\/AxB\/1

12

1

0

1

1

AxB

AxB

13

1

1

0

0

1

A\/A\/1

14

1

1

0

1

A+B

(A+B)\/A1\/1

15

1

1

1

0

A+B

(A+B)\/A\/1

16

1

1

1

1

А

A

55

56. Пример обобщенной схемы ядра микропроцессора

5657. Структура Intel 8051

5758. Литература

Маевская Е.А. Схемотехника цифровыхустройств: Электронный образовательный

ресурс УрФУ. Екатеринбург: УрФУ, 2011. 99с.

Лекции 5, 6.

58

Электроника

Электроника