Похожие презентации:

Программируемые логические устройства: CPLD и FPGA с дизайном VHDL

1.

Перевод: английский - русский - www.onlinedoctranslator.comПрограммируемые логические

устройства:

CPLD и FPGA с дизайном VHDL

Лекция3

Цифровая Электроника

2.

Материалы курсаВсе необходимое программное

обеспечение и материалы курса будут

размещенына холсте.

◻ Материалы, использованные в этих

слайдах, взяты из учебника «Цифровая

электроника: практический подход с VHDL»

Уильяма Клейца.

◻

3.

логические устройства:CPLD, FPGA с VHDLдизайном

Трудно производить различные логические

◻

ИС

◻ отвечают всем требованиям сложных

цифровых схем

◻

чрезмерное количество площади на

печатной плате

◻ ИС для каждой отдельной логической функции

◻ использовались только 1 или 2 вентиля на

четырехъядерном чипе

◻

программируемое логическое устройство

(ПЛУ)

4.

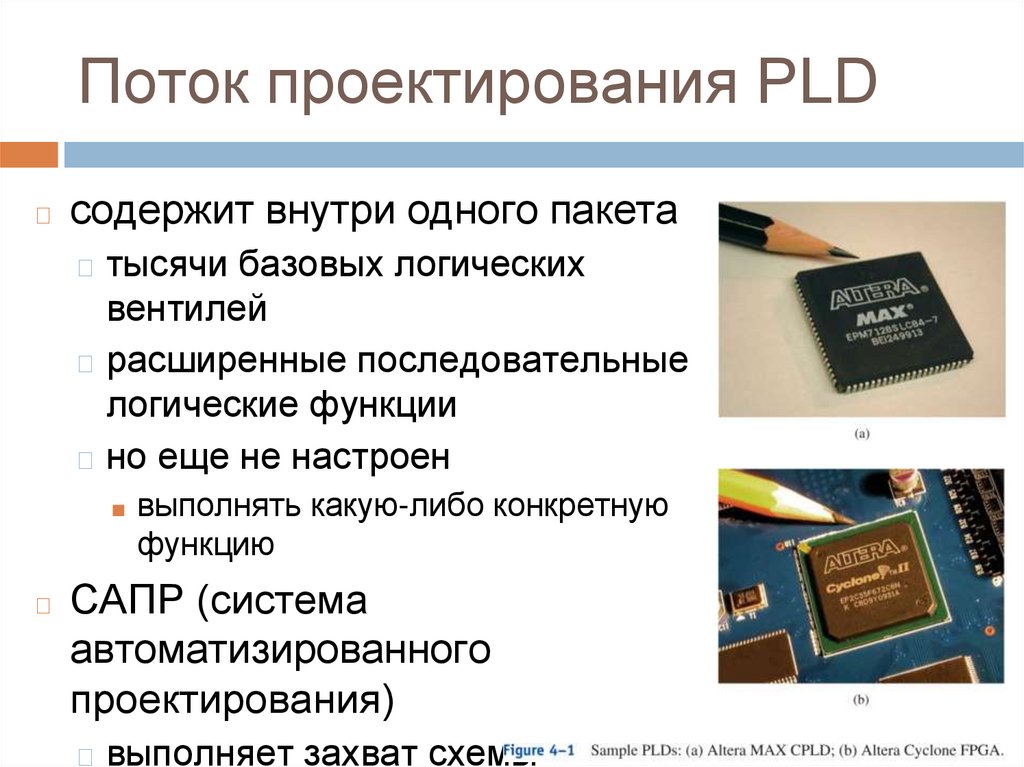

Поток проектирования PLD◻

содержит внутри одного пакета

◻ тысячи базовых логических

вентилей

◻ расширенные последовательные

логические функции

◻ но еще не настроен

■ выполнять какую-либо конкретную

функцию

◻

САПР (система

автоматизированного

проектирования)

◻ выполняет захват схемы

5.

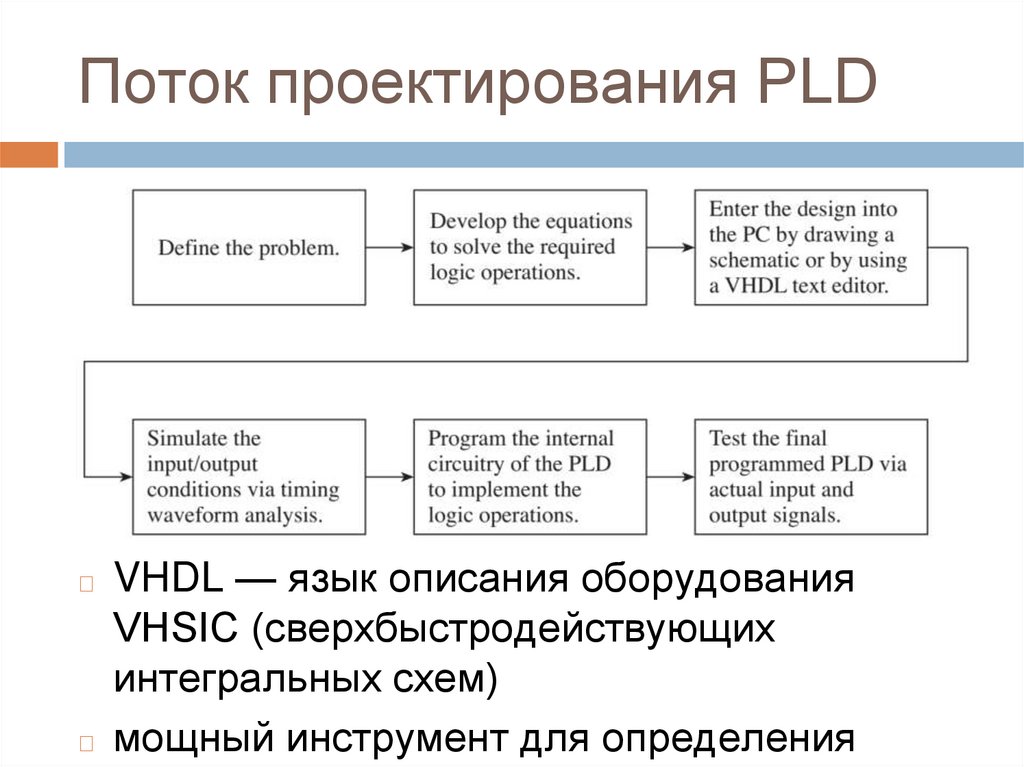

Поток проектирования PLDVHDL — язык описания оборудования

VHSIC (сверхбыстродействующих

интегральных схем)

◻ мощный инструмент для определения

◻

6.

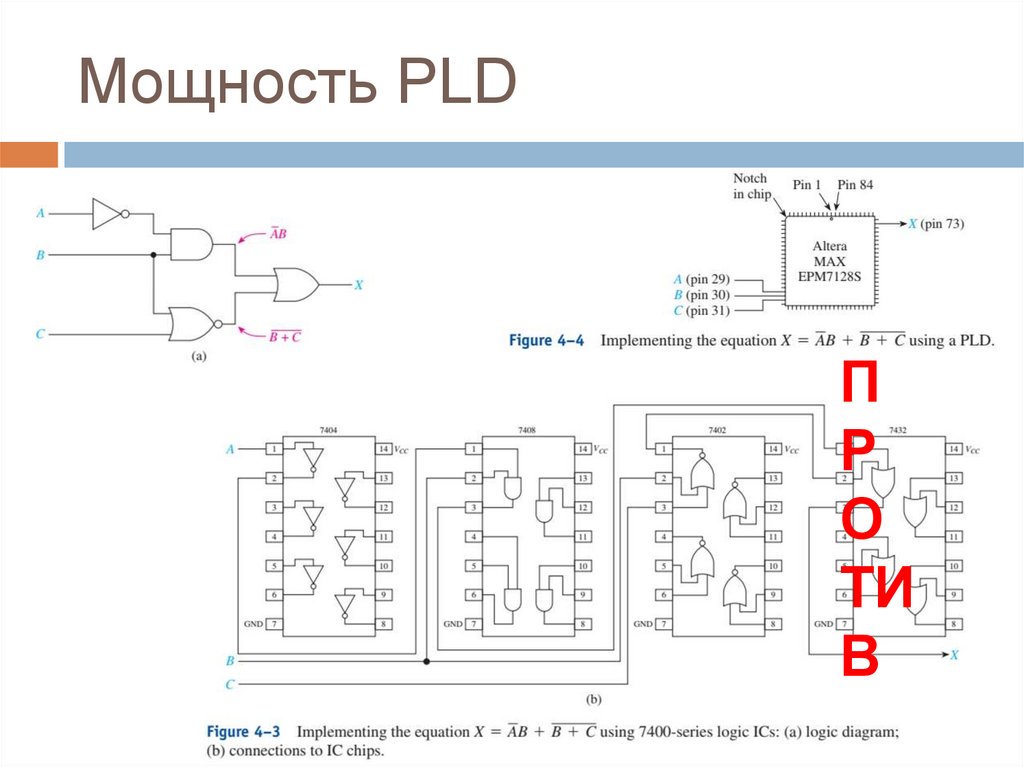

Мощность PLDП

Р

О

ТИ

В

7.

◻◻

◻

стираемый и

перепрограммируемый

Единственное ограничение —

количество входных и выходных

контактов.

Плата, которую мы будем

использовать, — это плата

разработки и обучения Altera

DE2.

◻

Почему мы выбрали Altera

Corporation

один из ведущих производителей

ПЛИС

◻ высокий уровень поддержки

колледжей и университетов

◻ бесплатная версия программного

обеспечения для проектирования

и разработки (Quartus II: Web

Edition)

◻

8.

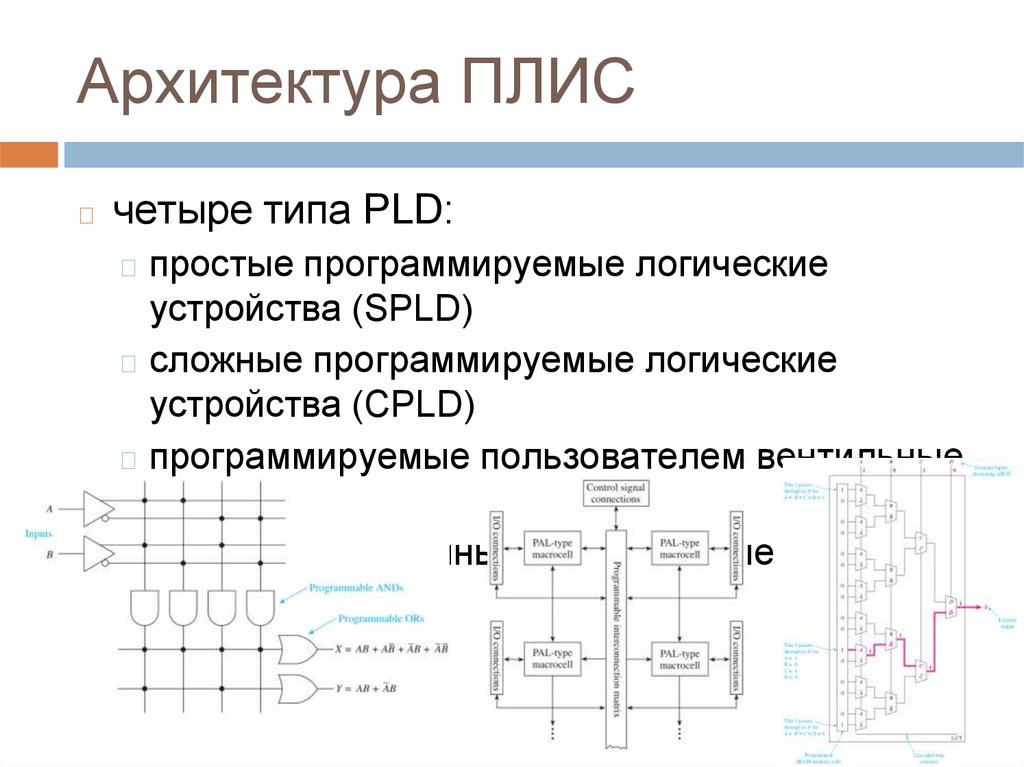

Архитектура ПЛИС◻

четыре типа PLD:

◻ простые программируемые логические

устройства (SPLD)

◻ сложные программируемые логические

устройства (CPLD)

◻ программируемые пользователем вентильные

матрицы (ПЛИС)

◻ специализированные интегральные схемы

(ASIC)

9.

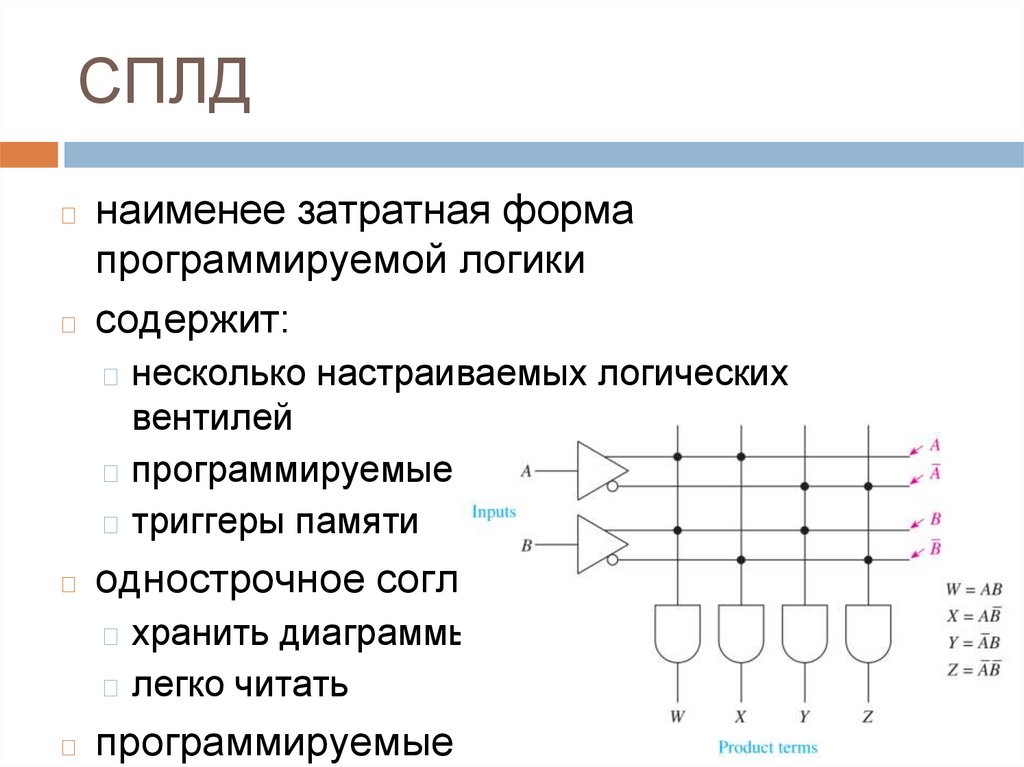

СПЛДнаименее затратная форма

программируемой логики

◻ содержит:

◻

◻ несколько настраиваемых логических

вентилей

◻ программируемые точки соединения

◻ триггеры памяти

◻

однострочное соглашение

◻ хранить диаграммы

◻ легко читать

◻

программируемые И

10.

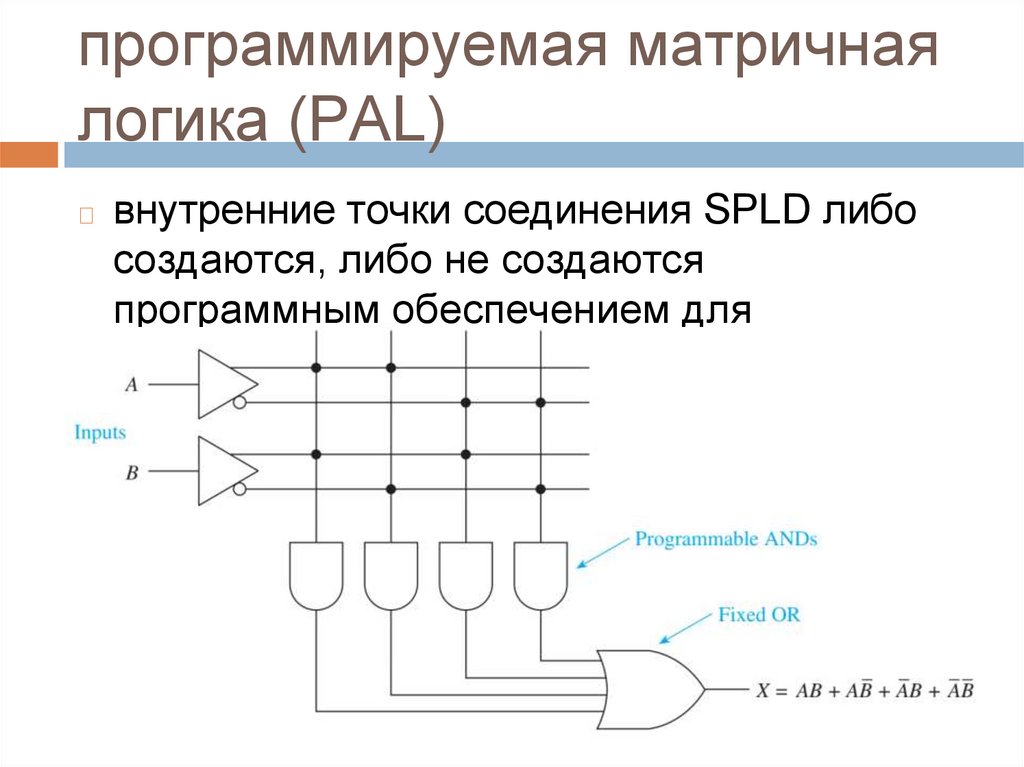

программируемая матричнаялогика (PAL)

◻

внутренние точки соединения SPLD либо

создаются, либо не создаются

программным обеспечением для

программирования PLD

11.

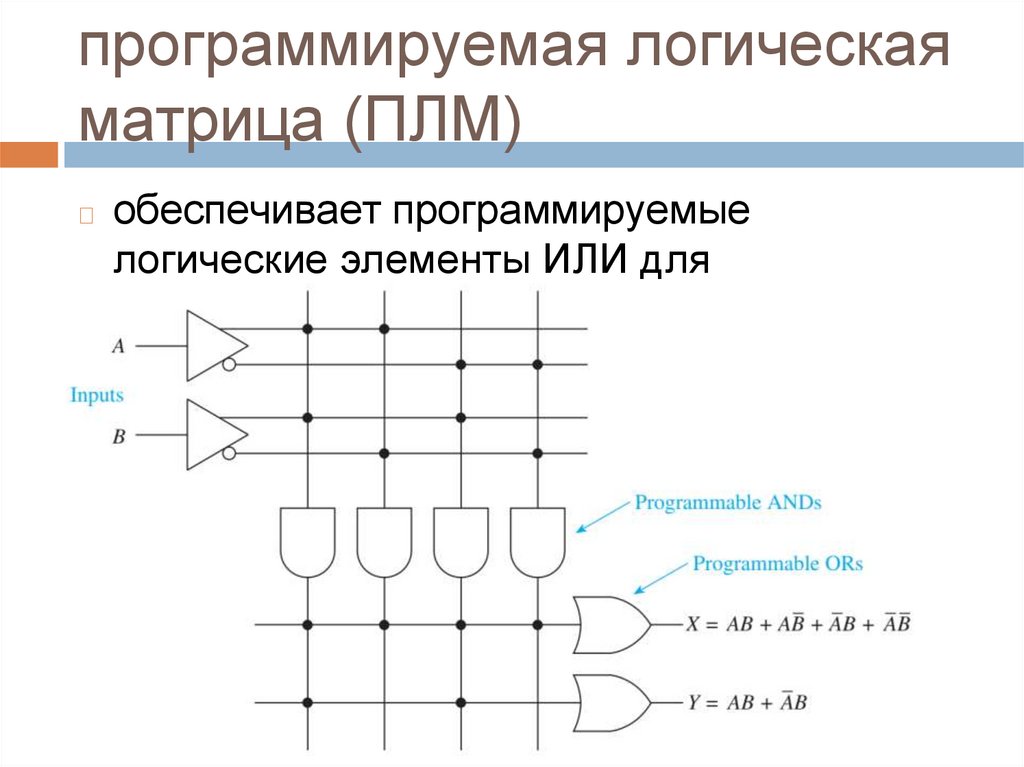

программируемая логическаяматрица (ПЛМ)

◻

обеспечивает программируемые

логические элементы ИЛИ для

объединения терминов продукта

12.

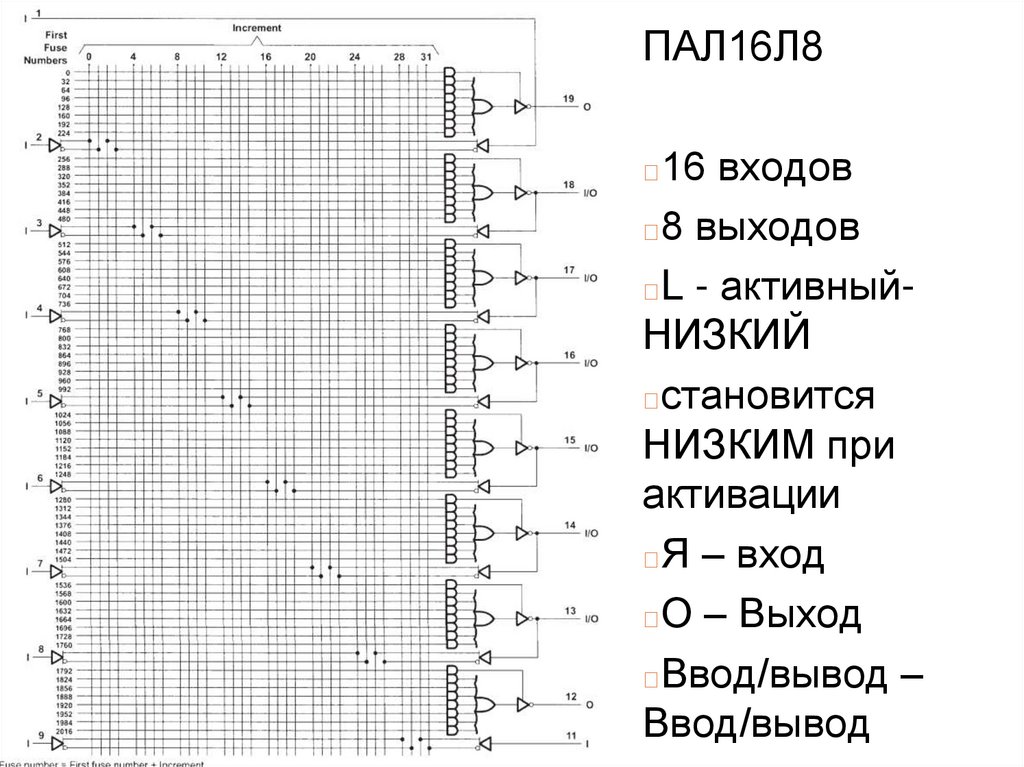

ПАЛ16Л816 входов

◻8 выходов

◻L - активныйНИЗКИЙ

◻становится

НИЗКИМ при

активации

◻Я – вход

◻О – Выход

◻Ввод/вывод –

Ввод/вывод

◻

13.

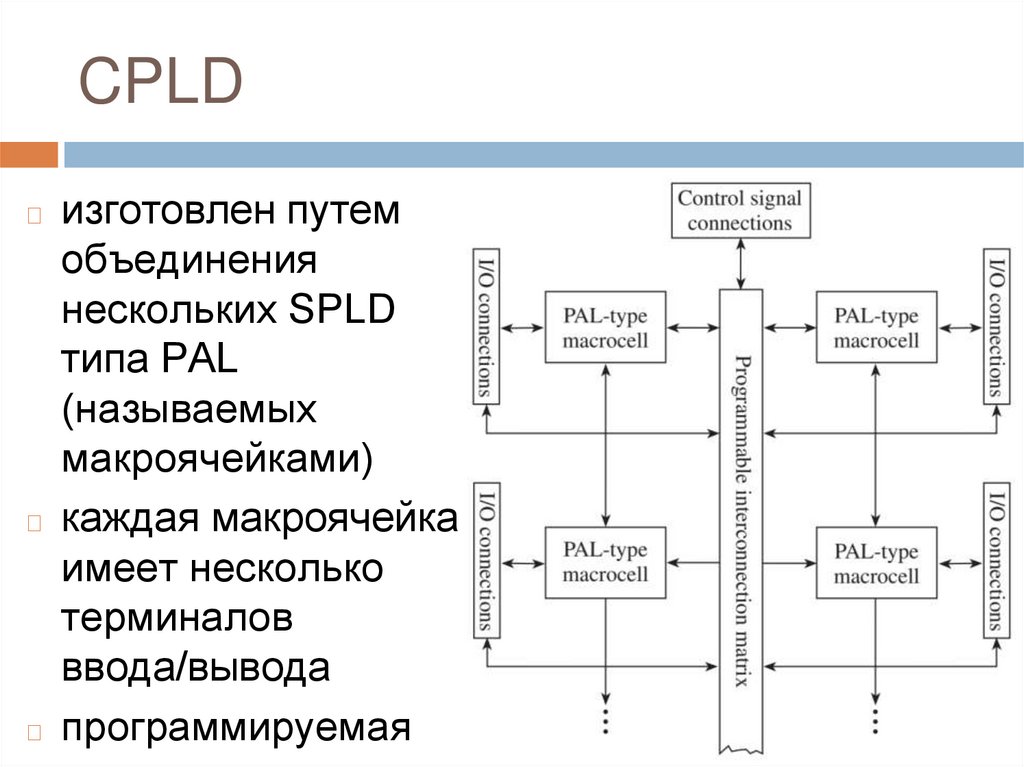

CPLDизготовлен путем

объединения

нескольких SPLD

типа PAL

(называемых

макроячейками)

◻ каждая макроячейка

имеет несколько

терминалов

ввода/вывода

◻ программируемая

◻

14.

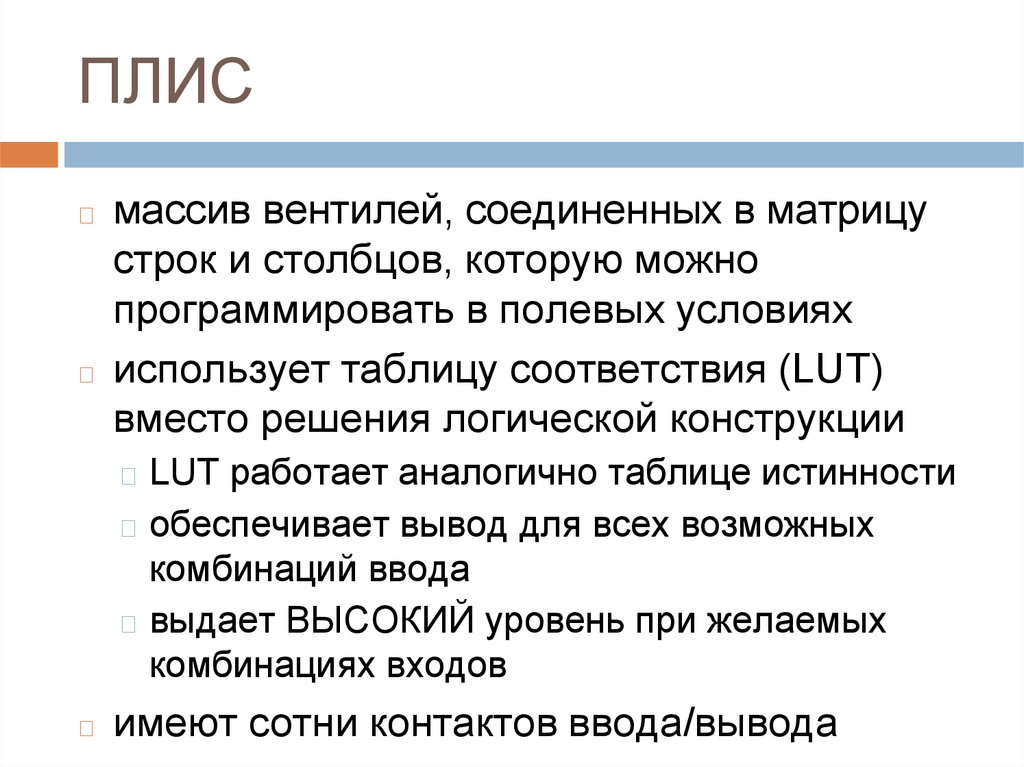

ПЛИСмассив вентилей, соединенных в матрицу

строк и столбцов, которую можно

программировать в полевых условиях

◻ использует таблицу соответствия (LUT)

вместо решения логической конструкции

◻

◻ LUT работает аналогично таблице истинности

◻ обеспечивает вывод для всех возможных

комбинаций ввода

◻ выдает ВЫСОКИЙ уровень при желаемых

комбинациях входов

◻

имеют сотни контактов ввода/вывода

15.

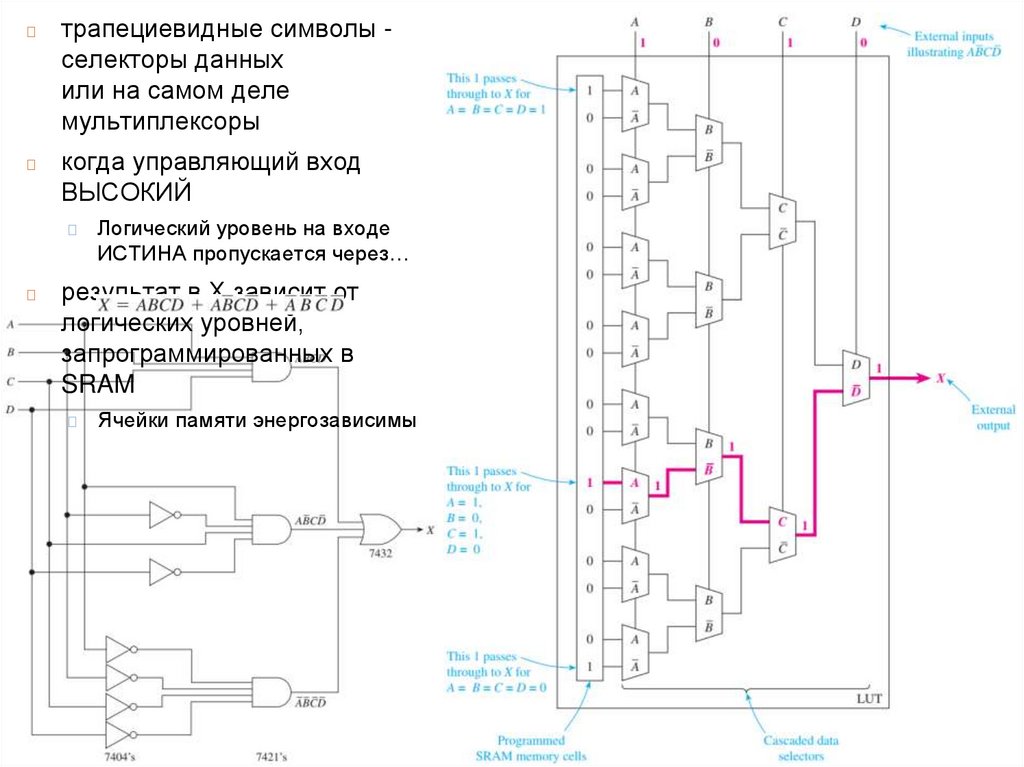

◻◻

трапециевидные символы селекторы данных

или на самом деле

мультиплексоры

когда управляющий вход

ВЫСОКИЙ

◻

◻

Логический уровень на входе

ИСТИНА пропускается через…

результат в X зависит от

логических уровней,

запрограммированных в

SRAM

◻

Ячейки памяти энергозависимы

16.

специализированнаяинтегральная схема (ASIC)

◻

Проект, созданный и протестированный на

ПЛИС, можно перенести на ASIC

◻ если есть большой объем спроса

логическая функция жестко закодирована в

ИС

◻ энергонезависимая — пользователю не

нужно перенастраивать ИС при каждом

включении питания

◻ Плата разработки Altera DE-2 содержит

ПЛИС

◻

◻ Циклон EP2C35F672C6N

17.

Обзорные вопросы1.

2.

3.

4.

ПЛИС использует __________ вместо

решения логической схемы?

ЛПВП означает _____________________?

__________ (PLA / PAL) предоставляет

программируемые логические элементы

ИЛИ для объединения терминов

продукта?

Ячейки памяти в ПЛИС энергозависимы.

Правда / Ложь?

18.

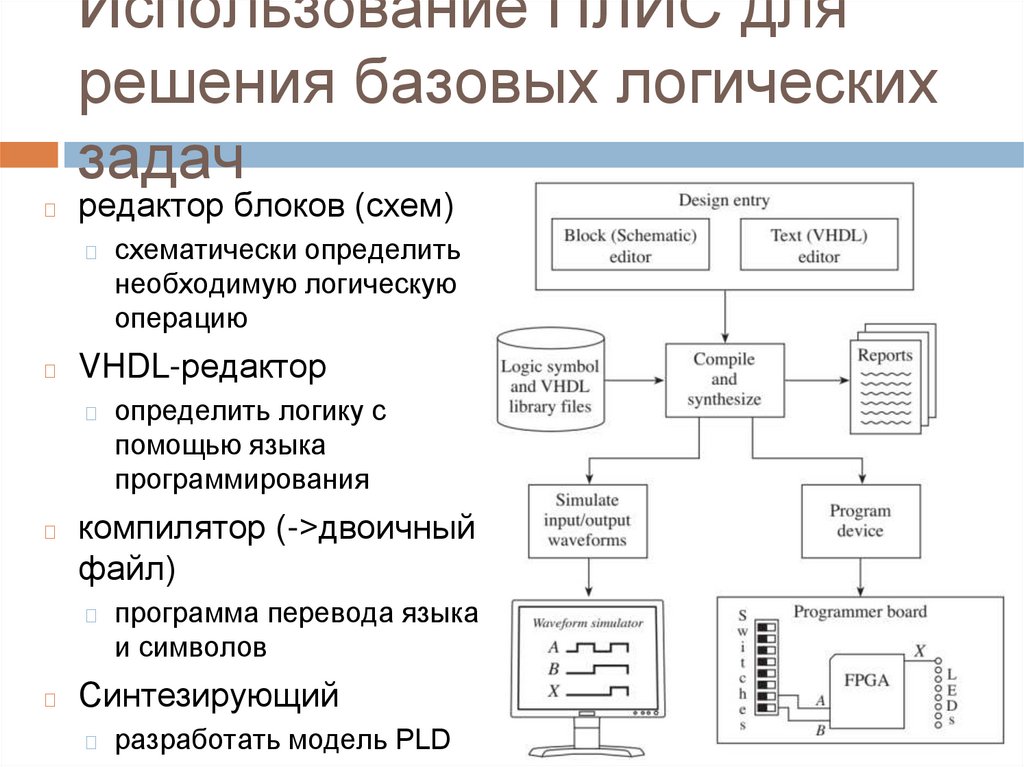

Использование ПЛИС длярешения базовых логических

задач

◻

редактор блоков (схем)

◻

◻

VHDL-редактор

◻

◻

определить логику с

помощью языка

программирования

компилятор (->двоичный

файл)

◻

◻

схематически определить

необходимую логическую

операцию

программа перевода языка

и символов

Синтезирующий

◻

разработать модель PLD

19.

Использование ПЛИС длярешения базовых логических

задач

◻

Отчетные файлы

◻ Назначение контактов

ввода/вывода,

◻ внутренняя маршрутизация

сигналов ПЛИС

◻ сообщения об ошибках

◻

симулятор формы волны

◻ предоставляет средства

для проверки логической

работы проекта

◻ показывает выходной

отклик, как если бы

воображаемые входы были

применены к реальной

20.

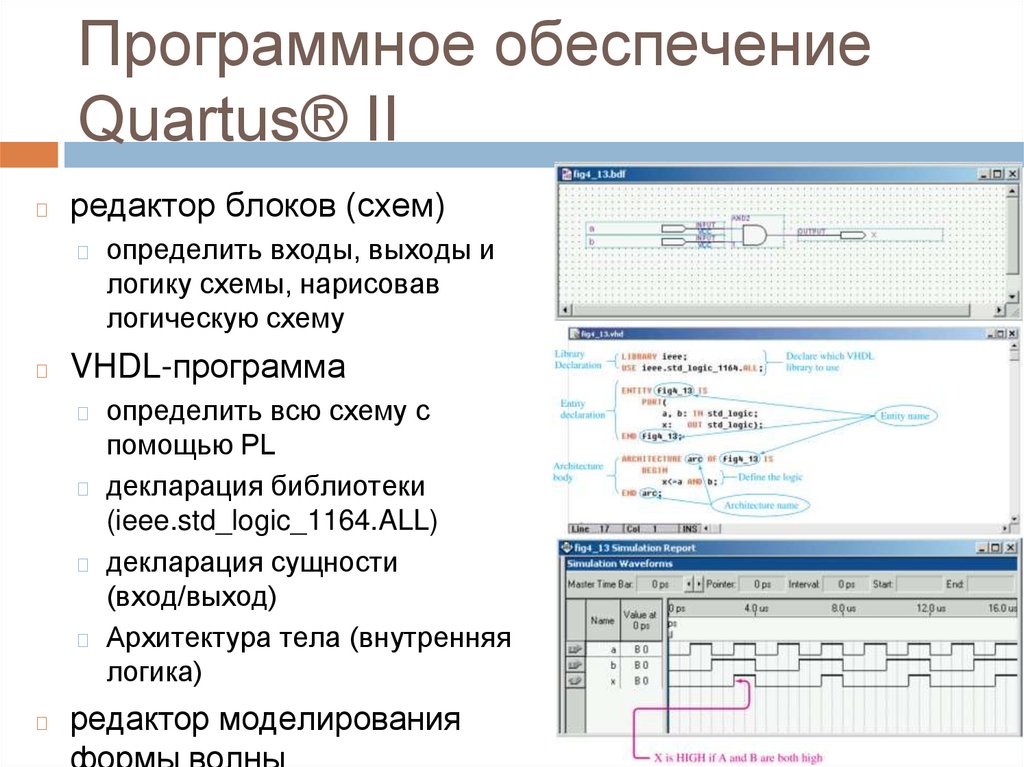

Программное обеспечениеQuartus® II

◻

редактор блоков (схем)

◻

◻

определить входы, выходы и

логику схемы, нарисовав

логическую схему

VHDL-программа

определить всю схему с

помощью PL

◻ декларация библиотеки

(ieee.std_logic_1164.ALL)

◻ декларация сущности

(вход/выход)

◻ Архитектура тела (внутренняя

логика)

◻

◻

редактор моделирования

21.

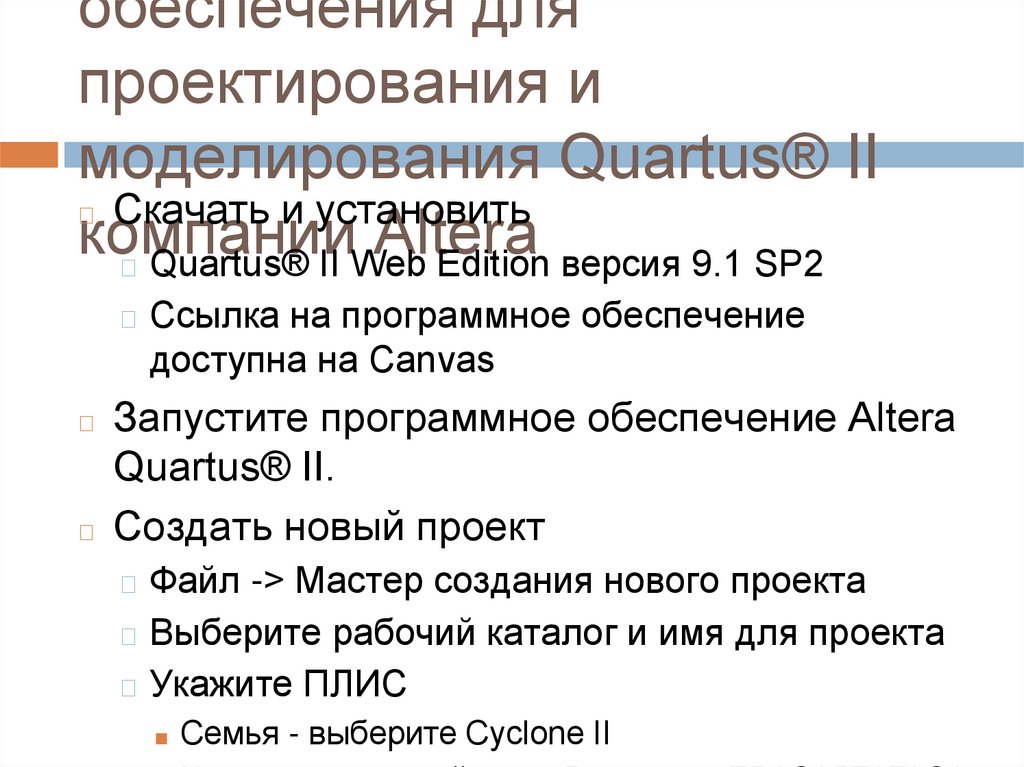

обеспечения дляпроектирования и

моделирования Quartus® II

Скачать и установить

компании

Altera

◻ Quartus® II Web Edition версия 9.1 SP2

◻

◻ Ссылка на программное обеспечение

доступна на Canvas

Запустите программное обеспечение Altera

Quartus® II.

◻ Создать новый проект

◻

◻ Файл -> Мастер создания нового проекта

◻ Выберите рабочий каталог и имя для проекта

◻ Укажите ПЛИС

■ Семья - выберите Cyclone II

22.

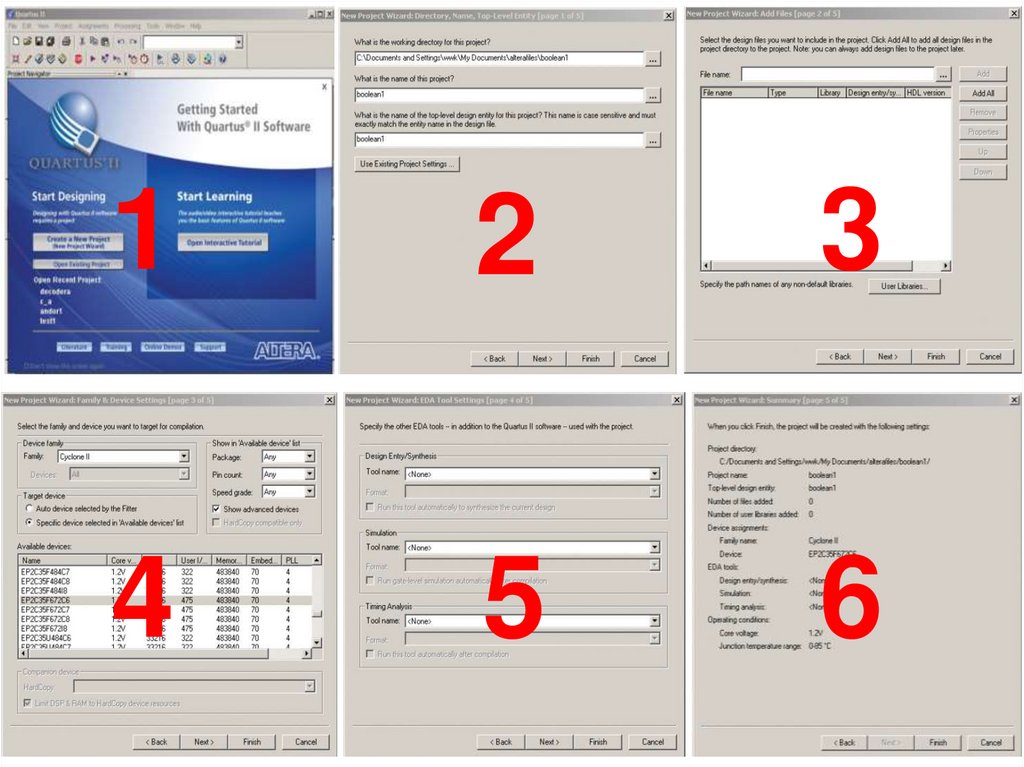

12

3

4

5

6

23.

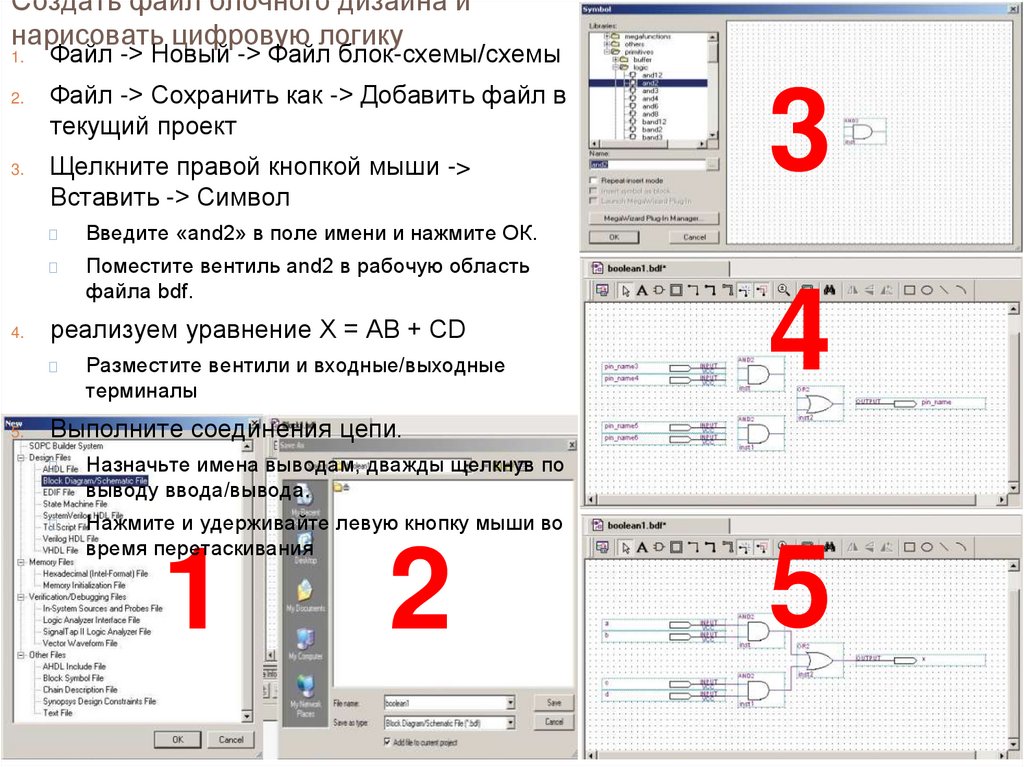

Создать файл блочного дизайна инарисовать цифровую логику

1.

2.

3.

4.

Файл -> Новый -> Файл блок-схемы/схемы

Файл -> Сохранить как -> Добавить файл в

текущий проект

Щелкните правой кнопкой мыши ->

Вставить -> Символ

◻

Введите «and2» в поле имени и нажмите ОК.

◻

Поместите вентиль and2 в рабочую область

файла bdf.

реализуем уравнение X = AB + CD

◻

5.

Разместите вентили и входные/выходные

терминалы

3

4

Выполните соединения цепи.

◻

Назначьте имена выводам, дважды щелкнув по

выводу ввода/вывода.

◻

Нажмите и удерживайте левую кнопку мыши во

время перетаскивания

1

2

5

24.

Компиляция и создание файлавекторной формы сигнала

1.

1

2.

4

3

3.

4.

5.

Обработка -> Начать компиляцию

Файл -> Создать -> Файлы

проверки/отладки -> Файл векторной

формы сигнала -> ОК, Сохранить

Изменить -> Время окончания -> 16 мкс > ОК

Редактировать -> Размер сетки ->

Период -> 1 мкс -> ОК

Вид -> По размеру окна

◻

2

перебрать все возможные комбинации

входных данных и получить

результирующий вывод

5

25.

1.Добавьте входы и выходы, создайте

временные формы сигналов,

выполните функциональное

моделирование

Вид

-> Утилиты -> Windows Node

изобразить входной сигнал в виде часов с

◻

периодом

Finder

Фильтр: Запись о дизайне -> Список

◻

Выберите вход (a, b, c, d)

перетащите имена входов и выходов

с экрана Node Finder на экран

векторной формы сигнала

◻

Правка -> Значение -> Часы

◻

Введите период (2 мкс для a, 4 мкс для b, 8 мкс

для c, 16 мкс для d)

◻

Нажмите ОК, затем Сохранить.

◻

2.

1

2

3

26.

Выполнить функциональноемоделирование

◻

◻

Задания -> Настройки

◻

Настройки симулятора ->

Режим симуляции ->

Функционал -> ОК

◻

◻

◻

Обработка -> Генерация

функционала -> Список

соединений моделирования ->

ОК

Обработка -> Начать

моделирование

Вид -> По размеру окна

X ВЫСОКИЙ, если оба A И B

ВЫСОКИЕ ИЛИ если оба C И

D ВЫСОКИЕ

27.

Назначение пиновПлата DE2 имеет несколько переключателей,

кнопок и светодиодов, жестко подключенных к

определенным контактам на ПЛИС.

◻ назначить определенные номера контактов

входам и выходам

◻ столбцы помечены последовательно (1..26)

◻ строки используют буквы (26 строк)

◻

◻ A..Y (пропустить I, O, Q и X)

◻ плюс АА..АФ

28.

◻Задания -> Зажимы

◻

введите номера контактов в столбце Местоположение

Перекомпилируйте проект: Обработка -> Начать

компиляцию

◻ Запрограммируйте ПЛИС на плате DE2: Инструменты ->

Программатор

◻

29.

Обзорные вопросы1.

2.

3.

___________ (редактор блоков, программа

VHDL) определяет необходимую

логическую операцию схематически?

Симулятор формы волны предоставляет

средства для проверки логической работы

проекта. True / Flase ?

Названия выводов ПЛИС содержат буквы,

которые обозначают ________

(строка/столбец), и цифры, которые

обозначают __________ (строка/столбец)?

30.

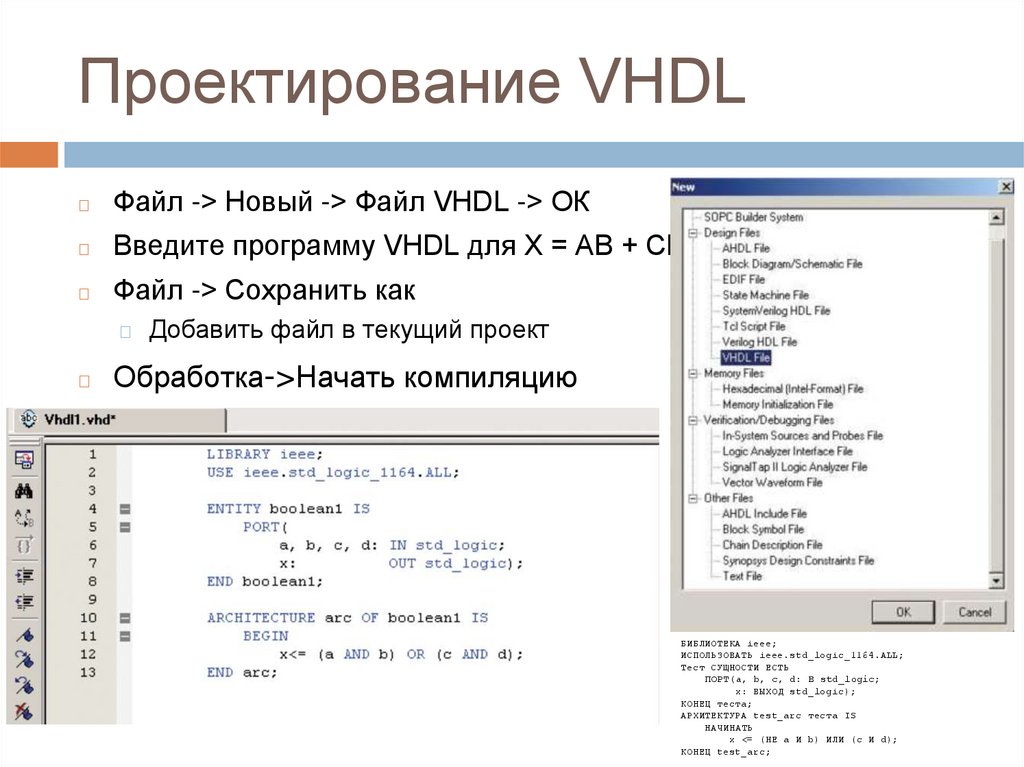

Проектирование VHDL◻

Файл -> Новый -> Файл VHDL -> ОК

◻

Введите программу VHDL для X = AB + CD

◻

Файл -> Сохранить как

◻

◻

Добавить файл в текущий проект

Обработка->Начать компиляцию

БИБЛИОТЕКА ieee;

ИСПОЛЬЗОВАТЬ ieee.std_logic_1164.ALL;

Тест СУЩНОСТИ ЕСТЬ

ПОРТ(a, b, c, d: В std_logic;

х: ВЫХОД std_logic);

КОНЕЦ теста;

АРХИТЕКТУРА test_arc теста IS

НАЧИНАТЬ

x <= (НЕ a И b) ИЛИ (c И d);

КОНЕЦ test_arc;

31.

Справочник языка VHDL◻

синтаксические правила и формат языка

базовой программы

32.

Соглашения об именованиипрограмм, сущностей и

архитектур и комментарии

имена могут состоять из букв, цифр и

подчеркивания

◻ имя должно начинаться с буквы и не может

содержать пробелов, дефисов, точек

◻ слова, которым предшествует двойной

дефис (--), считаются комментарием

◻ используется для документации

◻

33.

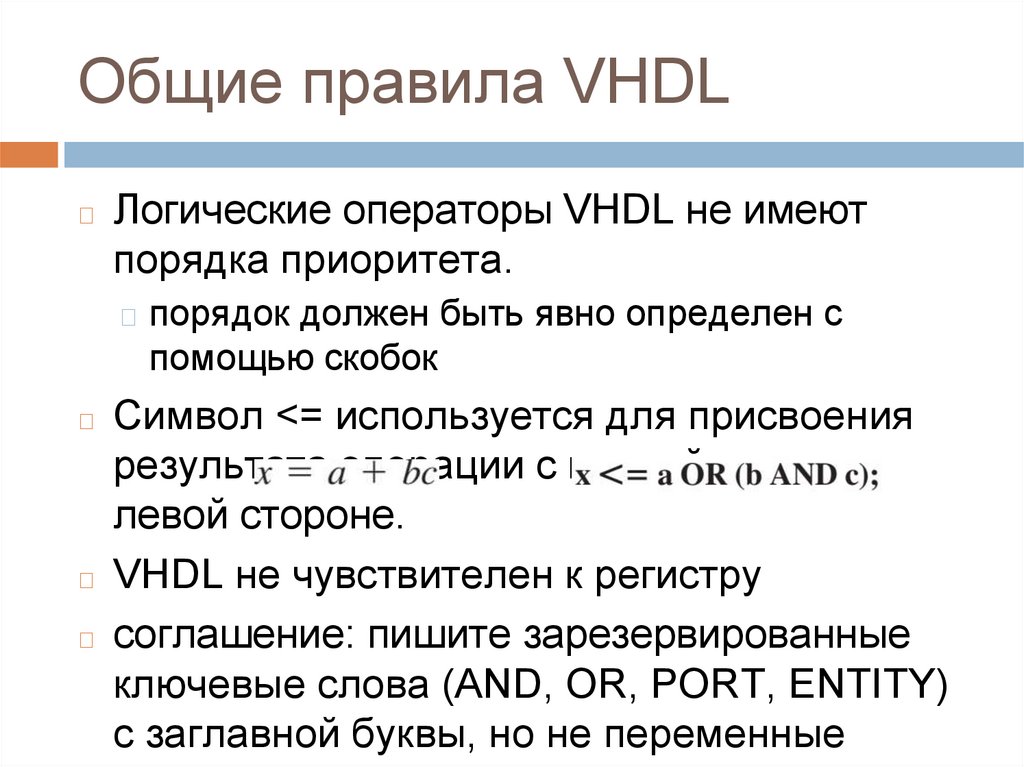

Общие правила VHDL◻

Логические операторы VHDL не имеют

порядка приоритета.

◻ порядок должен быть явно определен с

помощью скобок

Символ <= используется для присвоения

результата операции с правой стороны

левой стороне.

◻ VHDL не чувствителен к регистру

◻ соглашение: пишите зарезервированные

ключевые слова (AND, OR, PORT, ENTITY)

с заглавной буквы, но не переменные

◻

34.

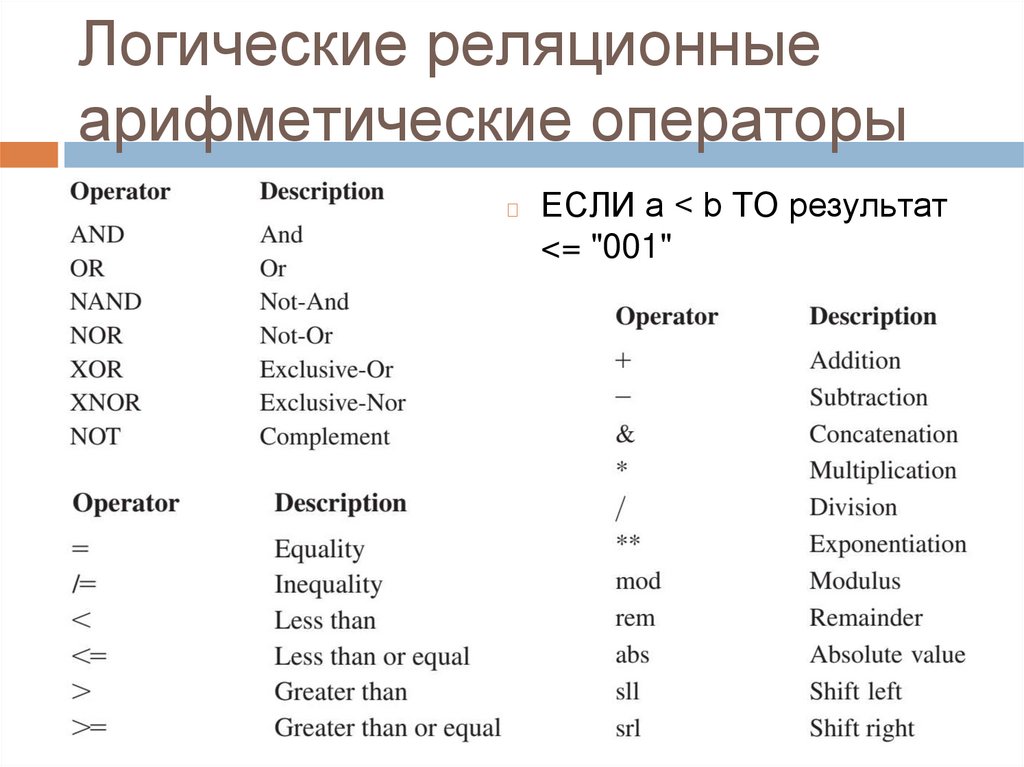

Логические реляционныеарифметические операторы

◻

ЕСЛИ а < b ТО результат

<= "001"

35.

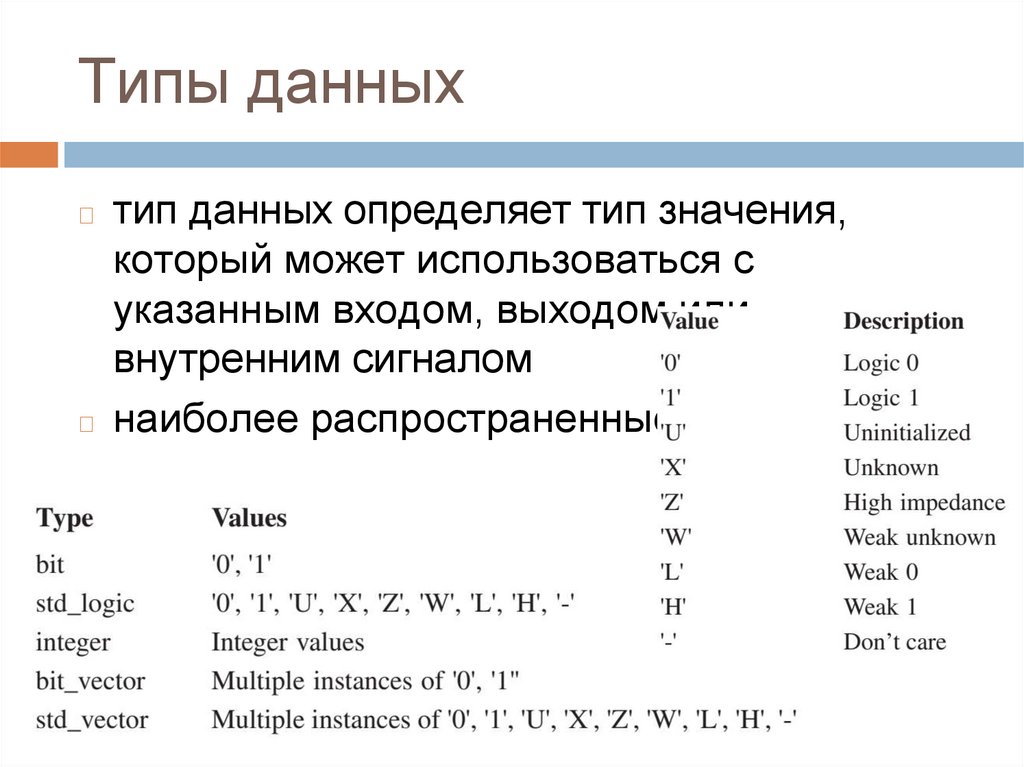

Типы данныхтип данных определяет тип значения,

который может использоваться с

указанным входом, выходом или

внутренним сигналом

◻ наиболее распространенные типы данных

◻

36.

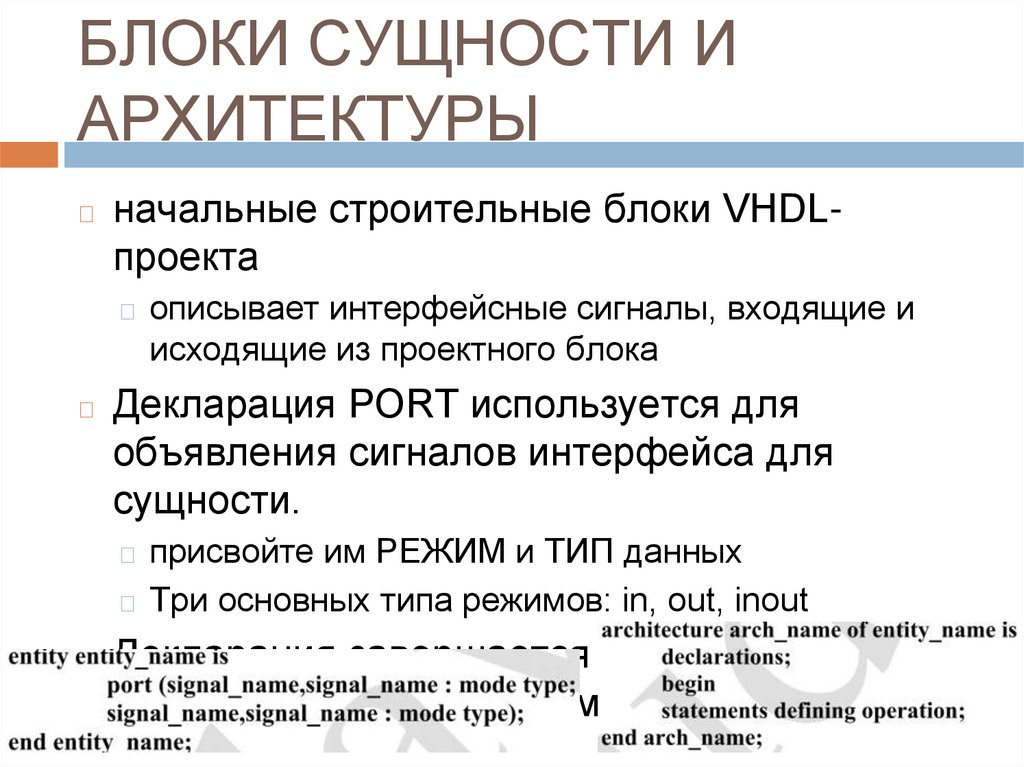

БЛОКИ СУЩНОСТИ ИАРХИТЕКТУРЫ

◻

начальные строительные блоки VHDLпроекта

◻ описывает интерфейсные сигналы, входящие и

исходящие из проектного блока

◻

Декларация PORT используется для

объявления сигналов интерфейса для

сущности.

◻ присвойте им РЕЖИМ и ТИП данных

◻ Три основных типа режимов: in, out, inout

◻

Декларация завершается с помощью

конечного оператора и имени сущности.

37.

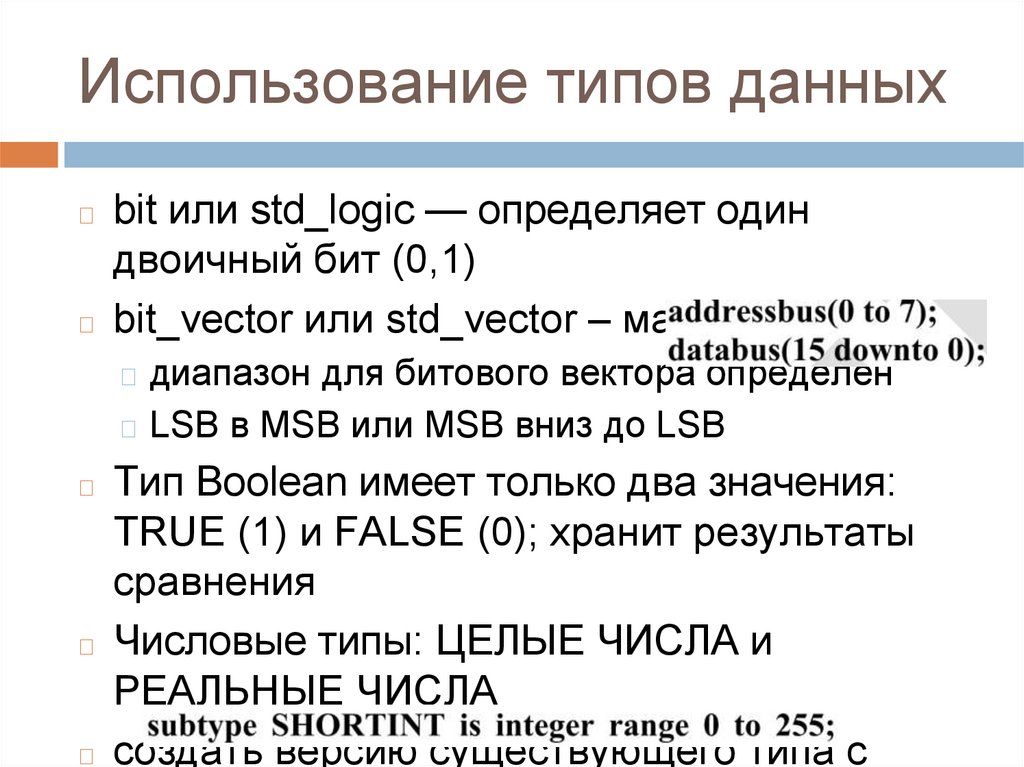

Использование типов данныхbit или std_logic — определяет один

двоичный бит (0,1)

◻ bit_vector или std_vector – массив бит

◻

◻ диапазон для битового вектора определен

◻ LSB в MSB или MSB вниз до LSB

Тип Boolean имеет только два значения:

TRUE (1) и FALSE (0); хранит результаты

сравнения

◻ Числовые типы: ЦЕЛЫЕ ЧИСЛА и

РЕАЛЬНЫЕ ЧИСЛА

◻ создать версию существующего типа с

◻

38.

Другие типы данных◻

Оператор TYPE используется для создания

и определения пользовательских типов.

Синтаксис: TYPE имя_типа (значения

типов);

◻ ТИП МЕСЯЦЕВ (ЯНВ, ФЕВ, МАР, АПР, МАЙ,

ИЮН, ИЮЛ, АВГ, СЕН, ОКТ, НОЯБ, ДЕК);

◻

дополнительные типы данных

◻ доступ - действует как указательный тип

◻ файл - используется для доступа к файлу

◻ физические - конечные величины, такие как

время, напряжение…

39.

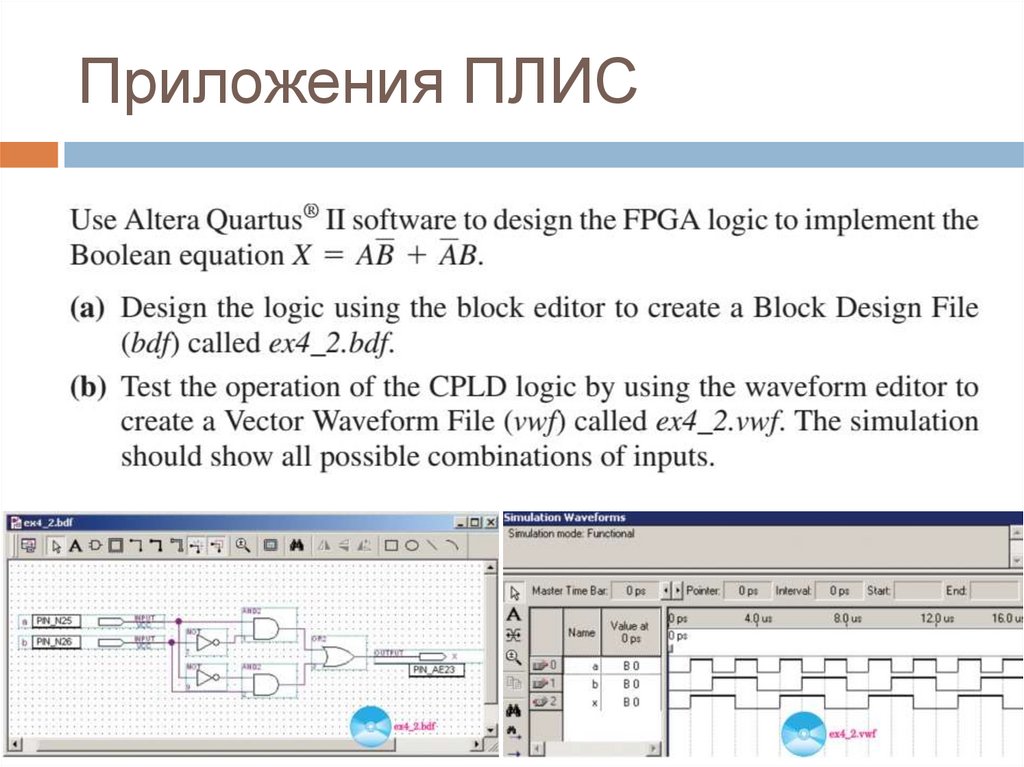

Приложения ПЛИС40.

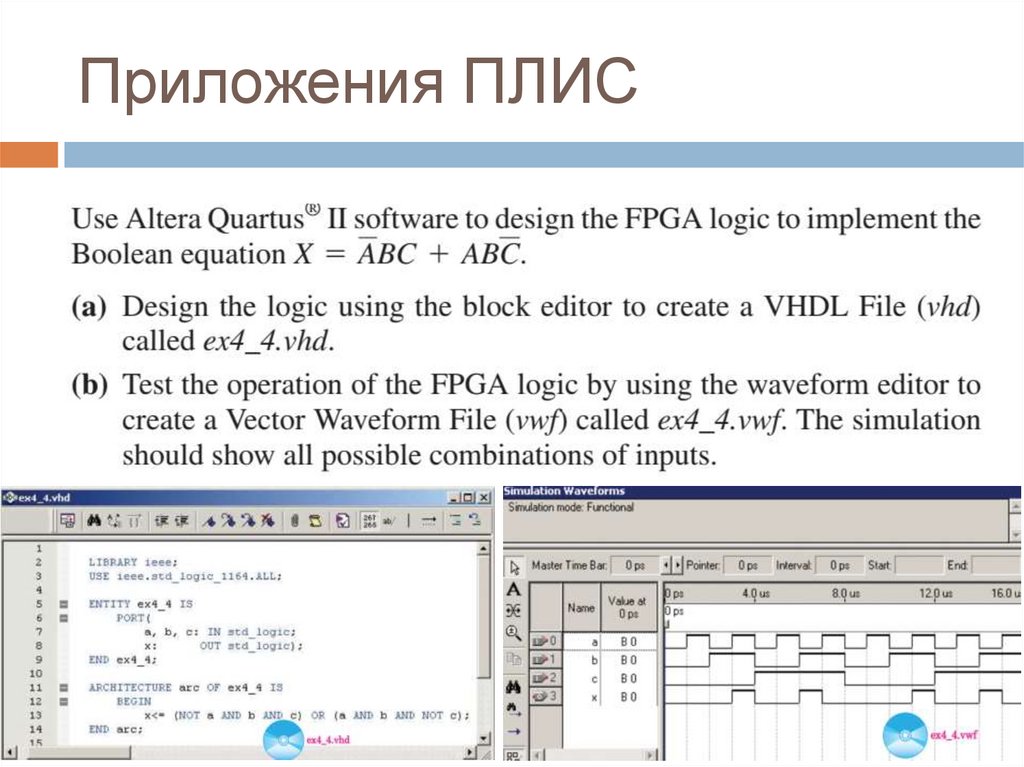

Приложения ПЛИС41.

Обзорные вопросы1.

2.

3.

4.

Как создаются комментарии в VHDL?

Тип данных _________ определяет только

два значения (0,1)?

Оператор __________ используется для

присвоения результата операции с правой

стороны левой стороне?

Оператор ___________ (ТИП, ПОДТИП)

используется для создания и определения

типов пользователей?

42.

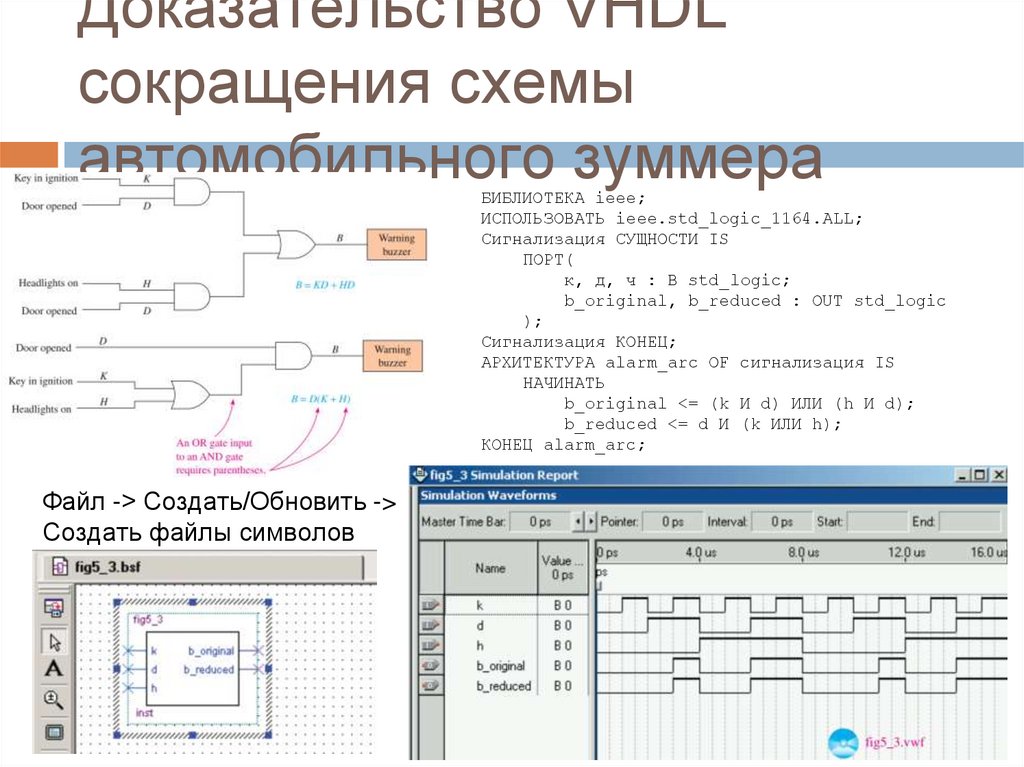

Доказательство VHDLсокращения схемы

автомобильного зуммера

БИБЛИОТЕКА ieee;

ИСПОЛЬЗОВАТЬ ieee.std_logic_1164.ALL;

Сигнализация СУЩНОСТИ IS

ПОРТ(

к, д, ч : В std_logic;

b_original, b_reduced : OUT std_logic

);

Сигнализация КОНЕЦ;

АРХИТЕКТУРА alarm_arc OF сигнализация IS

НАЧИНАТЬ

b_original <= (k И d) ИЛИ (h И d);

b_reduced <= d И (k ИЛИ h);

КОНЕЦ alarm_arc;

Файл -> Создать/Обновить ->

Создать файлы символов

43.

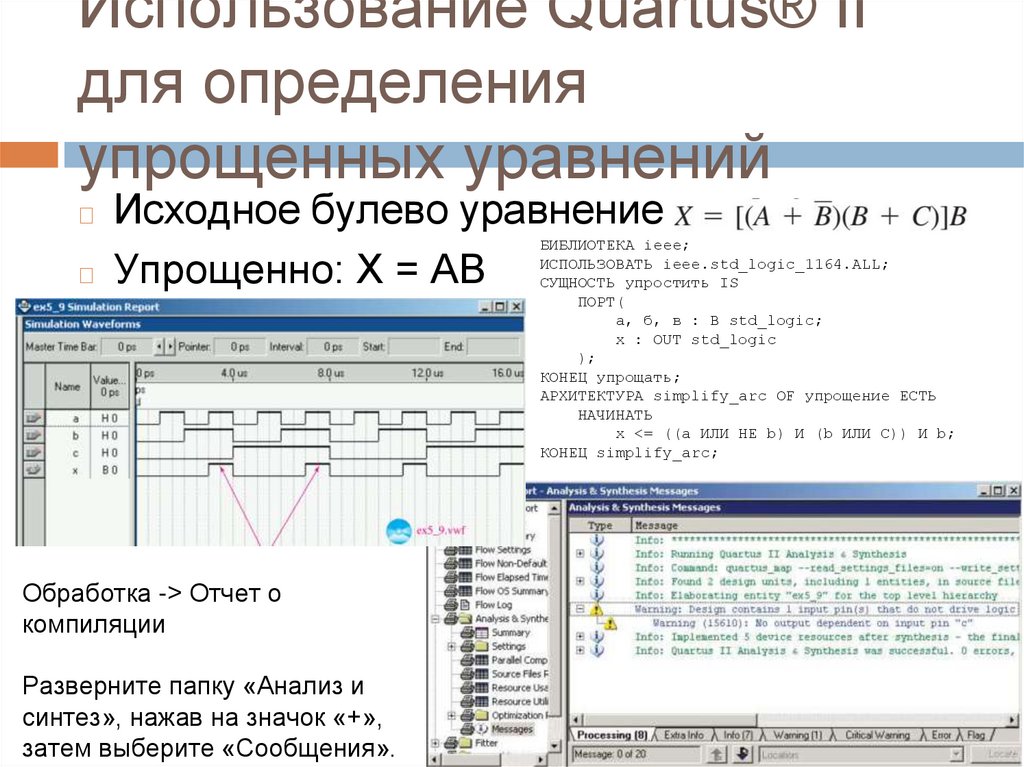

Использование Quartus® IIдля определения

упрощенных уравнений

Исходное булево уравнение

◻ Упрощенно: X = AB

◻

БИБЛИОТЕКА ieee;

ИСПОЛЬЗОВАТЬ ieee.std_logic_1164.ALL;

СУЩНОСТЬ упростить IS

ПОРТ(

а, б, в : В std_logic;

x : OUT std_logic

);

КОНЕЦ упрощать;

АРХИТЕКТУРА simplify_arc OF упрощение ЕСТЬ

НАЧИНАТЬ

x <= ((a ИЛИ НЕ b) И (b ИЛИ C)) И b;

КОНЕЦ simplify_arc;

Обработка -> Отчет о

компиляции

Разверните папку «Анализ и

синтез», нажав на значок «+»,

затем выберите «Сообщения».

44.

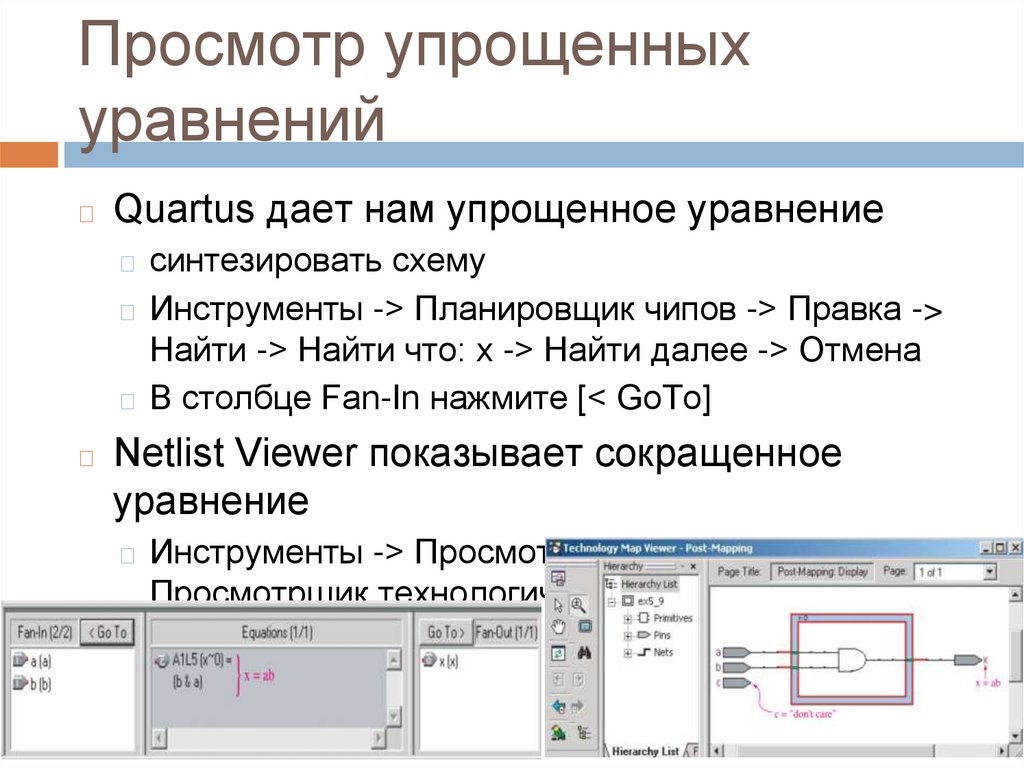

Просмотр упрощенныхуравнений

◻

Quartus дает нам упрощенное уравнение

◻ синтезировать схему

◻ Инструменты -> Планировщик чипов -> Правка ->

Найти -> Найти что: x -> Найти далее -> Отмена

◻ В столбце Fan-In нажмите [< GoTo]

◻

Netlist Viewer показывает сокращенное

уравнение

◻ Инструменты -> Просмотр списка соединений ->

Просмотрщик технологических карт - Посткартирование

45.

Вопросы и ответыЕсть вопросы?

Электроника

Электроника