Похожие презентации:

Л09. Синтез конвейерного процессора

1. Архитектуры процессорных систем

Лекция 9. Конвейерный процессор RISC-VЦикл из 16 лекций о цифровой схемотехнике, способах построения и архитектуре компьютеров

2. План лекции

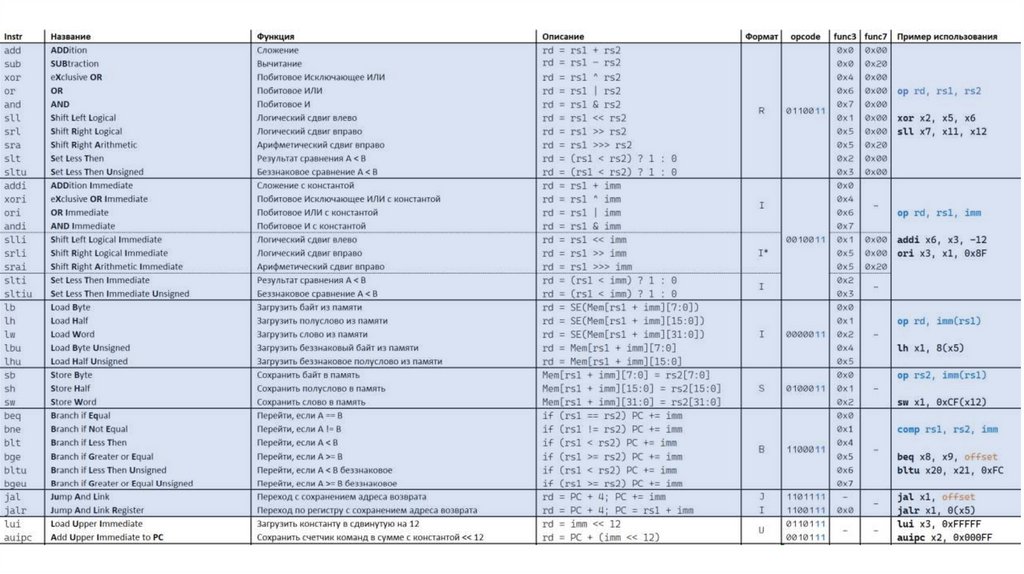

RISC-V

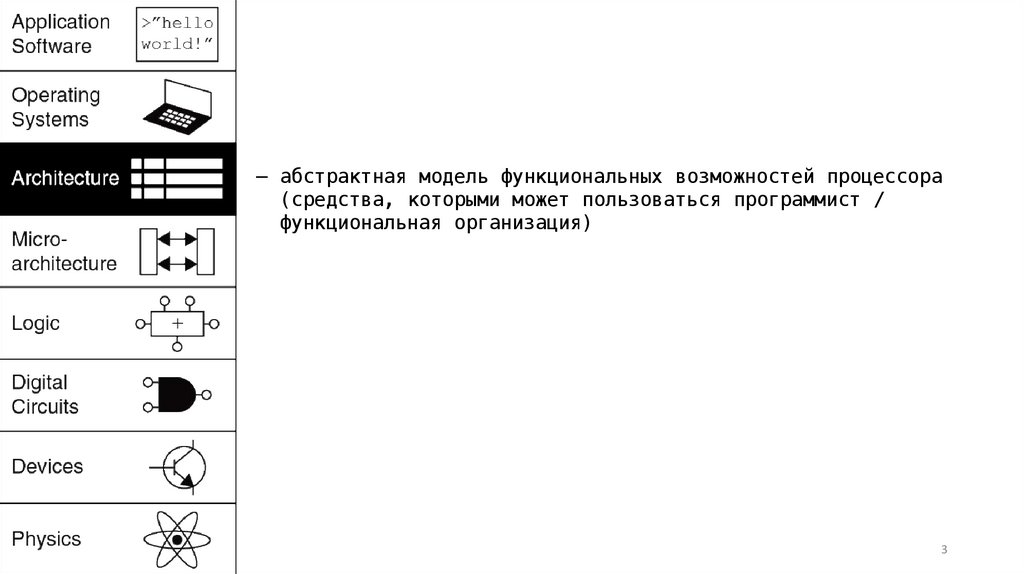

3. – абстрактная модель функциональных возможностей процессора (средства, которыми может пользоваться программист / функциональная

организация)3

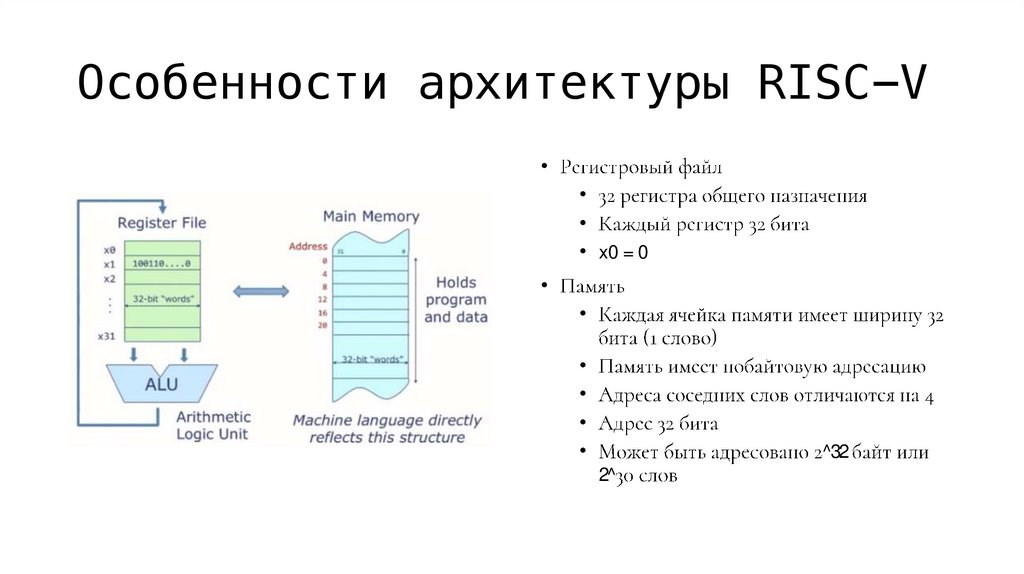

4. Особенности архитектуры RISC-V

• x0 = 0

2^

^32

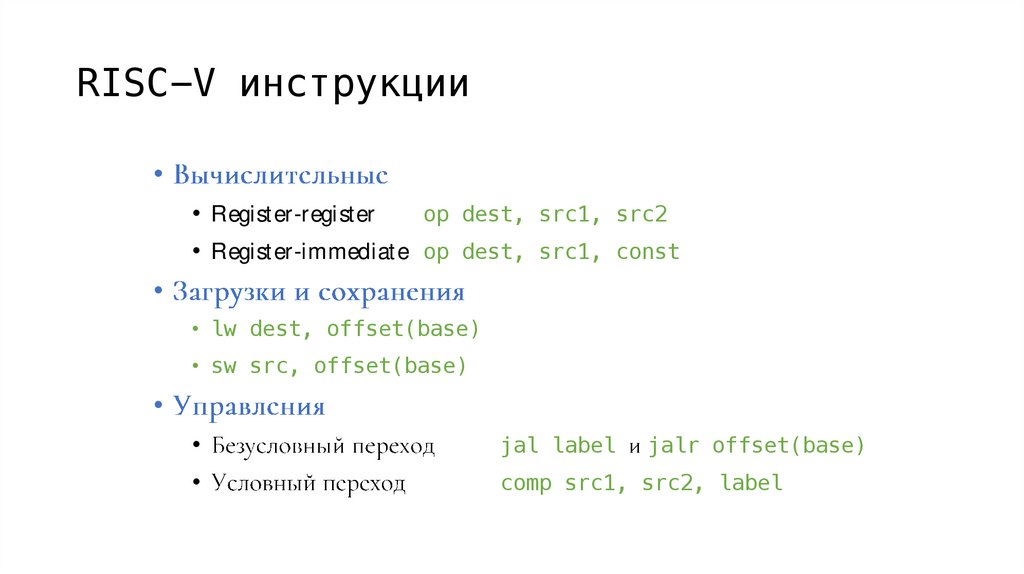

5. RISC-V инструкции

• Register-register

op dest, src1, src2

• Register-immediate op dest, src1, const

• lw dest, offset(base)

• sw src, offset(base)

jal label

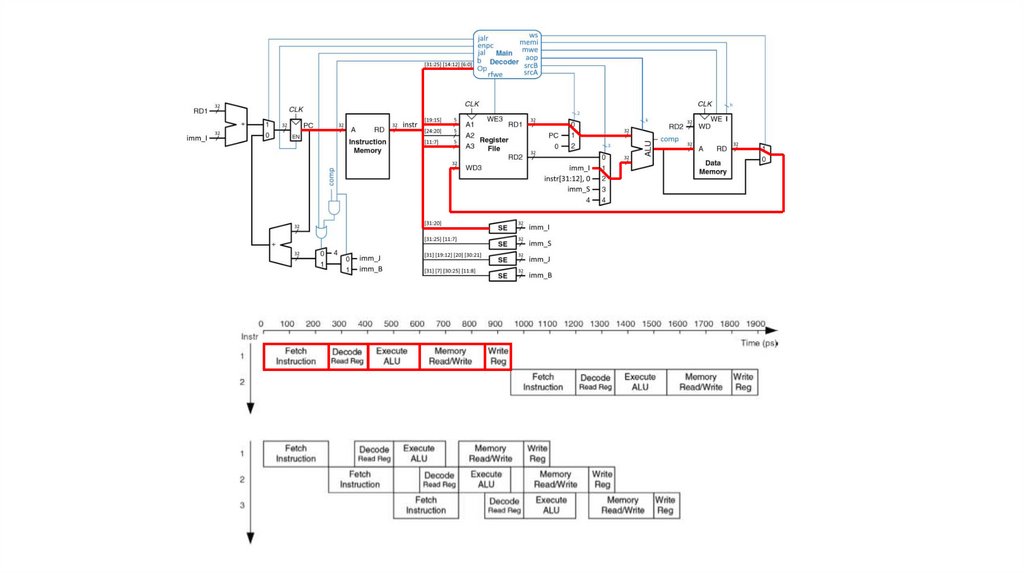

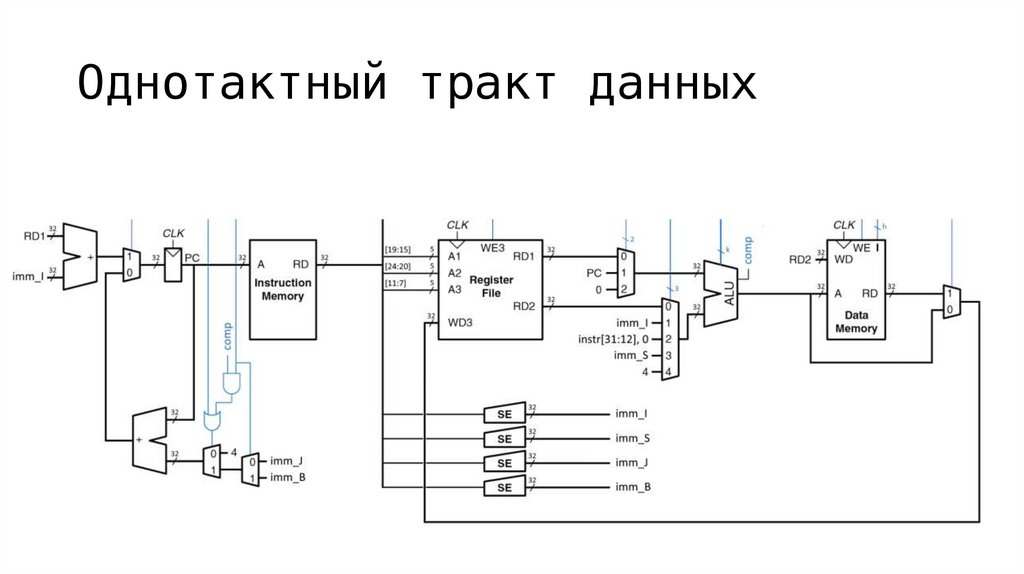

jalr offset(base)

comp src1, src2, label

6.

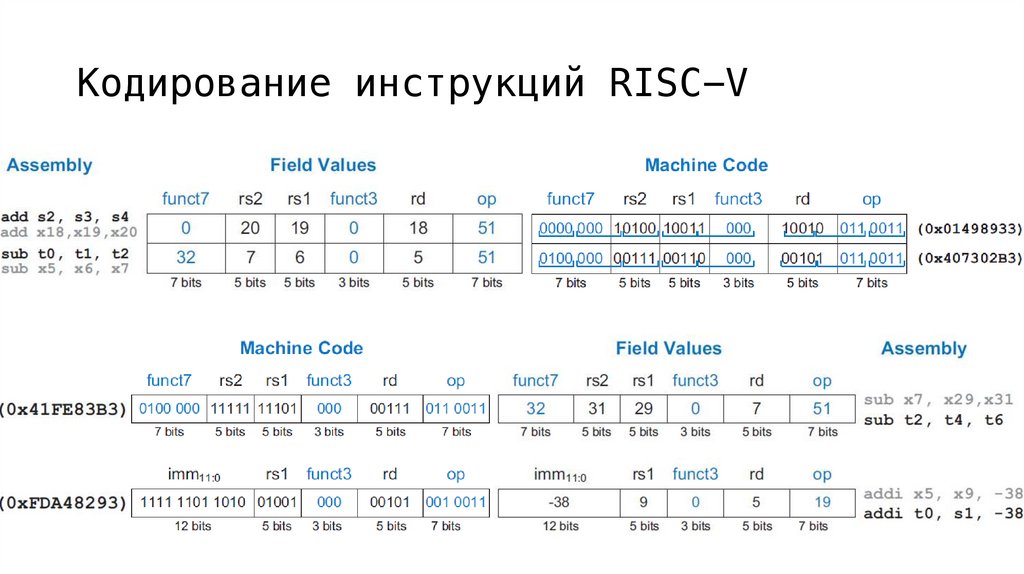

7. Кодирование инструкций RISC-V

8. Кодирование инструкций RISC-V

9. Представление программы в памяти

10. – физическая модель, которая устанавливает состав, порядок и принципы взаимодействия основных функциональных частей процессора

(структурная организация)10

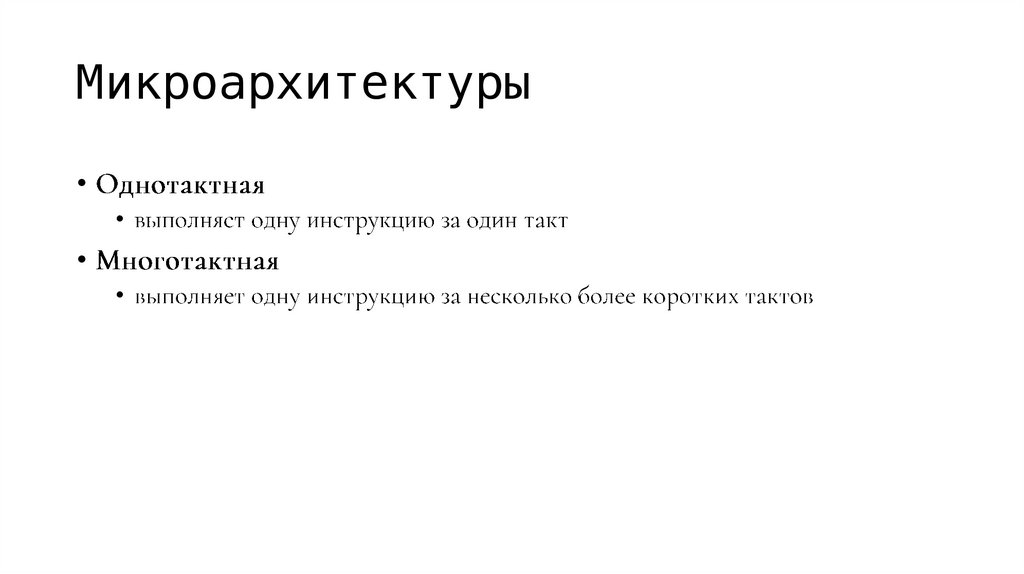

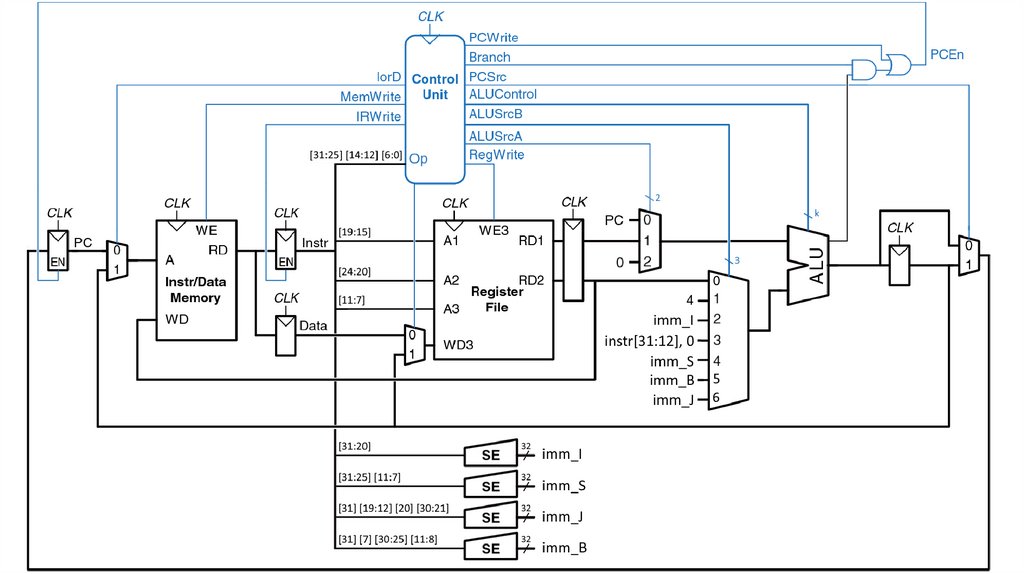

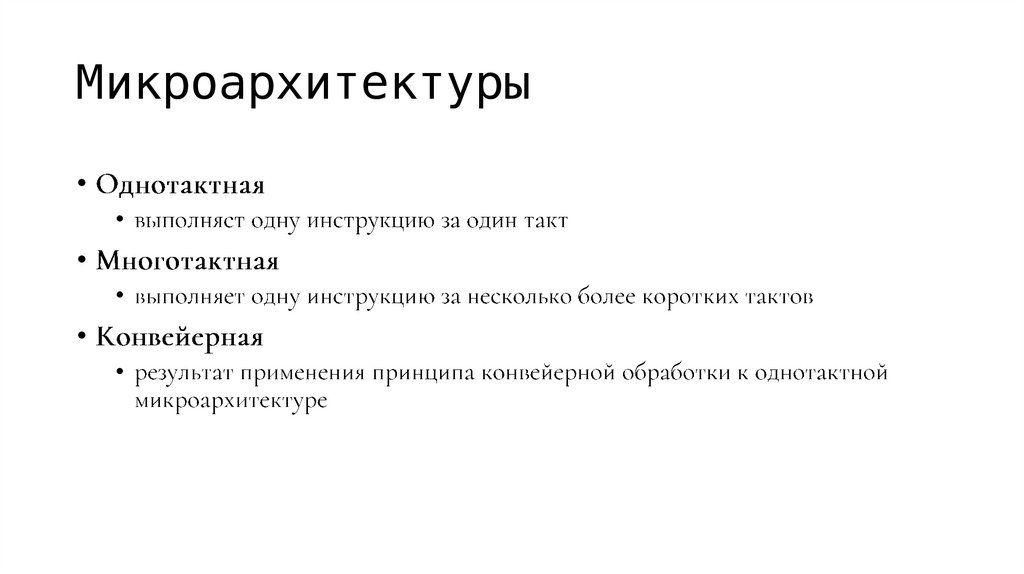

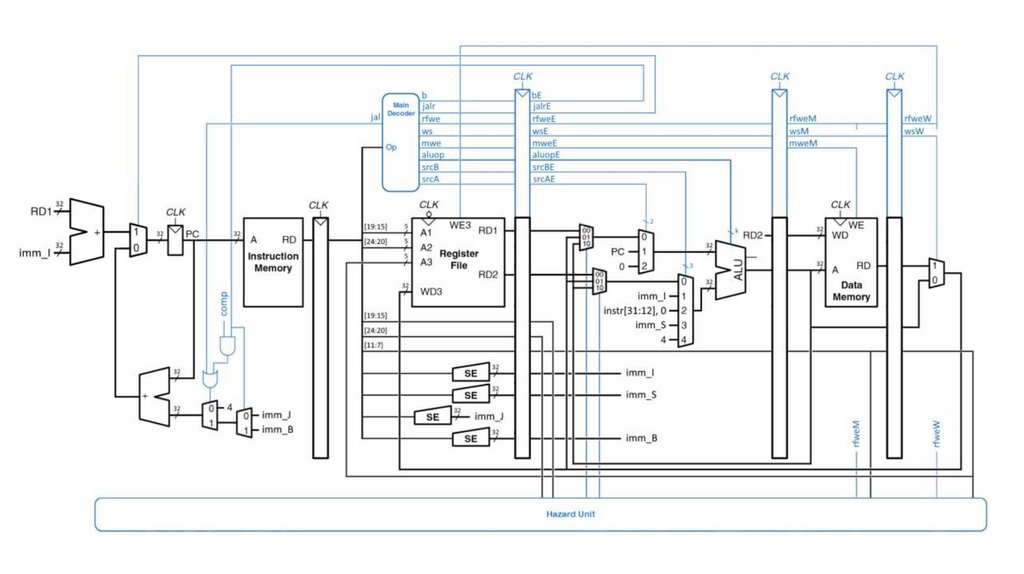

11. Микроархитектуры

12.

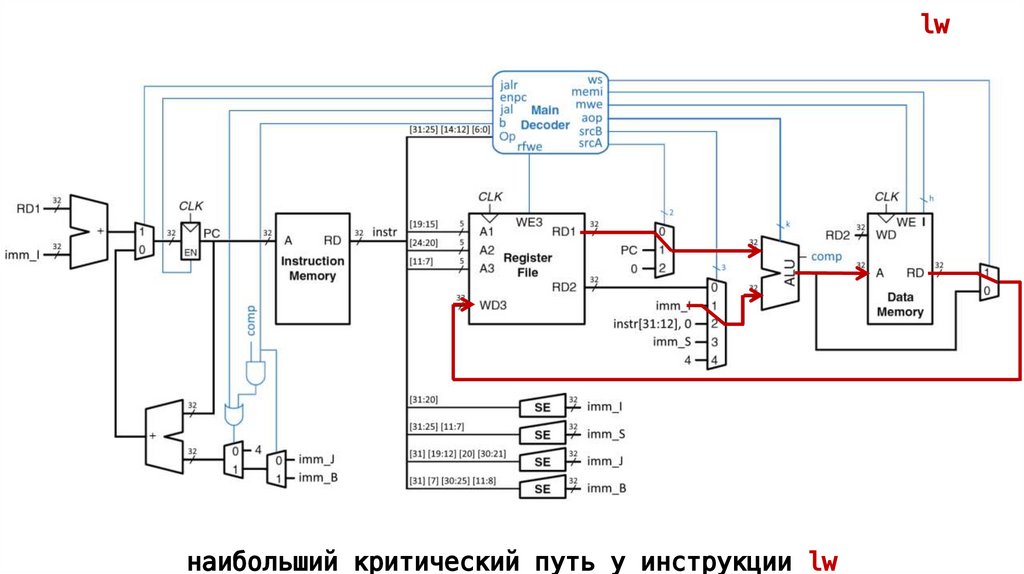

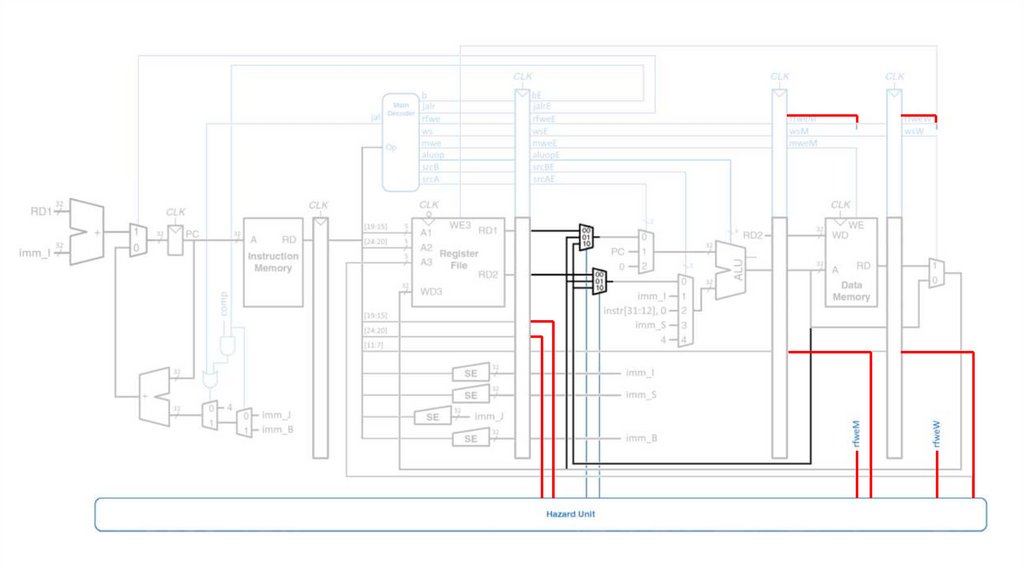

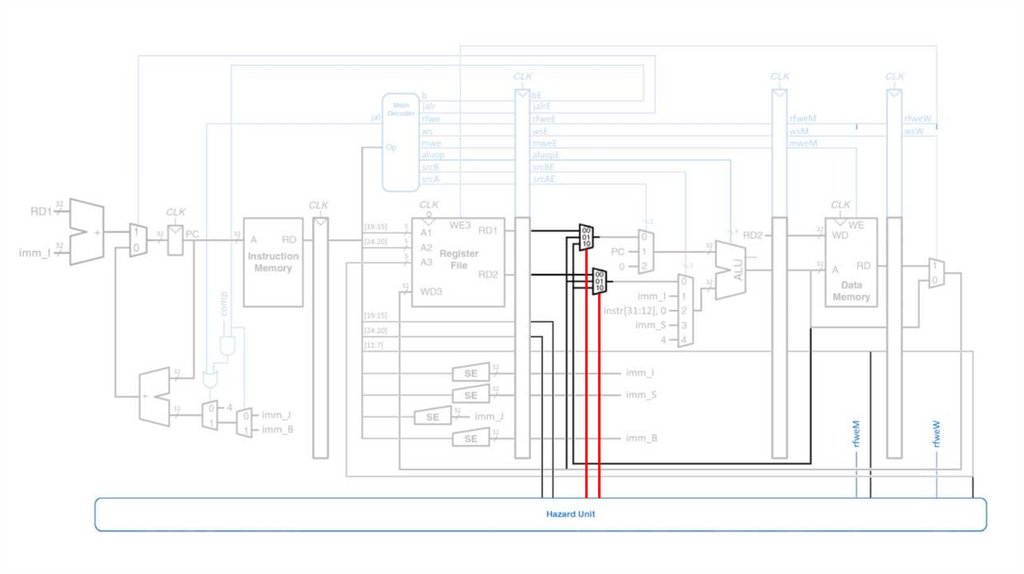

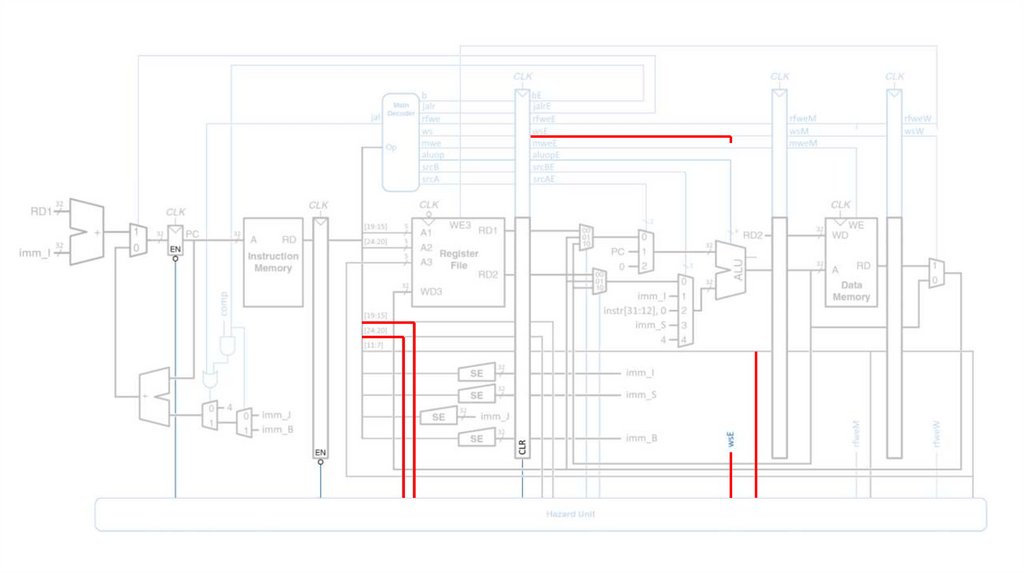

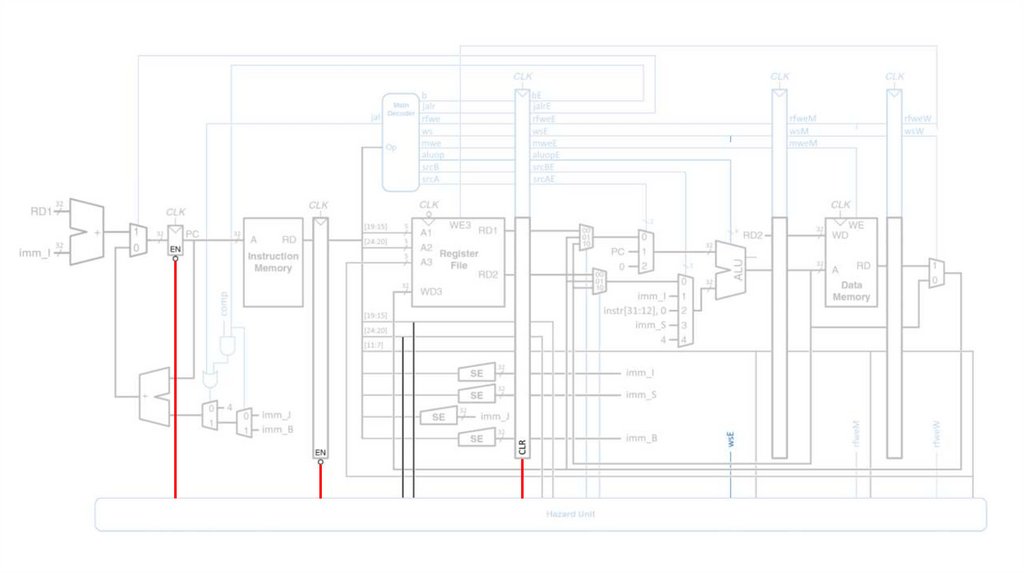

lwнаибольший критический путь у инструкции lw

13.

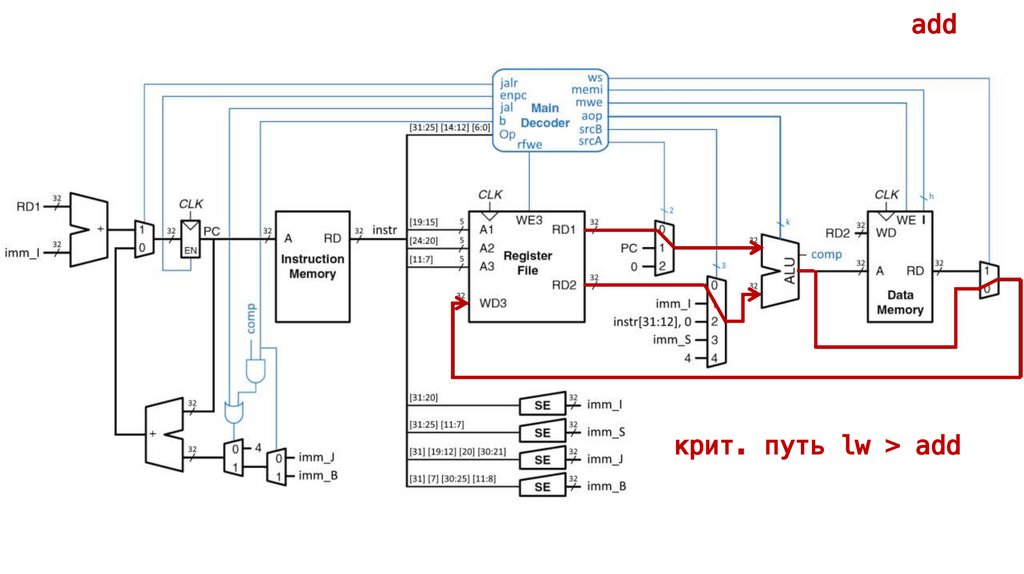

addкрит. путь lw > add

14. Микроархитектуры

15.

16. Микроархитектуры

17.

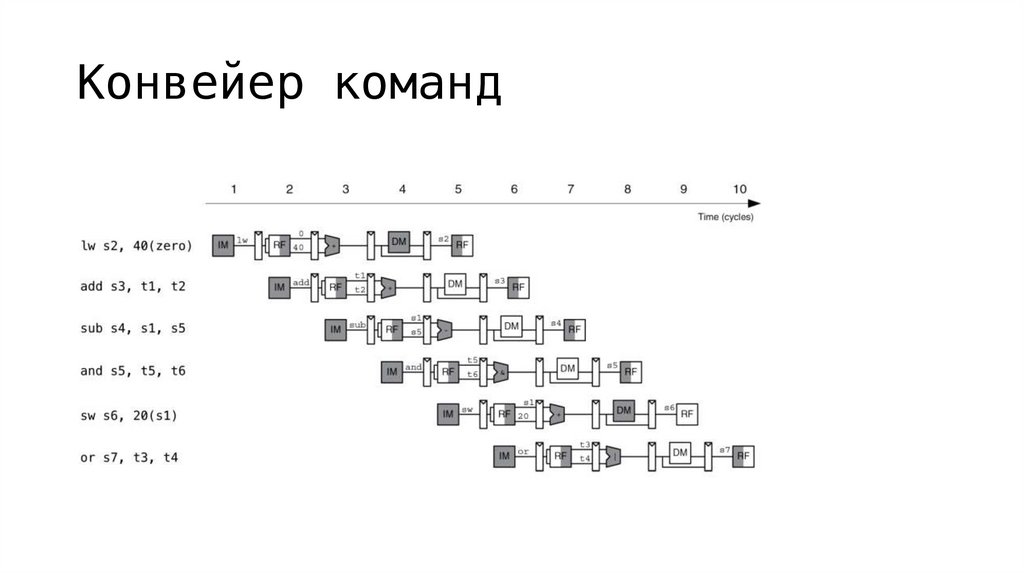

18. Конвейер команд

19. Однотактный тракт данных

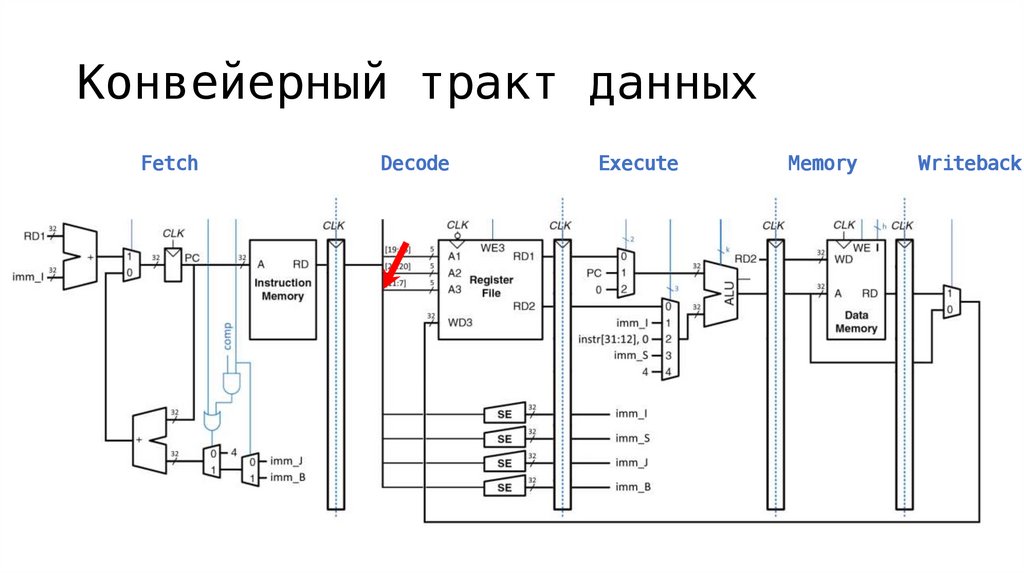

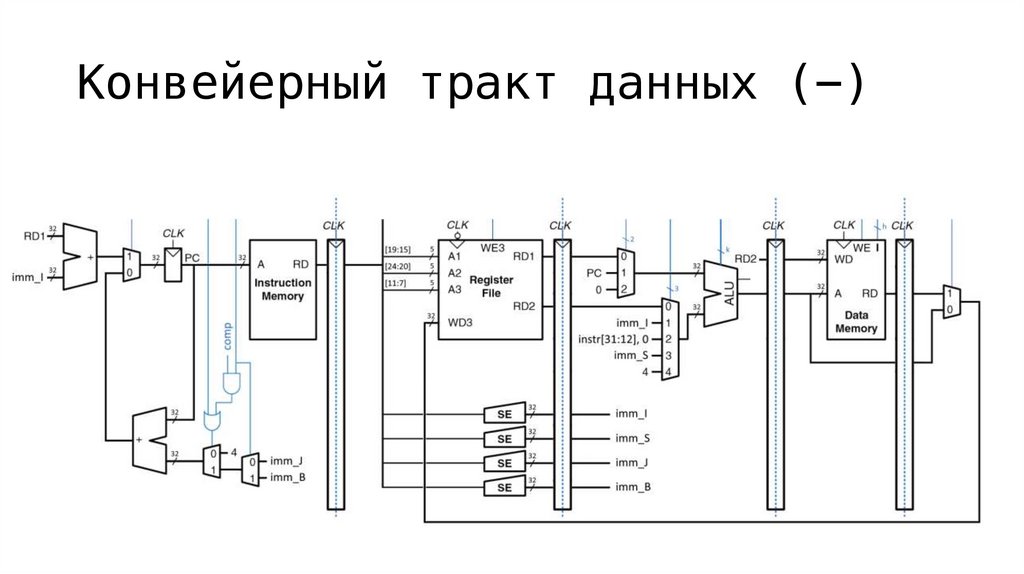

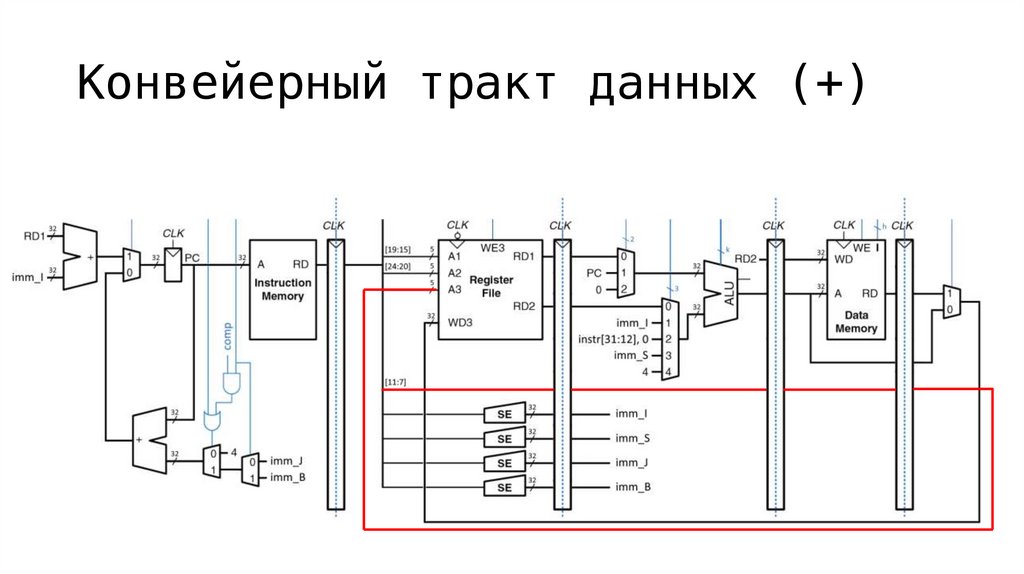

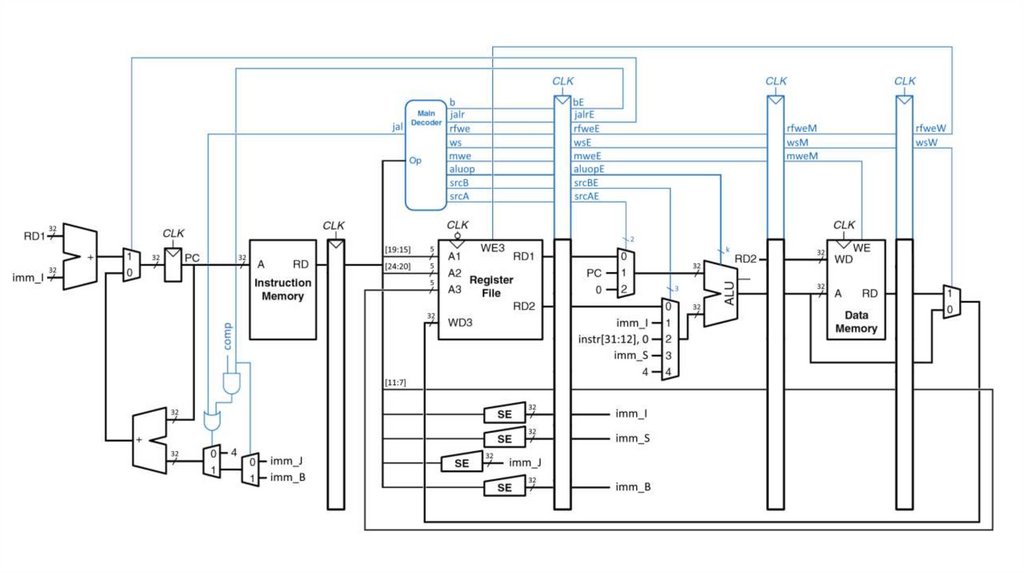

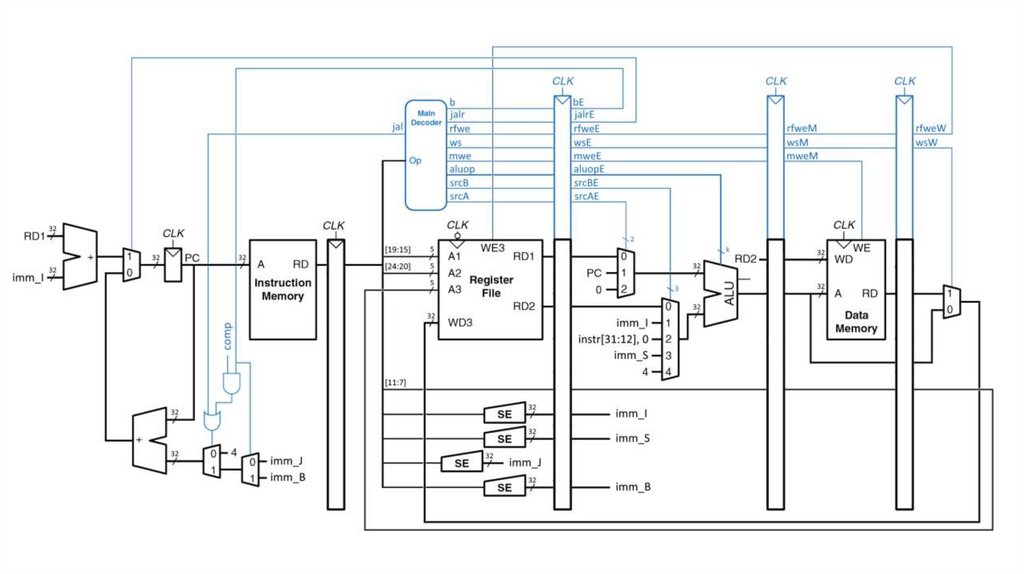

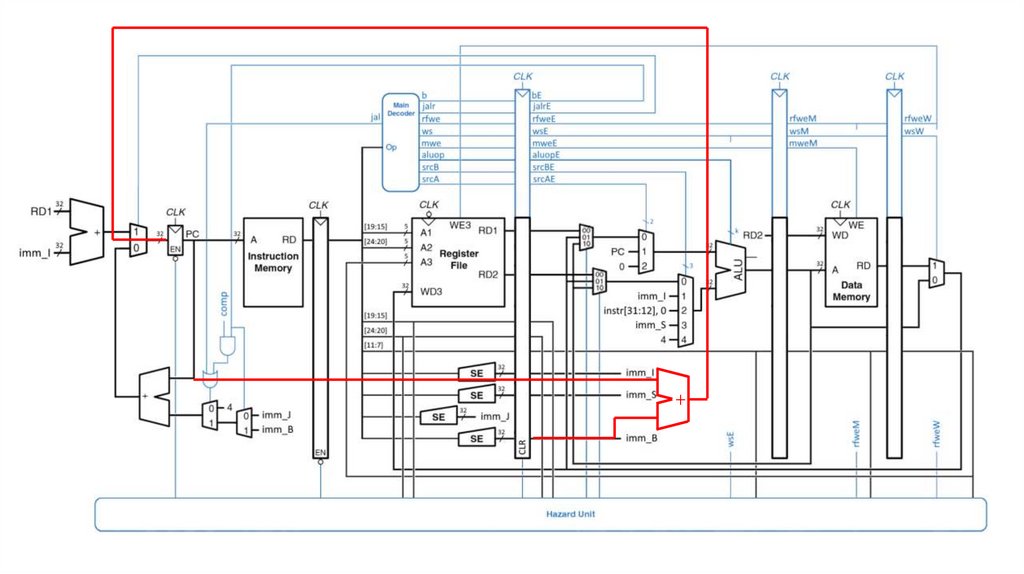

20. Конвейерный тракт данных

FetchDecode

Execute

Memory

Writeback

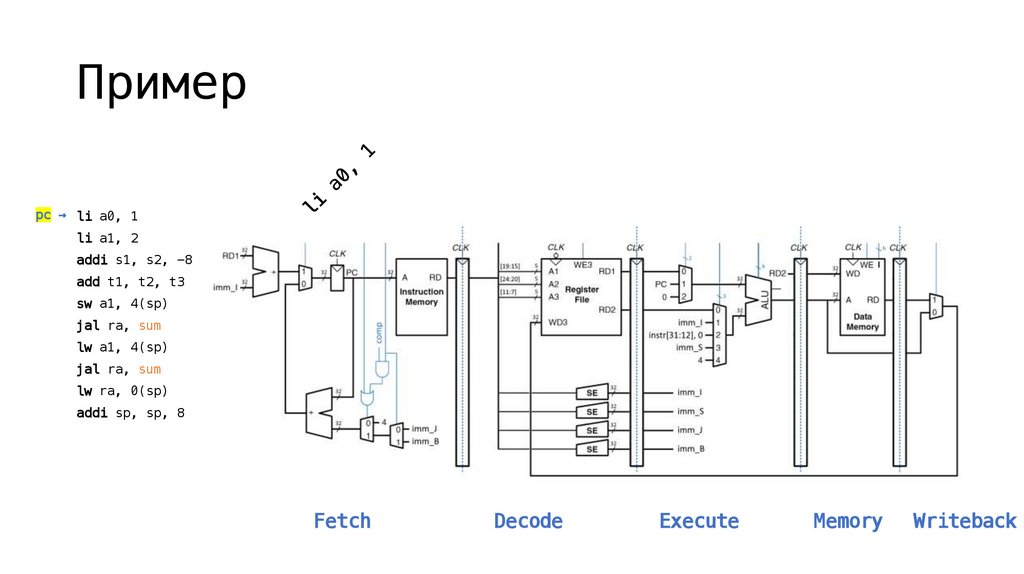

21. Пример

pc → li a0, 1li a1, 2

addi s1, s2, -8

add t1, t2, t3

sw a1, 4(sp)

jal ra, sum

lw a1, 4(sp)

jal ra, sum

lw ra, 0(sp)

addi sp, sp, 8

Fetch

Decode

Execute

Memory

Writeback

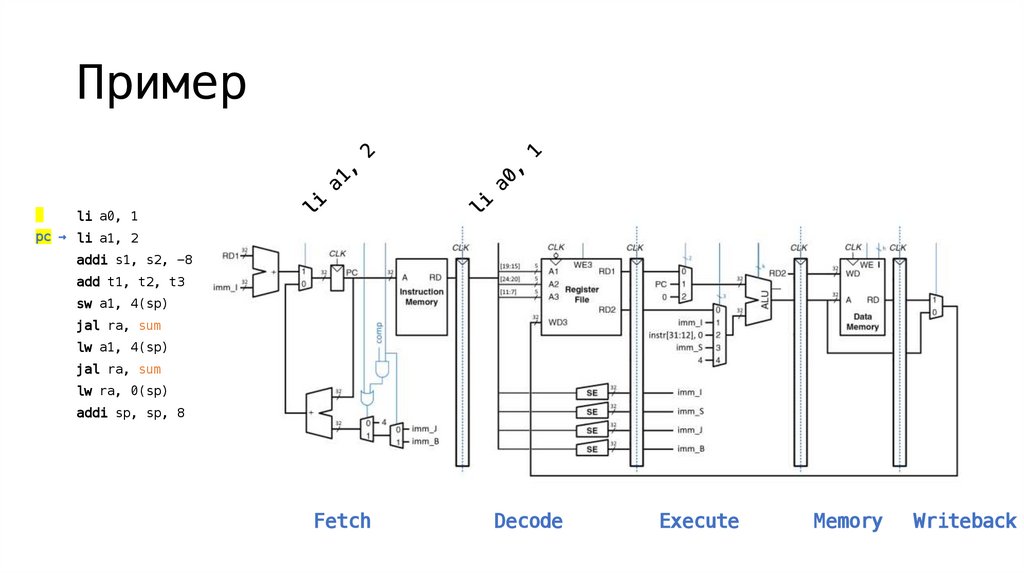

22. Пример

li a0, 1pc → li a1, 2

addi s1, s2, -8

add t1, t2, t3

sw a1, 4(sp)

jal ra, sum

lw a1, 4(sp)

jal ra, sum

lw ra, 0(sp)

addi sp, sp, 8

Fetch

Decode

Execute

Memory

Writeback

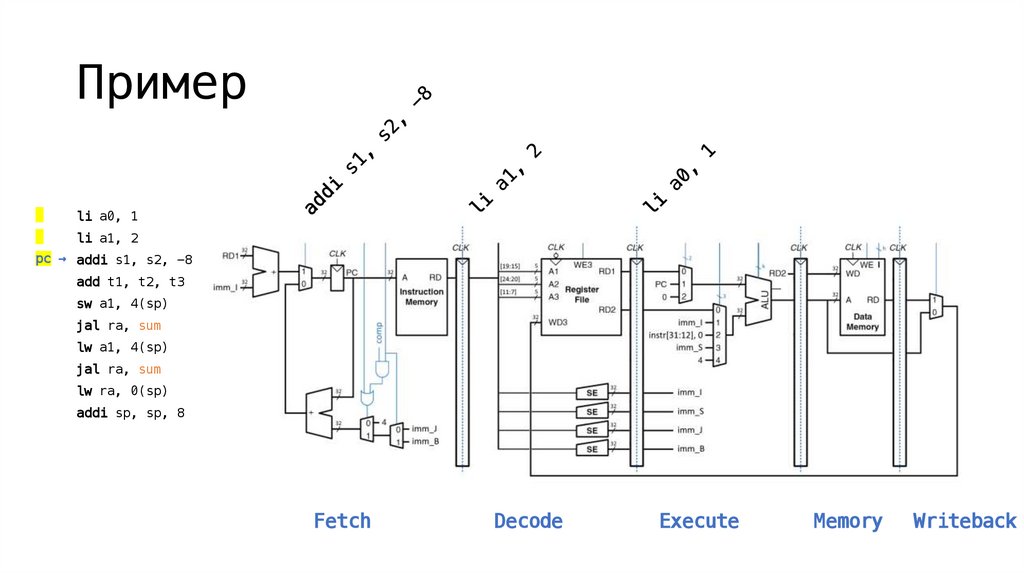

23. Пример

li a0, 1li a1, 2

pc → addi s1, s2, -8

add t1, t2, t3

sw a1, 4(sp)

jal ra, sum

lw a1, 4(sp)

jal ra, sum

lw ra, 0(sp)

addi sp, sp, 8

Fetch

Decode

Execute

Memory

Writeback

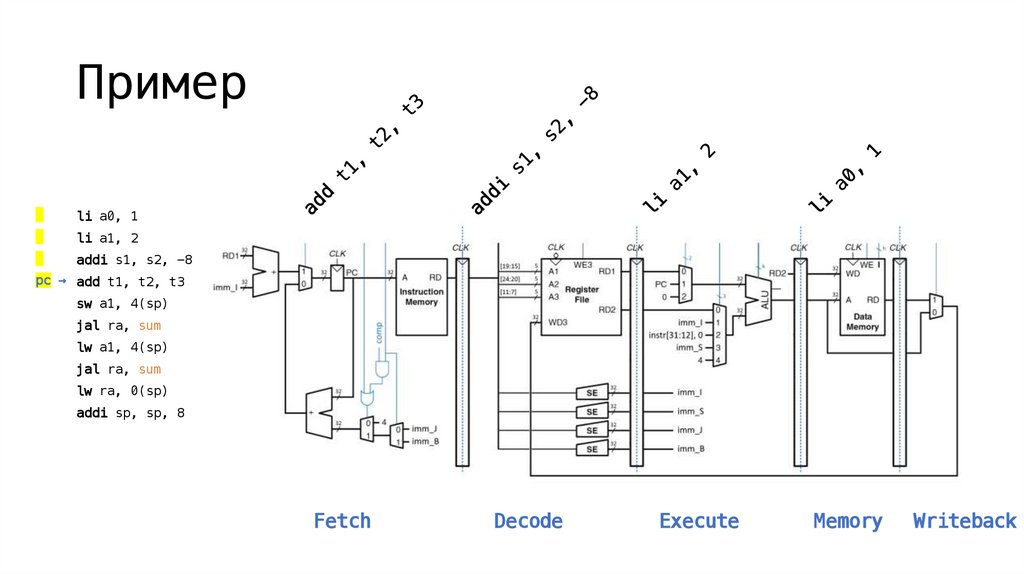

24. Пример

li a0, 1li a1, 2

addi s1, s2, -8

pc → add t1, t2, t3

sw a1, 4(sp)

jal ra, sum

lw a1, 4(sp)

jal ra, sum

lw ra, 0(sp)

addi sp, sp, 8

Fetch

Decode

Execute

Memory

Writeback

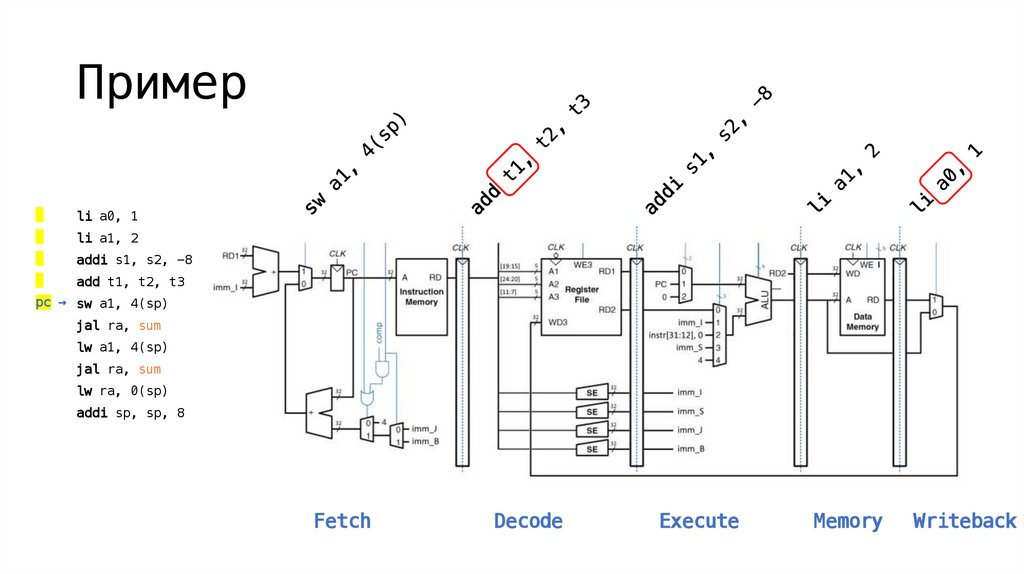

25. Пример

li a0, 1li a1, 2

addi s1, s2, -8

add t1, t2, t3

pc → sw a1, 4(sp)

jal ra, sum

lw a1, 4(sp)

jal ra, sum

lw ra, 0(sp)

addi sp, sp, 8

Fetch

Decode

Execute

Memory

Writeback

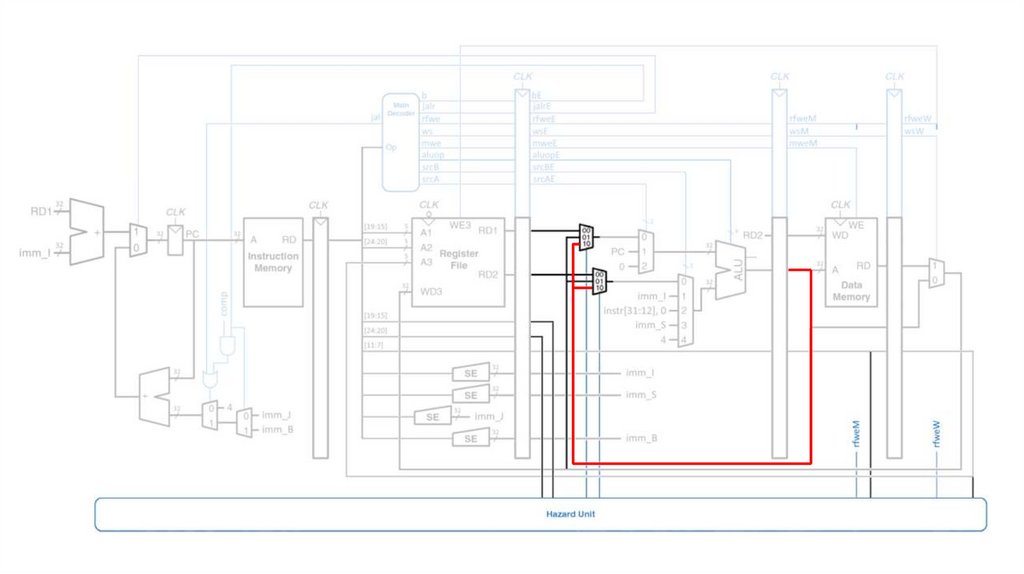

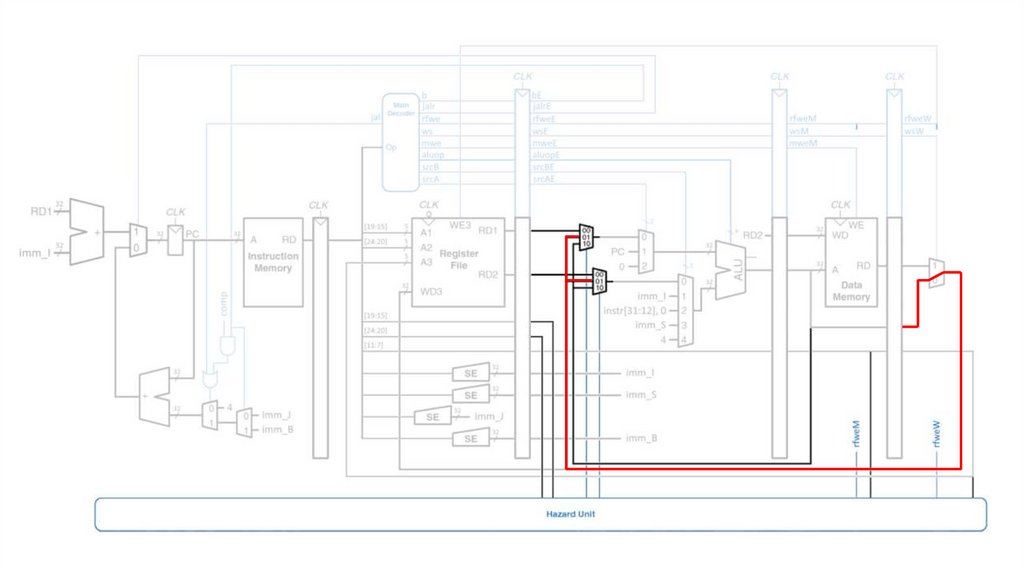

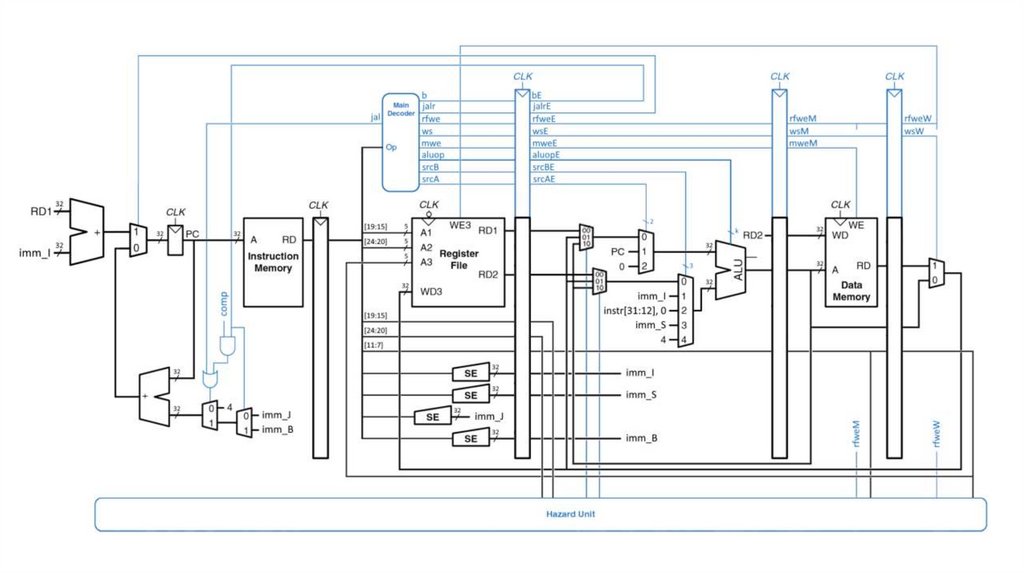

26. Конвейерный тракт данных (-)

27. Конвейерный тракт данных (+)

28.

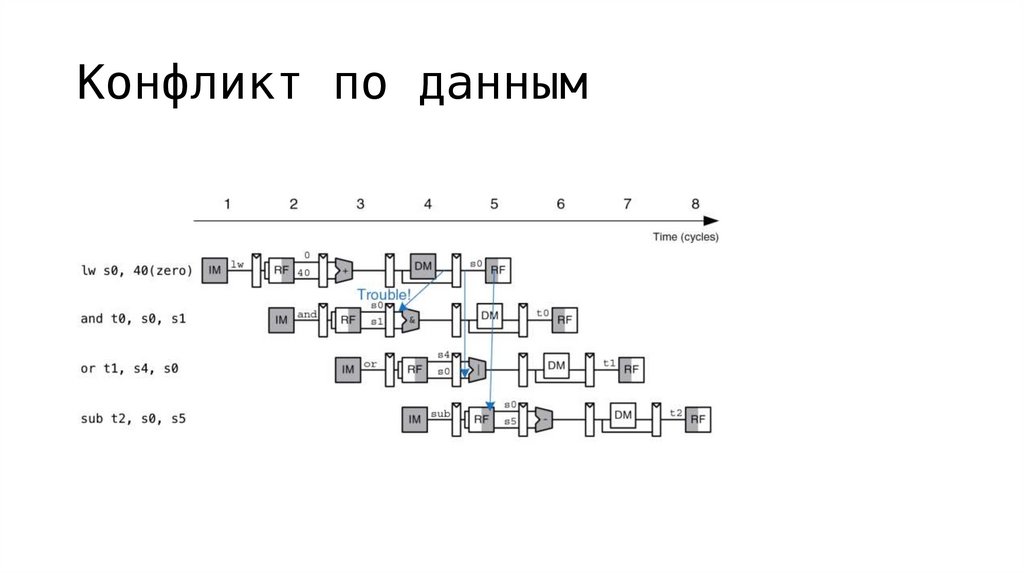

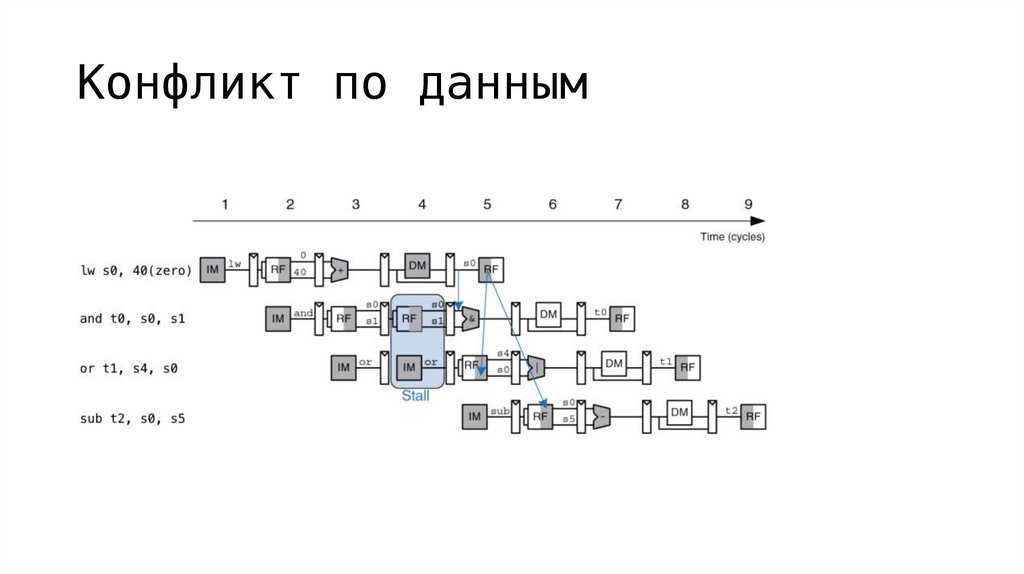

29. Конфликт по данным

30. Конфликт по данным

31.

32.

33.

34.

35.

36.

37. Конфликт по данным

38. Конфликт по данным

39.

40.

41.

42.

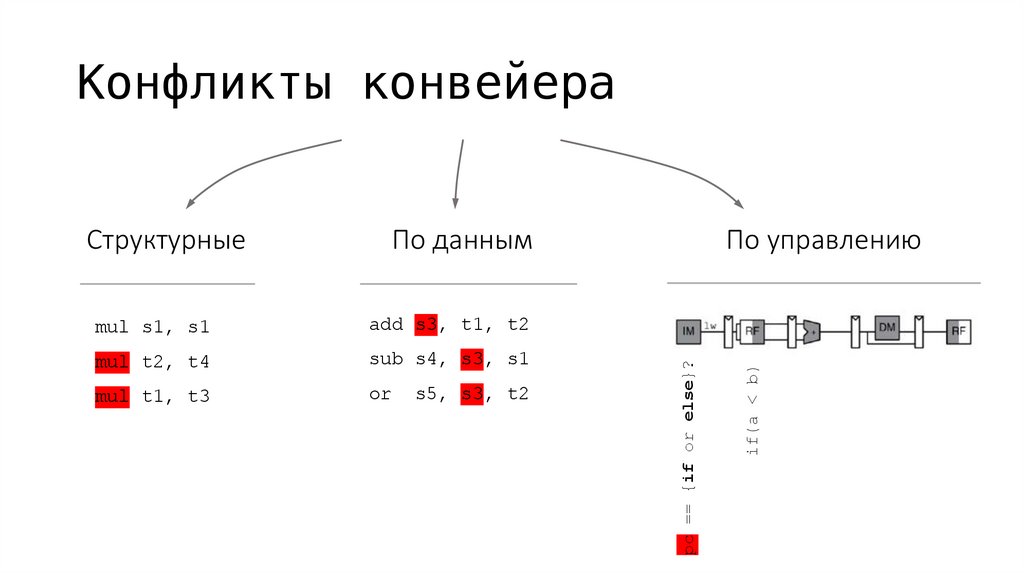

+43. Конфликты конвейера

mul s1, s1add s3, t1, t2

mul t2, t4

sub s4, s3, s1

mul t1, t3

or

s5, s3, t2

По управлению

if(a < b)

По данным

pc == {if or else}?

Структурные

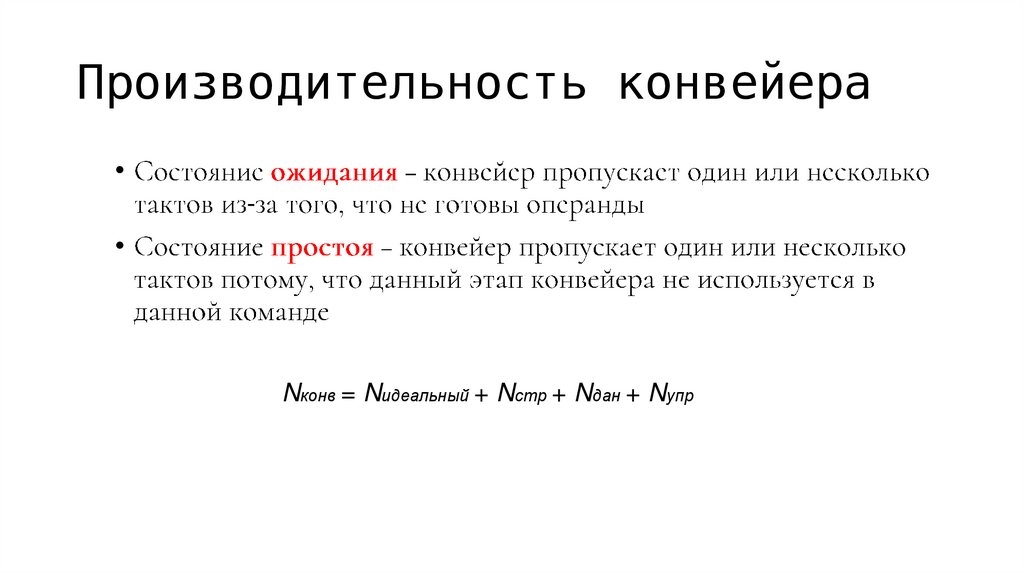

44. Производительность конвейера

-

Nконв = Nидеальный + Nстр + Nдан + Nупр

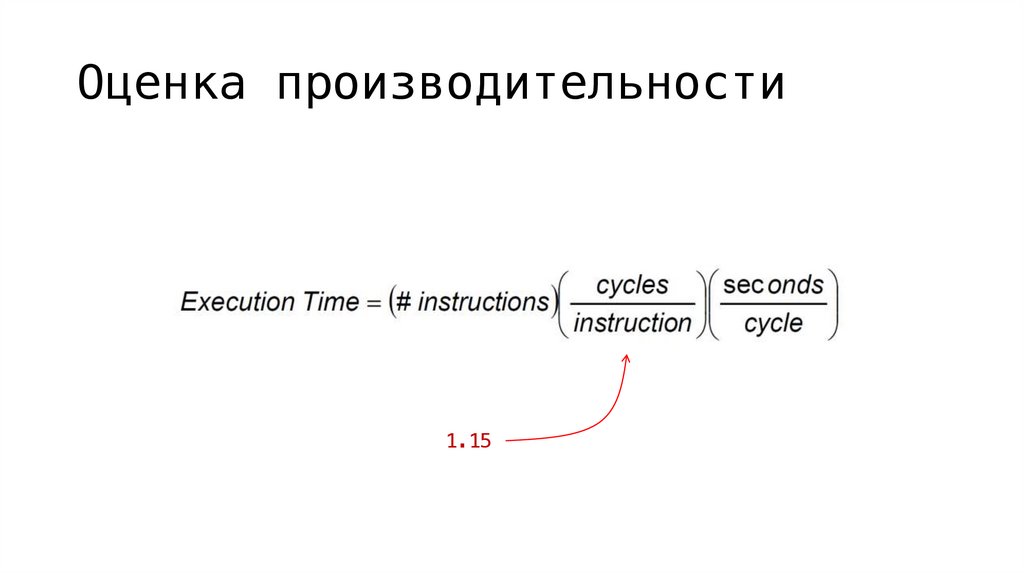

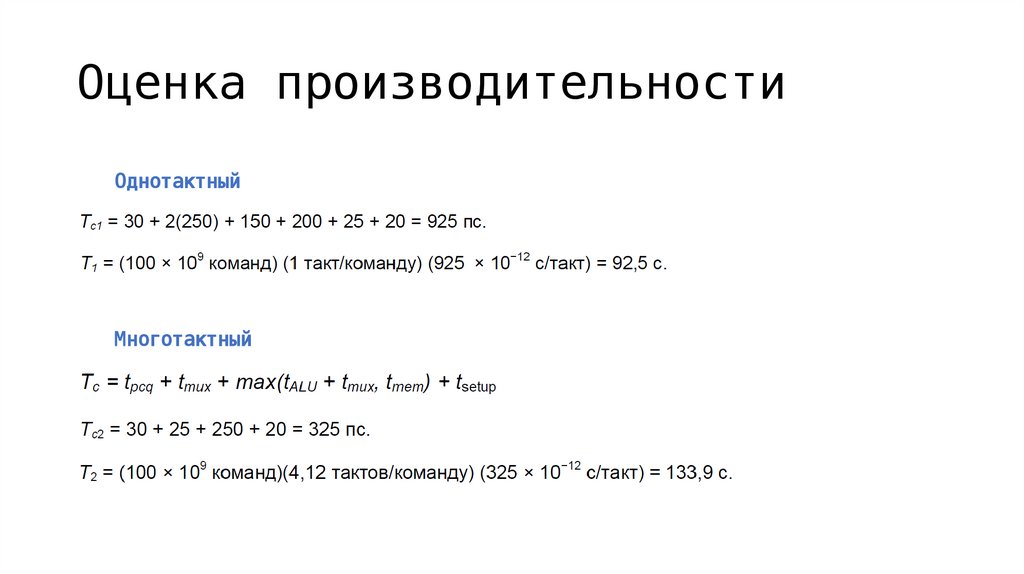

45. Оценка производительности

1.1546. Оценка производительности

ОднотактныйМноготактный

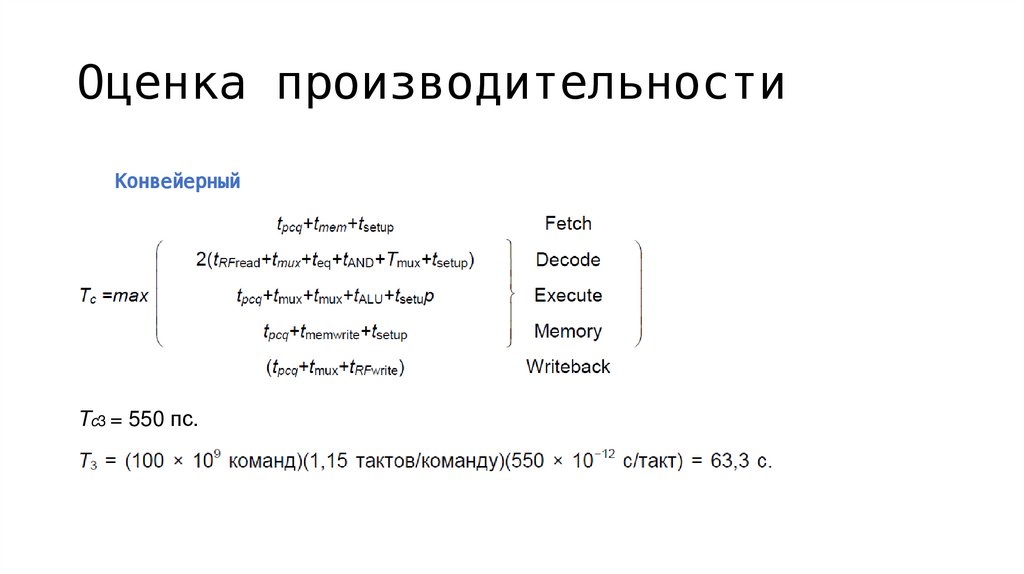

47. Оценка производительности

КонвейерныйTc3 = 550 пс.

Программирование

Программирование