Похожие презентации:

3. Л2(1)

1.

ЦИФРОВАЯОБРАБОТКА

СИГНАЛОВ

2.

Тема № 1.ПРЕДСТАВЛЕНИЕ

ДИСКРЕТНЫХ СИГНАЛОВ

Занятие № 2. Лекция № 2.

Обработка сигналов в ЦОС

Кафедра «Электроника

и теория связи»

3.

Взаимосвязи дисциплины «Цифровая обработка сигналов»Дисциплины модуля телекоммуникаций

Сети и комплексы

радиорелейной

и спутниковой

связи

Сети и системы

передачи информации

Системы

и комплексы радиосвязи

Основы построения

пользовательского

(оконечного) оборудования

Системы

и комплексы специальной

связи

Теория

электросвязи

Цифровая обработка сигналов

Высшая математика

Дискретная

математика

Основы

теории цепей

Информатика

Электроника

и схемотехника

3

4.

Цели занятия1. Изучение основных операций ЦОС.

2. Ознакомление со средствами реализации

систем цифровой обработки сигналов.

3. Изучение принципов построения

и архитектуры цифровых устройств

обработки сигналов

4

5.

Учебные вопросы1. Основные операции ЦОС.

2. Средства реализации систем ЦОС.

3. Архитектура аппаратных средств ЦОС.

5

6.

Литература1. Солонина А. И., Улахович Д. А., Арбузов С. М., Соловьева Е. Б. и др. Основы цифровой

обработки сигналов: Курс лекций. – СПб.: БХВ-Петербург, 2003, 2005.

6

7.

2. Афанасьев А. А., Рыболовлев А. А.,Рыжков А. П. Цифровая обработка

сигналов. – Орел: Академия ФСО, 2016.

3. Афанасьев А. А., Рыболовлев А. А.,

Рыжков А. П. Цифровая обработка

сигналов. Учебное пособие для вузов. –

М.: Горячая линия - Телеком, 2017, 2021.

7

8.

1.Основные операции ЦОС

9.

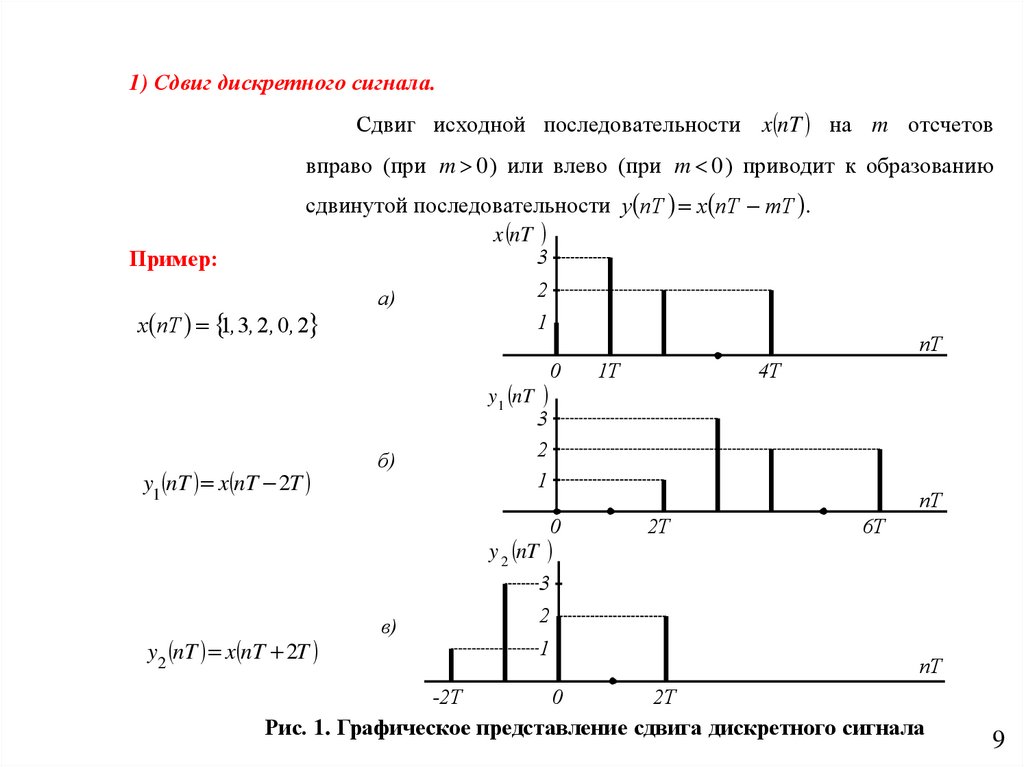

1) Сдвиг дискретного сигнала.i.

Сдвиг исходной последовательности x nT на m отсчетов

вправо (при m 0 ) или влево (при m 0 ) приводит к образованию

сдвинутой последовательности y nT x nT mT .

x nT

3

Пример:

2

а)

1

x nT 1, 3, 2, 0, 2

y 1 nT

y1 nT x nT 2T

0

4Т

1Т

3

2

1

б)

nT

0

y 2 nT

3

y2 nT x nT 2T

nT

2Т

2

1

в)

-2Т

6Т

nT

0

2Т

Рис. 1. Графическое представление сдвига дискретного сигнала

9

10.

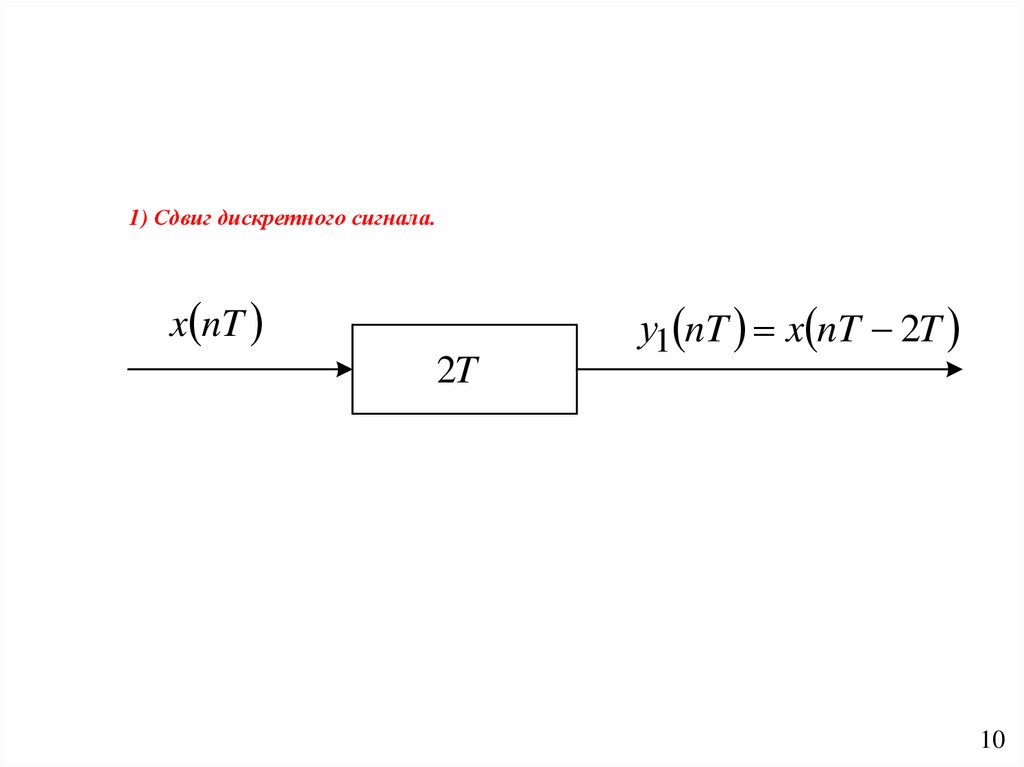

1) Сдвиг дискретного сигнала.x nT

2T

у1 nT x nT 2T

10

11.

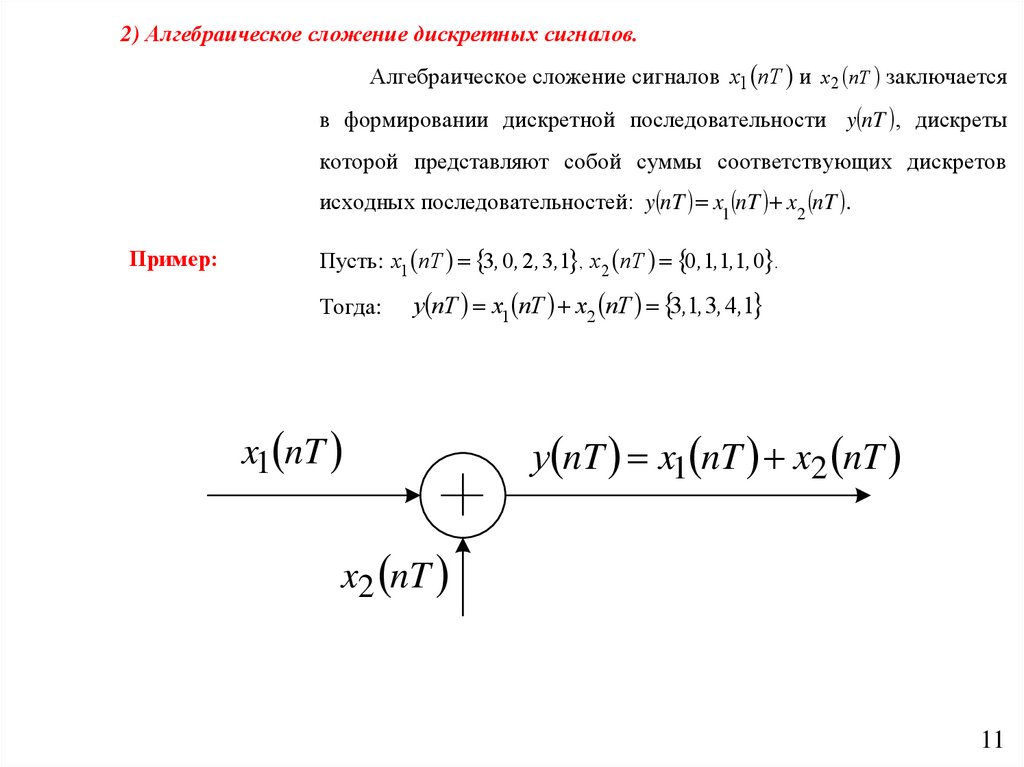

2) Алгебраическое сложение дискретных сигналов.Алгебраическое сложение сигналов x1 nT и x 2 nT заключается

в формировании дискретной последовательности y nT , дискреты

которой представляют собой суммы соответствующих дискретов

исходных последовательностей: y nT x1 nT x2 nT .

Пример:

Пусть: x1 nT 3, 0 , 2 , 3,1 , x 2 nT 0 ,1,1,1, 0 .

Тогда:

y nT x1 nT x2 nT 3,1, 3, 4,1

x1 nT

у nT x1 nT x2 nT

x2 nT

11

12.

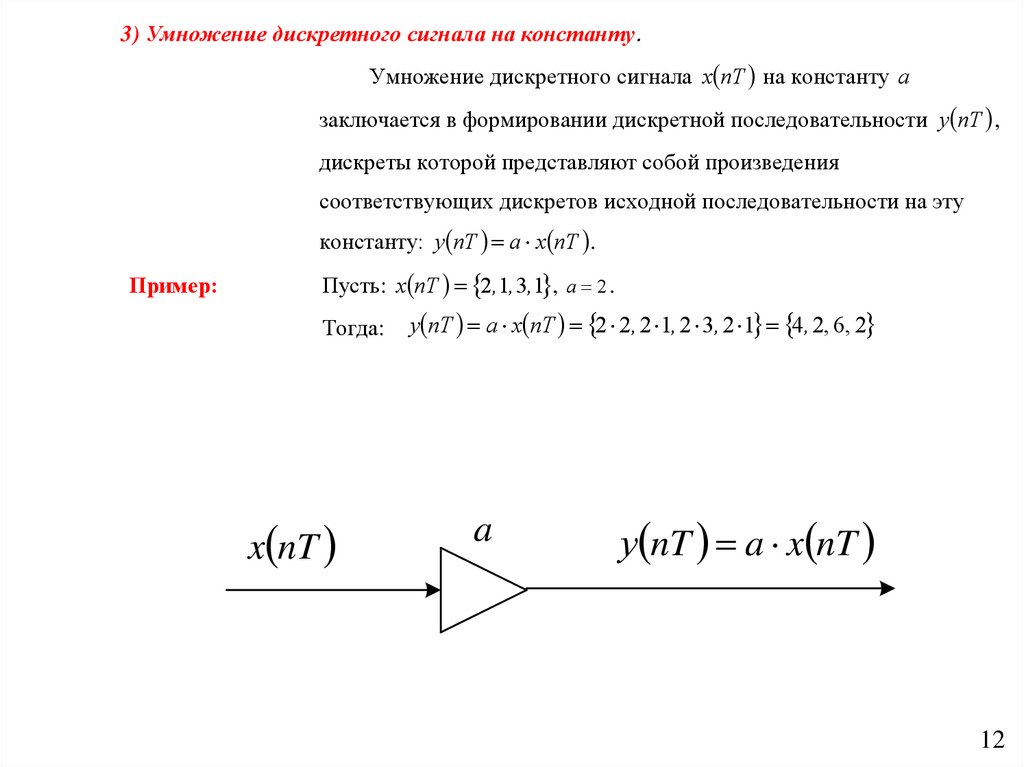

3) Умножение дискретного сигнала на константу.Умножение дискретного сигнала x nT на константу a

i.

заключается в формировании дискретной последовательности y nT ,

дискреты которой представляют собой произведения

соответствующих дискретов исходной последовательности на эту

константу: y nT a x nT .

Пример:

Пусть: x nT 2,1, 3,1 , a 2 .

Тогда:

x nT

y nT a x nT 2 2, 2 1, 2 3, 2 1 4, 2, 6, 2

a

у nT a x nT

12

13.

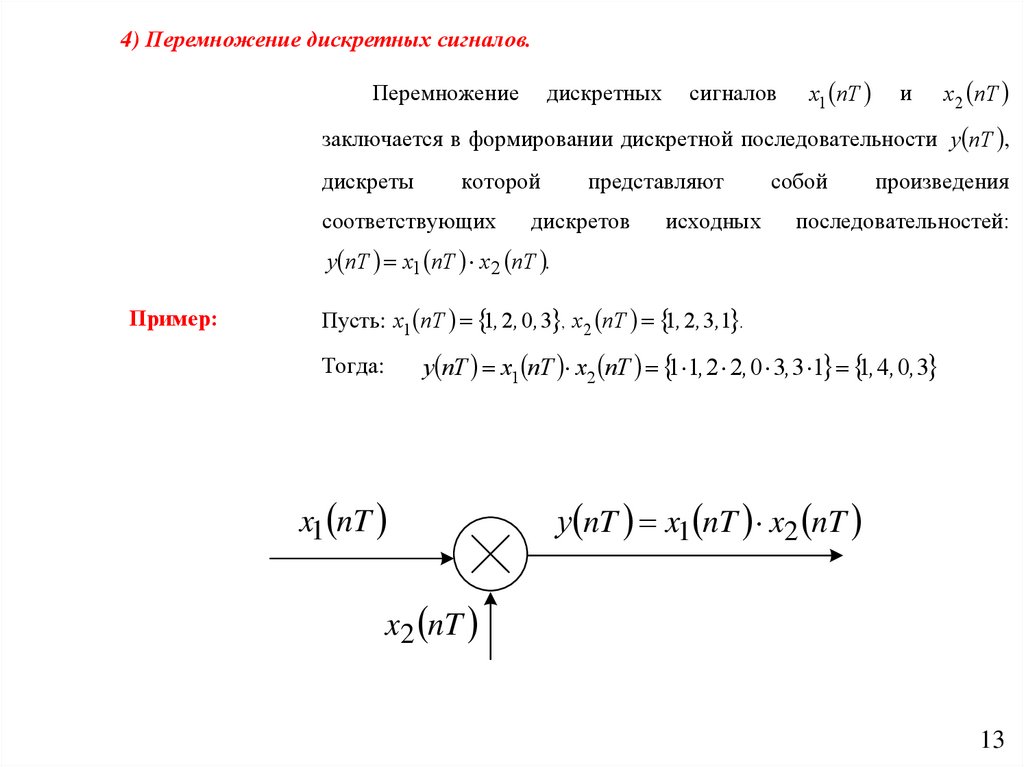

4) Перемножение дискретных сигналов.i.

Перемножение

дискретных

сигналов

x1 nT

и

x 2 nT

заключается в формировании дискретной последовательности y nT ,

дискреты

которой

соответствующих

представляют

дискретов

исходных

собой

произведения

последовательностей:

y nT x1 nT x 2 nT .

Пример:

i.

Пусть: x1 nT 1, 2, 0, 3 , x 2 nT 1, 2 , 3,1 .

ii.

Тогда:

y nT x1 nT x2 nT 1 1, 2 2, 0 3, 3 1 1, 4, 0, 3

x1 nT

у nT x1 nT x2 nT

x2 nT

13

14.

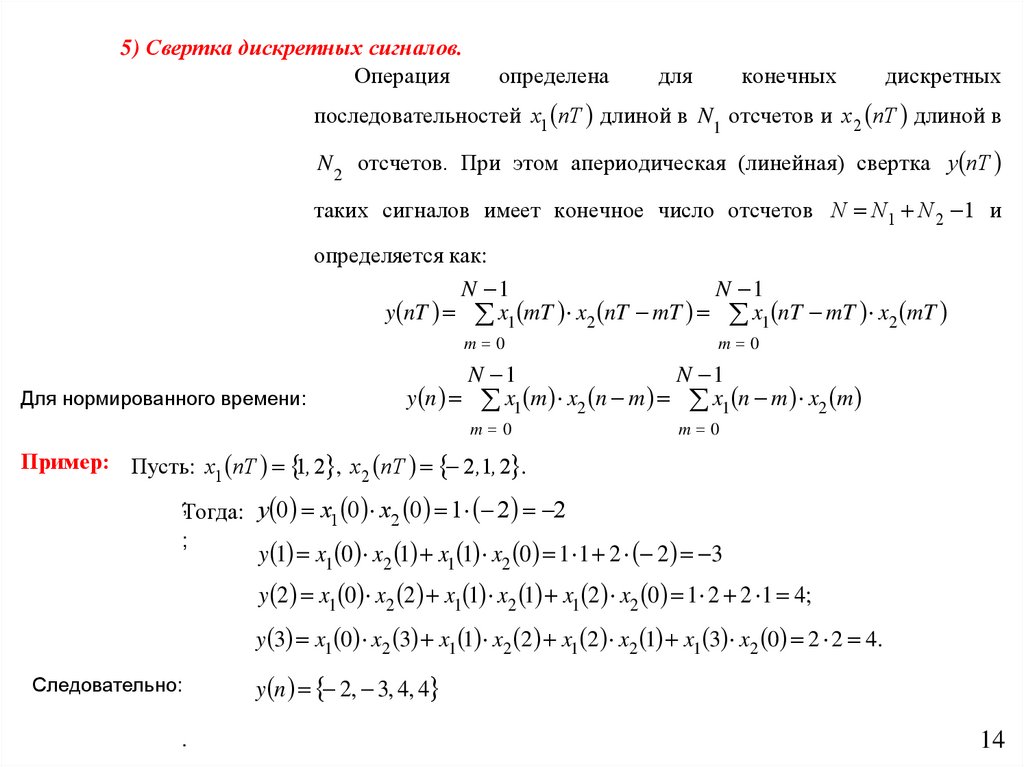

5) Свертка дискретных сигналов.Операция

определена

для

конечных

дискретных

последовательностей x1 nT длиной в N1 отсчетов и x 2 nT длиной в

N 2 отсчетов. При этом апериодическая (линейная) свертка y nT

таких сигналов имеет конечное число отсчетов N N1 N 2 1 и

определяется как:

N 1

N 1

y nT x1 mT x2 nT mT x1 nT mT x2 mT

m 0

Для нормированного времени:

m 0

N 1

N 1

y n x1 m x2 n m x1 n m x2 m

m 0

m 0

Пример: Пусть: x nT 1, 2 , x nT 2 ,1, 2 .

1

2

i.

;

y 0 x1 0 x2 0 1 2 2

Тогда:

;

y 1 x1 0 x2 1 x1 1 x2 0 1 1 2 2 3

y 2 x1 0 x2 2 x1 1 x2 1 x1 2 x2 0 1 2 2 1 4;

y 3 x1 0 x2 3 x1 1 x2 2 x1 2 x2 1 x1 3 x2 0 2 2 4.

Следовательно:

.

y n 2, 3, 4, 4

14

15.

Выводы по первому вопросу:1. Изучили основные операции ЦОС. Зачем?

Данные операции являются базовыми принципами обработки

дискретных (цифровых) сигналов во всей вычислительной технике

15

16.

2.Средства реализации систем ЦОС

17.

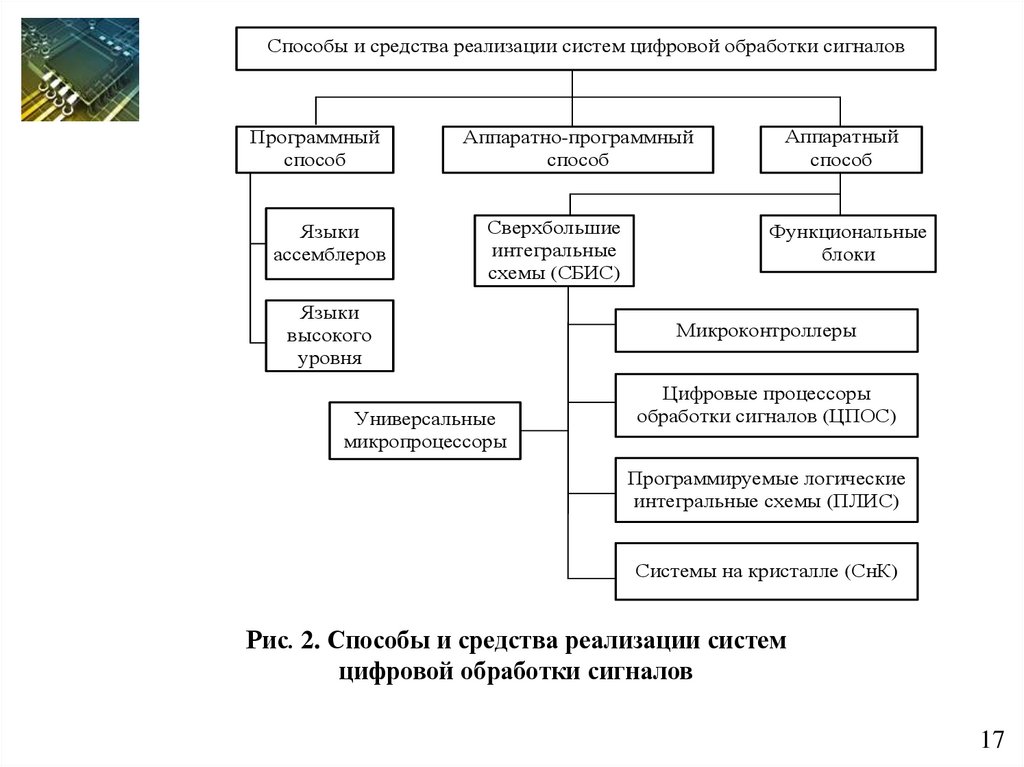

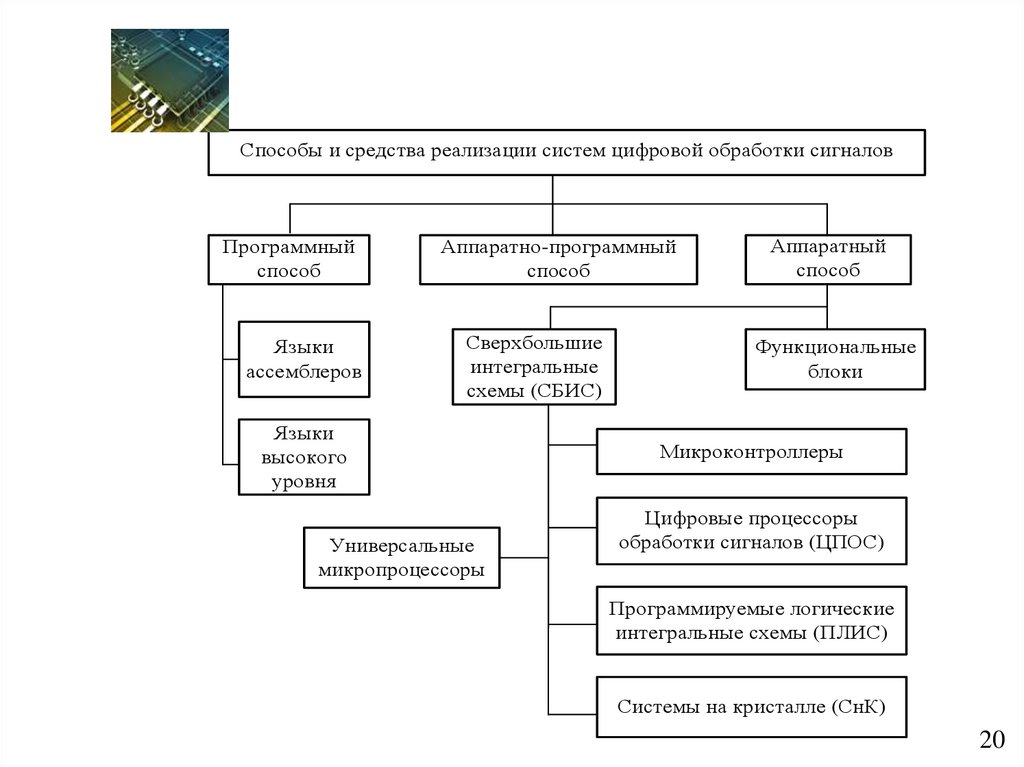

Способы и средства реализации систем цифровой обработки сигналовПрограммный

способ

Языки

ассемблеров

Аппаратно-программный

способ

Сверхбольшие

интегральные

схемы (СБИС)

Языки

высокого

уровня

Универсальные

микропроцессоры

Аппаратный

способ

Функциональные

блоки

Микроконтроллеры

Цифровые процессоры

обработки сигналов (ЦПОС)

Программируемые логические

интегральные схемы (ПЛИС)

Системы на кристалле (СнК)

Рис. 2. Способы и средства реализации систем

цифровой обработки сигналов

17

18.

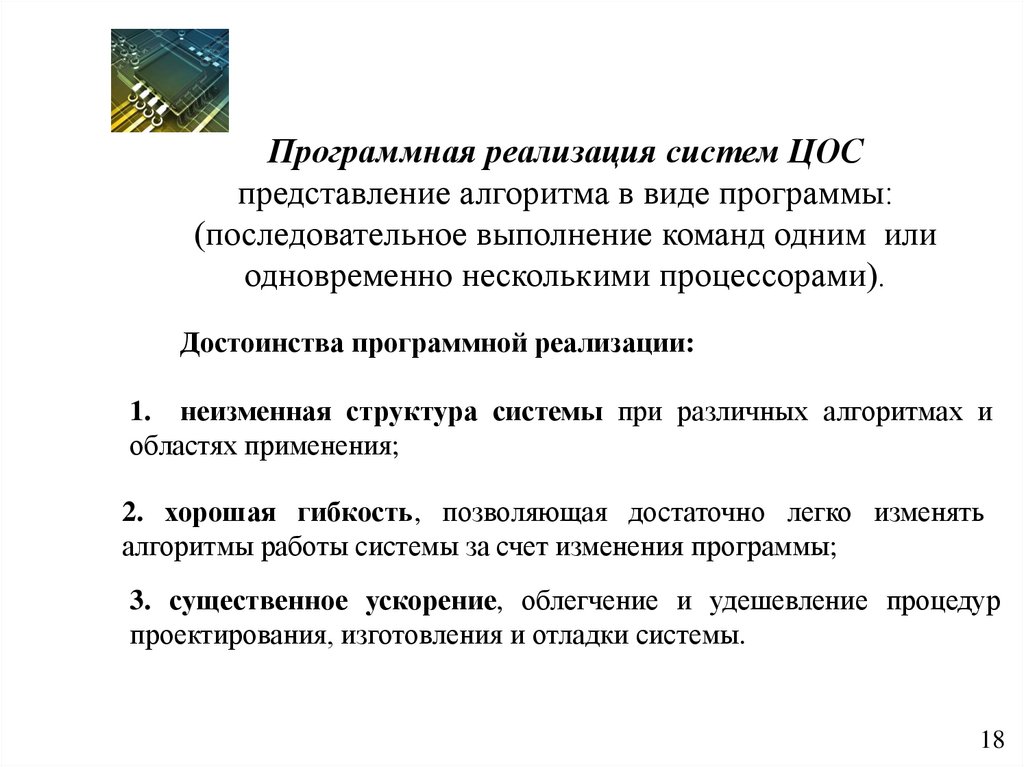

Программная реализация систем ЦОСпредставление алгоритма в виде программы:

(последовательное выполнение команд одним или

одновременно несколькими процессорами).

Достоинства программной реализации:

1. неизменная структура системы при различных алгоритмах и

областях применения;

2. хорошая гибкость, позволяющая достаточно легко изменять

алгоритмы работы системы за счет изменения программы;

3. существенное ускорение, облегчение и удешевление процедур

проектирования, изготовления и отладки системы.

18

19.

Аппаратная реализация систем ЦОСиспользование разнообразных функциональных блоков

(регистров, сумматоров, линий задержки, умножителей,

счетчиков, устройств памяти, логических элементов),

совокупность и порядок связей между которыми определяют

реализуемый алгоритм,

или

интегральных схем, современное поколение которых,

принято называть сверхбольшими интегральными схемами

(СБИС).

19

20.

Способы и средства реализации систем цифровой обработки сигналовПрограммный

способ

Языки

ассемблеров

Аппаратно-программный

способ

Сверхбольшие

интегральные

схемы (СБИС)

Языки

высокого

уровня

Универсальные

микропроцессоры

Аппаратный

способ

Функциональные

блоки

Микроконтроллеры

Цифровые процессоры

обработки сигналов (ЦПОС)

Программируемые логические

интегральные схемы (ПЛИС)

Системы на кристалле (СнК)

20

21.

Цифровые процессоры обработки сигналов (ЦПОС)Системы на кристалле (СнК)

Программируемые логические интегральные схемы (ПЛИС)

21

22.

ЦПОС (DSP)- RISC-процессор (Reduced Instruction Set Computer):

предназначен

для

реализации

алгоритмов

реальном

масштабе

времени

с

цифровых

потоков,

образованных

ЦОС

в

использованием

оцифровкой

аналоговых сигналов.

22

23.

Реальный масштаб временипредполагает,

что

время

выполнения

алгоритма

вычисления не превышает периода дискретизации

(в случае обособленной обработки каждого отсчета

исходного сигнала) или длительности обрабатываемого

кадра (при блочной обработке исходного сигнала), при

этом расчет текущего отсчета (текущего блока отсчетов)

выходного сигнала системы опережает по времени

поступление следующего отсчета (следующего блока

отсчетов) входной последовательности.

23

24.

ПЛИС (PLD)матричные СБИС, обладающие "гибкостью"

архитектуры, что обеспечивает возможность разработчику

самостоятельно конфигурировать СБИС.

ПЛИС обеспечивает:

1. рекордно короткий проектно-технологический цикл,

2. минимальные затраты на проектирование;

3. максимальную

гибкость

при

необходимости

модификации аппаратуры.

24

25.

"Система на кристалле" (СнК)"SOC" - System On the Chip

- технологической основой создания СнК является тенденция

уменьшения размера единичного элемента ЦПОС (например,

элементарного транзистора), обуславливающая рост числа

элементов, интегрированных в одном кристалле. Такая тенденция

обеспечивает возможность размещения на одном кристалле (в

одном корпусе) нескольких вычислительных ядер (как правило,

микроконтроллера для задач управления и, например, одного или

нескольких ЦПОС для задач обработки сигналов) и комплекта

периферийных устройств, необходимого для прогнозируемой

области применения СнК.

25

26.

Достоинство аппаратной реализации состоит вочень высоком быстродействии (обработка

сигналов при требуемых частотах дискретизации).

А недостатки есть ?

26

27.

Выводы по второму вопросу:1. Ознакомились с понятиями:

Программная, аппаратная и аппаратно-программная реализация

систем ЦОС.

2. Ознакомились с достоинствами и недостатками различных

видов реализаций систем ЦОС.

3. Существенно: реальный масштаб времени!

27

28.

3.Архитектура аппаратных средств ЦОС

29.

Наиболее специфические особенности ЦОС :высокая скорость поступления исходных

данных;

широкий динамический диапазон

входных и выходных сигналов;

большое количество операций сложения,

умножения и логических операций

в вычислительных алгоритмах;

необходимость

обеспечения

гибкости и перестройки цифровых

систем;

параллелизм

вычислительных

процедур во многих алгоритмах ЦОС;

повторяемость многих операций

в вычислительных алгоритмах.

29

30.

Свойства ЦПОС:- быстрое выполнение типовых операций ЦОС;

- аппаратная реализация комплексной операции умножения с накоплением;

- аппаратная реализация умножителя, декодера Витерби;

- применение арифметики с фиксированной и плавающей точками (ФТ и

ПТ) при различных форматах представления чисел;

- параллельное выполнение отдельных частей исполняемого алгоритма,

достигаемое аппаратной реализацией ряда типовых алгоритмов ЦОС;

- значительная внутрикристальная память данных и память программ;

- разнообразие режимов адресации применительно к различным задачам:

организация буферов, поддержка бит-реверсивной адресации при расчете

БПФ и т. д.;

- обработка цифровых последовательностей в режиме реального времени;

- наличие внутрикристальной периферии (последовательных и

параллельных интерфейсов, портов ввода и вывода, таймеров и т. д.);

- малое время обращения к элементам внешней периферии.

30

31.

Термин "архитектура" включает в себя описание:состава, принципа действия, конфигурации и взаимного

соединения основных узлов вычислительной системы,

изложение возможностей программирования, форматов

данных, системы команд, способов адресации и т.д.

31

32.

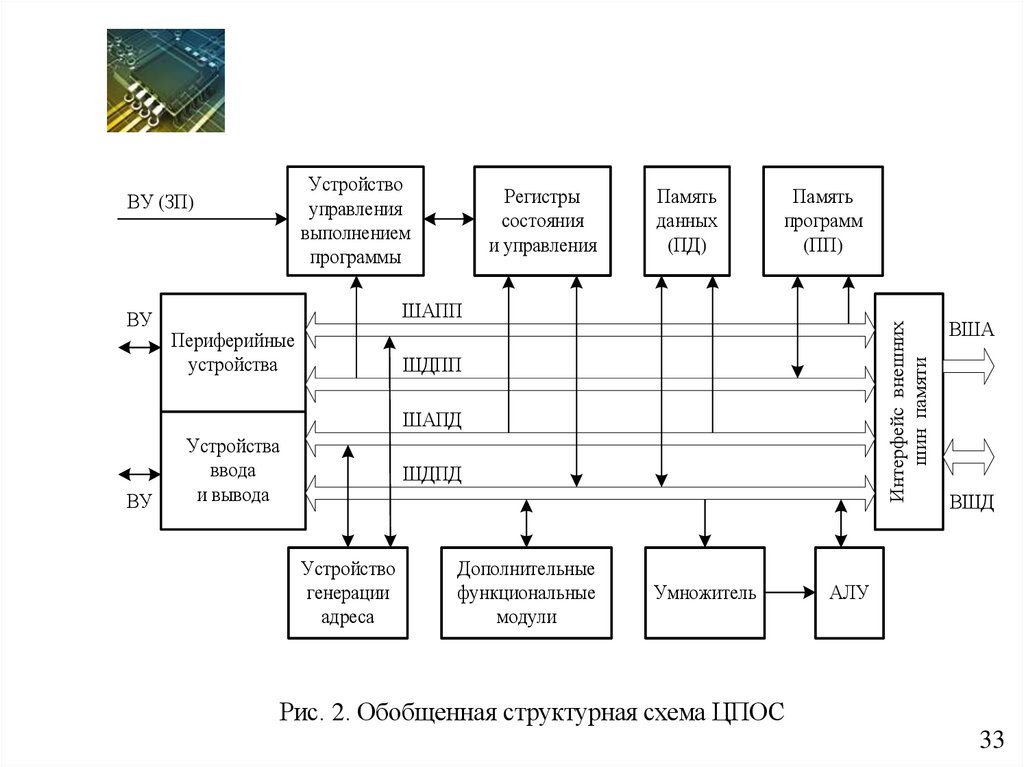

Гарвардская архитектура :аппаратное разделение внутрикристальной памяти на сегменты

памяти программ (ПП) и памяти данных (ПД), а следовательно

организация раздельных шин передачи программ (команд) и данных, что

позволяет полностью совмещать по времени выборку и исполнение

команд.

Модифицированная гарвардская архитектура ЦПОС предоставляет

возможность обмена данными между ПП и ПД (значительно расширяет

возможности устройства).

Способ повышения производительности ЦПОС - использование

конвейерного режима обработки данных (исполнительное устройство

одновременно обрабатывает несколько различных команд)

32

33.

Устройствоуправления

выполнением

программы

ВУ (ЗП)

Память

данных

(ПД)

Память

программ

(ПП)

ШАПП

Периферийные

устройства

Интерфейс внешних

шин памяти

ВУ

Регистры

состояния

и управления

ШДПП

ШАПД

ВУ

Устройства

ввода

и вывода

ШДПД

Устройство

генерации

адреса

Дополнительные

функциональные

модули

Умножитель

ВША

ВШД

АЛУ

Рис. 2. Обобщенная структурная схема ЦПОС

33

34.

1. Технология производстваКМОП-технология (комплементарная структура "металлокисел-полупроводник")

2. Формы представления чисел: с фиксированной

точкой (ФТ), либо с плавающей точкой (ПТ); отдельные

семейства ЦПОС поддерживают обе формы.

34

35.

3. Форматы представления чисел.Кодовые слова длиной в 16, 24, 32 и 40 бит.

4. Код представления чисел.

ФТ - дополнительный код, ПТ - прямой код.

5. Внутренняя тактовая частота

Тактовая частота определяет длительность командного цикла

процессора.

Некоторые семейства ЦПОС имеют встроенные системы деления или

умножения частоты и используют параллельное выполнение команд и

параллельную работу нескольких независимых операционных модулей.

35

36.

6. ПроизводительностьПиковая

производительность

теоретический

-

максимум быстродействия процессора при идеальных

условиях,

который

вычислительных

времени

всеми

определяется

команд,

выполняемых

имеющимися

в

как

число

в

единицу

процессоре

арифметическими устройствами.

36

37.

Показатели пиковой производительности :-

количество

миллионов

команд

(инструкций),

выполняемых процессором за секунду (MIPS Million of

Instructions Per Second) при представлении данных в форме

с ФТ;

-количество миллионов операций, выполняемых за секунду

при арифметике с ПТ (MFLOPS Million of Floating-point

Operations Per Second);

- количество миллионов операций (MOPS) или миллионов

операций умножения с накоплением в секунду (MMACS).

37

38.

Повышениепиковой

производительности

ЦПОС

относительно тактовой частоты достигается архитектурными

решениями, направленными на увеличение степени параллелизма в

обработке данных (одновременное выполнение в процессоре

нескольких команд или операций).

увеличение

количества

функциональных модулей процессора

(АЛУ, умножителей);

увеличение

количества

дополнительных специализированных

устройств и сопроцессоров (например,

переход к многоядерным процессорам);

увеличение разрядности шин

передачи данных и программ для

увеличения количества одновременно

передаваемой информации.

38

39.

Реальнаяпроизводительность

оценивается

временем выполнения стандартных алгоритмов ЦОС,

при этом преимущество имеет

не всегда ЦПОС с

большей пиковой производительностью.

Например, ЦПОС ADSP 21160N (пиковая производительность

600 MFLOPS) имеет большую реальную производительность по

выполнению алгоритма БПФ на 1024 отсчета, чем TMS320C6701

(пиковая производительность 1 GFLOPS): время выполнения этой

операции указанными процессорами составляет 90 и 120 мкс

соответственно.

39

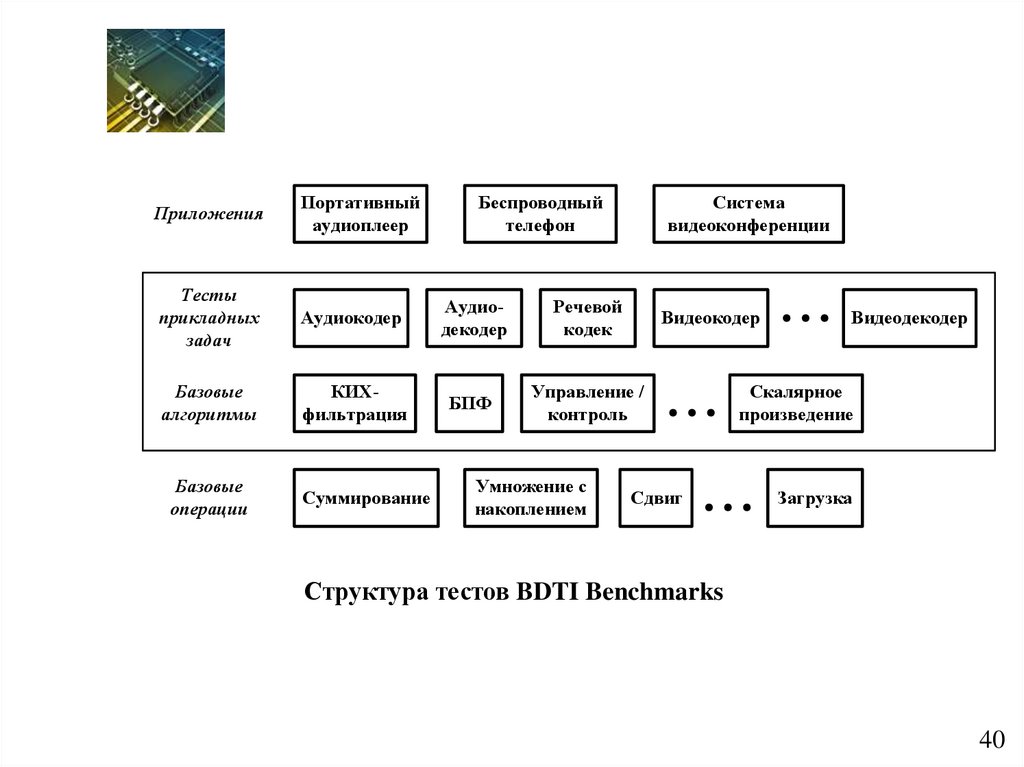

40.

ПриложенияПортативный

аудиоплеер

Беспроводный

телефон

Тесты

прикладных

задач

Аудиокодер

Аудиодекодер

Речевой

кодек

Базовые

алгоритмы

КИХфильтрация

БПФ

Управление /

контроль

Базовые

операции

Суммирование

Умножение с

накоплением

Система

видеоконференции

Видеокодер

Сдвиг

Видеодекодер

Скалярное

произведение

Загрузка

Структура тестов BDTI Benchmarks

40

41.

7. Объем и разновидность внутренней памяти ЦПОС во многомопределяют характеристики и возможности реализуемой системы ЦОС.

Основными признаками классификации внутренней памяти ЦПОС

являются вид хранимой информации, степень доступности на этапах

разработки и функционирования системы, тип элементарной ячейки.

По виду хранимой информации память процессора

классифицируется на ПП и ПД (в ряде ЦПОС жесткое (аппаратное)

разделение ресурса памяти на ПП и ПД не применяется, при этом

распределение общего ресурса осуществляется программно).

По степени доступности элементов памяти она разделяется:

на ПЗУ (ROM Read Only Memory) и ОЗУ (RAM Random Access

Memory).

Разновидностью ПЗУ - флэш-память (flash memory), позволяющая

неоднократное перезаписывание программы и данных.

Кэш-память (cache memory-CM) - буферная память между собственно

процессором (его АЛУ) и ОЗУ. По типу элементарной ячейки память

подразделяется на динамическую (миниатюрные конденсаторы), и

статическую (транзисторы).

41

42.

8. Напряжение питания является характеристикой ЦПОС, особенноважной при разработке носимых систем ЦОС с батарейным питанием.

Кроме указанных, на выбор типа ЦПОС для разработки системы

ЦОС значительное влияние оказывают следующие характеристики

процессора:

температурный диапазон функционирования ЦПОС;

наличие и удобство в использовании аппаратных и

программных средств разработки систем ЦОС;

стоимость и габариты процессора;

совместимость процессора с существующей элементной базой

реализации алгоритмов ЦОС;

количество и разновидность портов ввода/вывода информации;

комплект внутренних периферийных устройств;

наличие и количество каналов прямого доступа к памяти.

42

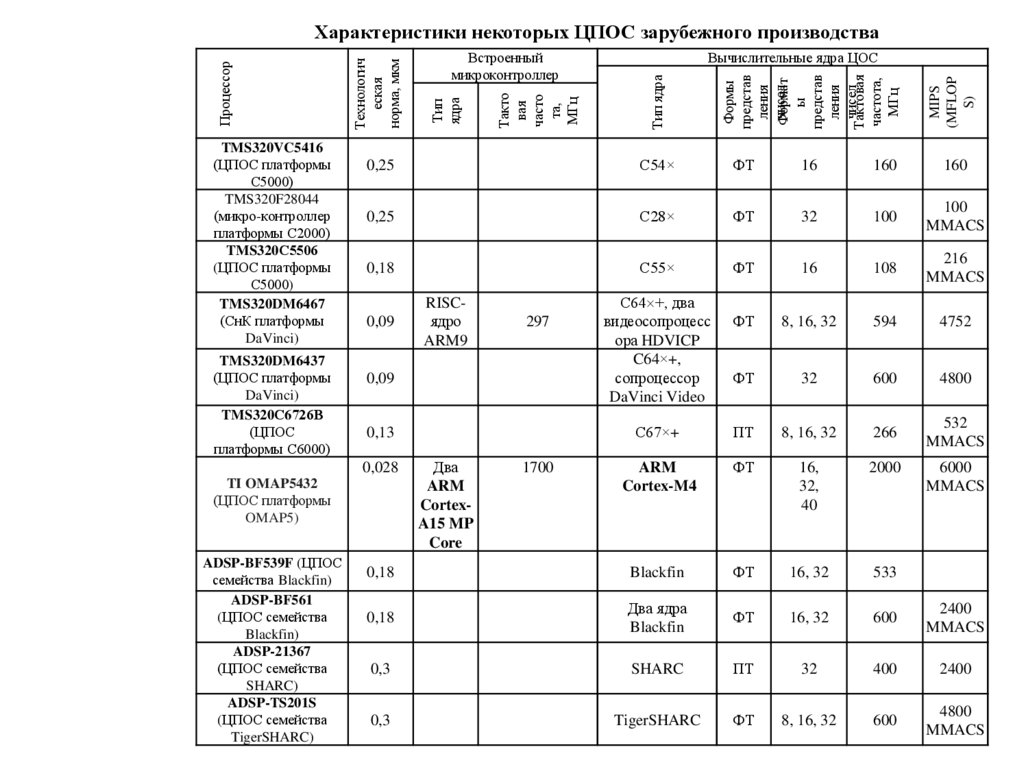

43.

TMS320VC5416(ЦПОС платформы

С5000)

TMS320F28044

(микро-контроллер

платформы С2000)

TMS320С5506

(ЦПОС платформы

С5000)

TMS320DM6467

(СнК платформы

DaVinci)

TMS320DM6437

(ЦПОС платформы

DaVinci)

TMS320С6726В

(ЦПОС

платформы С6000)

MIPS

(MFLOP

S)

Формы

представ

ления

чисел

Формат

ы

представ

ления

чисел

Тактовая

частота,

МГц

Тип ядра

Такто

вая

часто

та,

МГц

Вычислительные ядра ЦОС

0,25

С54×

ФТ

16

160

160

0,25

С28×

ФТ

32

100

100

MMACS

0,18

С55×

ФТ

16

108

216

MMACS

ФТ

8, 16, 32

594

4752

ФТ

32

600

4800

С67×+

ПТ

8, 16, 32

266

532

MMACS

ARM

Cortex-M4

ФТ

16,

32,

40

2000

0,18

Blackfin

ФТ

16, 32

533

0,18

Два ядра

Blackfin

ФТ

16, 32

600

2400

MMACS

0,3

SHARC

ПТ

32

400

2400

0,3

TigerSHARC

ФТ

8, 16, 32

600

4800

MMACS

0,09

RISCядро

ARM9

297

0,09

0,13

0,028

TI OMAP5432

(ЦПОС платформы

OMAP5)

ADSP-BF539F (ЦПОС

семейства Blackfin)

ADSP-BF561

(ЦПОС семейства

Blackfin)

ADSP-21367

(ЦПОС семейства

SHARC)

ADSP-TS201S

(ЦПОС семейства

TigerSHARC)

Встроенный

микроконтроллер

Тип

ядра

Технологич

еская

норма, мкм

Процессор

Характеристики некоторых ЦПОС зарубежного производства

Два

ARM

CortexA15 MP

Core

1700

С64 +, два

видеосопроцесс

ора HDVICP

C64×+,

сопроцессор

DaVinci Video

6000

MMACS

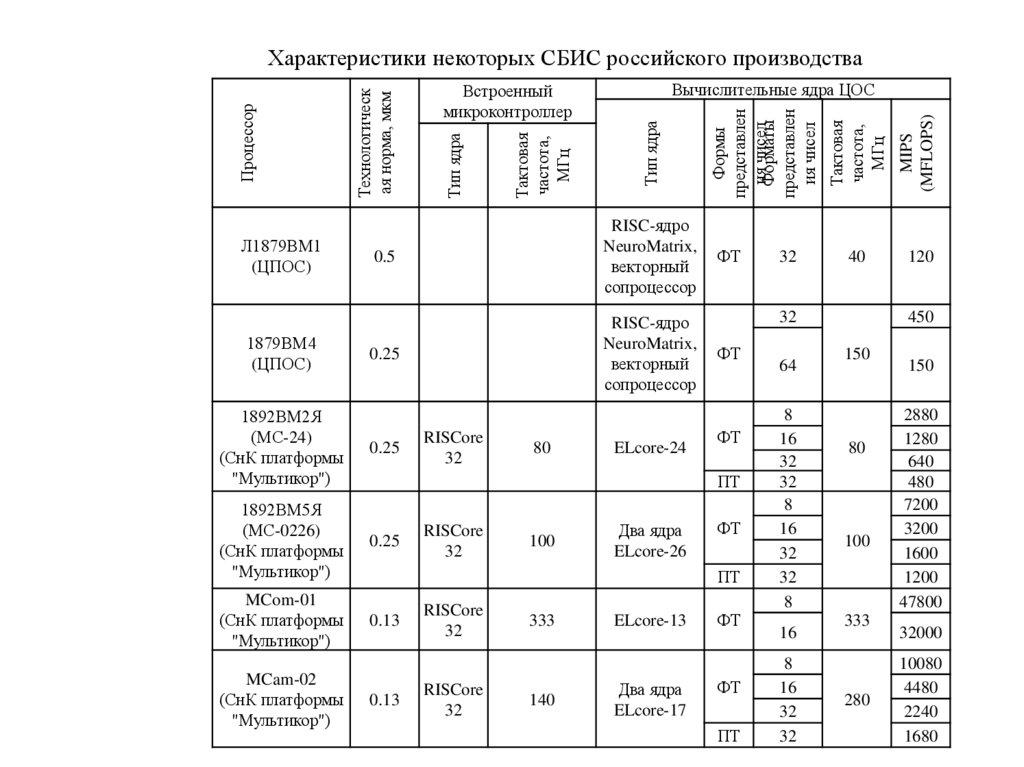

44.

1879ВМ4(ЦПОС)

0.25

1892ВМ5Я

(МС-0226)

(СнК платформы

"Мультикор")

0.25

MCom-01

(СнК платформы

"Мультикор")

0.13

RISCore

32

80

ELcore-24

MIPS

(MFLOPS)

0.25

RISC-ядро

NeuroMatrix,

векторный

сопроцессор

Тактовая

частота,

МГц

0.5

представлен

ия чисел

Тип ядра

Тактовая

частота,

МГц

Тип ядра

Вычислительные ядра ЦОС

RISC-ядро

NeuroMatrix,

векторный

сопроцессор

1892ВМ2Я

(МС-24)

(СнК платформы

"Мультикор")

MCam-02

(СнК платформы

"Мультикор")

Встроенный

микроконтроллер

Формы

представлен

ия чисел

Форматы

Л1879ВМ1

(ЦПОС)

Технологическ

ая норма, мкм

Процессор

Характеристики некоторых СБИС российского производства

ФТ

32

40

120

32

ФТ

ФТ

ПТ

RISCore

32

100

Два ядра

ELcore-26

ФТ

ПТ

0.13

RISCore

32

RISCore

32

333

140

ELcore-13

Два ядра

ELcore-17

ФТ

ФТ

ПТ

64

8

16

32

32

8

16

32

32

8

16

8

16

32

32

450

150

80

100

333

280

150

2880

1280

640

480

7200

3200

1600

1200

47800

32000

10080

4480

2240

1680

45.

Выводы по третьему вопросу1. При построении ЦПОС используется гарвардская

архитектура!

2. Гарвардская архитектура предусматривает разделение памяти

программ и памяти данных.

3. Модифицированная гарвардская архитектура обеспечивает

взаимодействие сегмента памяти программ и памяти данных.

45

46.

Методические указания и задание для самостоятельной работы:1. Повторение изученного материала

по современной и перспективной элементной базе

реализации алгоритмов ЦОС,

характеристикам цифровых процессоров обработки сигналов.

2. Ознакомление с базой тестовых

заданий по теме № 1.

46

47.

Тема № 1.ПРЕДСТАВЛЕНИЕ ДИСКРЕТНЫХ СИГНАЛОВ

Занятие № 2. Лекция № 2.

Обработка сигналов в ЦОС

Учебные вопросы

1. Основные операции ЦОС.

2. Средства реализации систем ЦОС.

3. Архитектура аппаратных средств ЦОС.

Кафедра «Электроника

и теория связи»

Электроника

Электроника