Похожие презентации:

Временные ограничения цифровых схем

1. Временные ограничения цифровых схем

Григорий Кузьмин2016

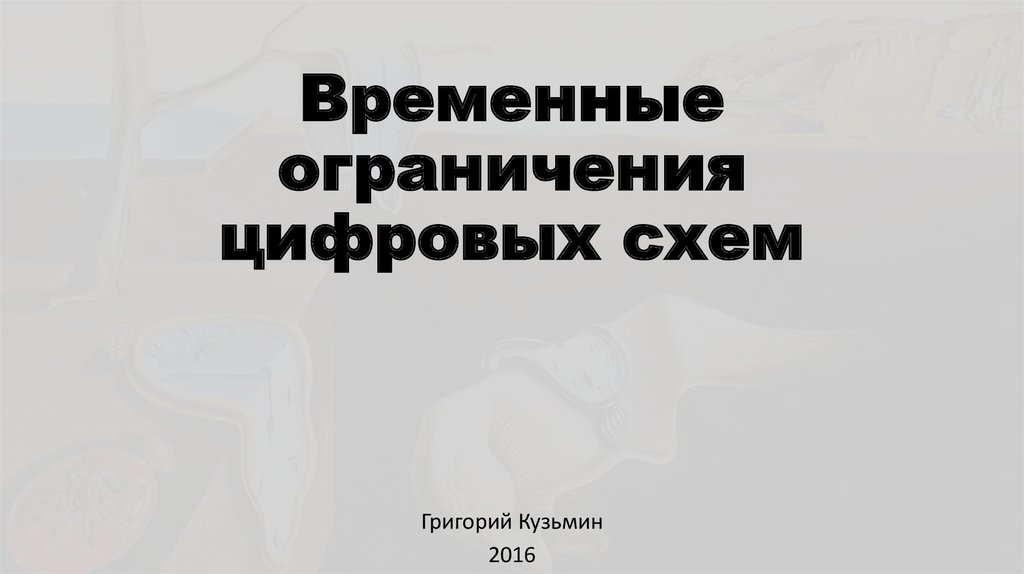

2. Комбинационная логика

ВходыCL

Выходы

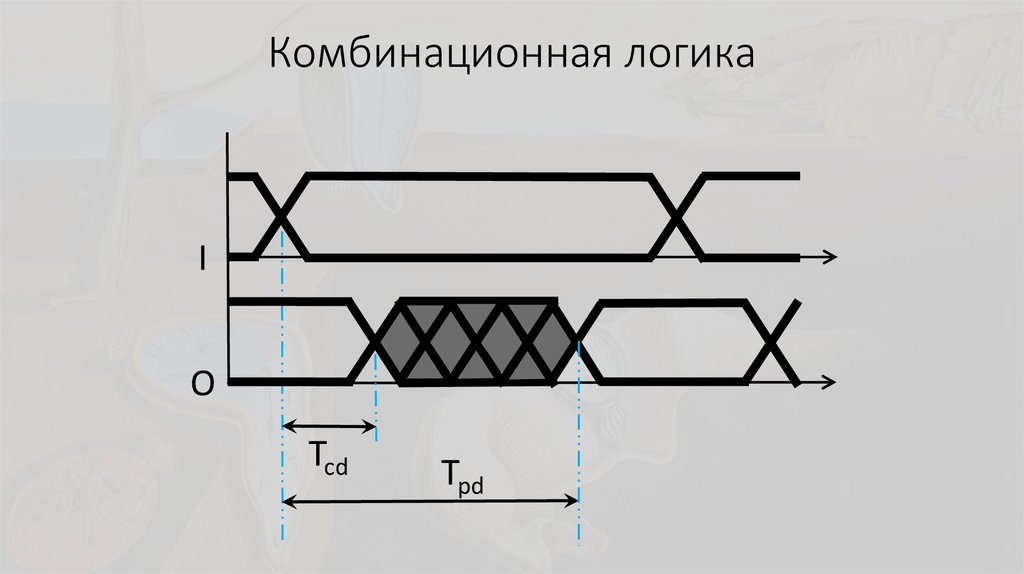

3. Комбинационная логика

IO

Tcd

Tpd

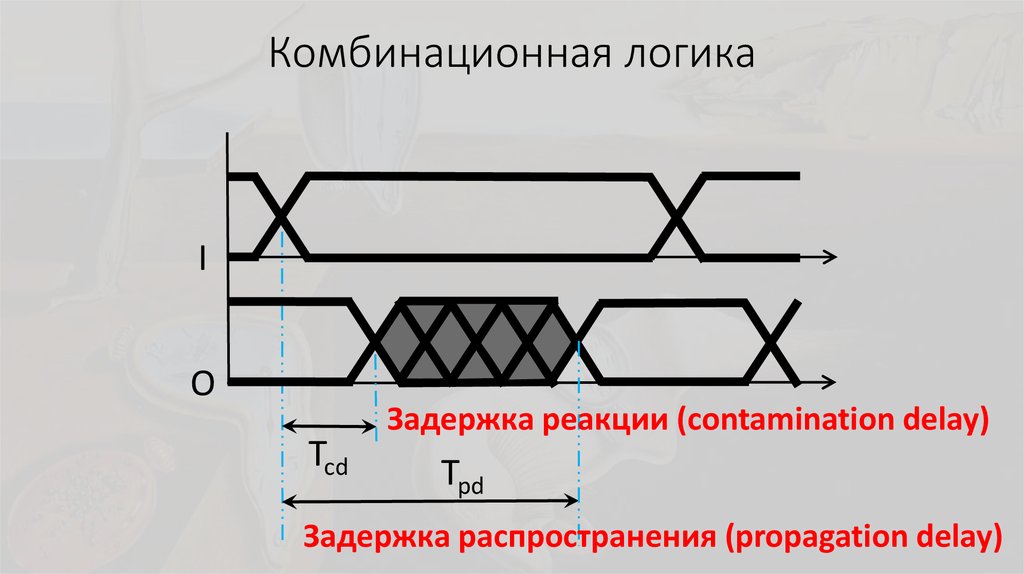

4. Комбинационная логика

IO

Tcd

Задержка реакции (contamination delay)

Tpd

Задержка распространения (propagation delay)

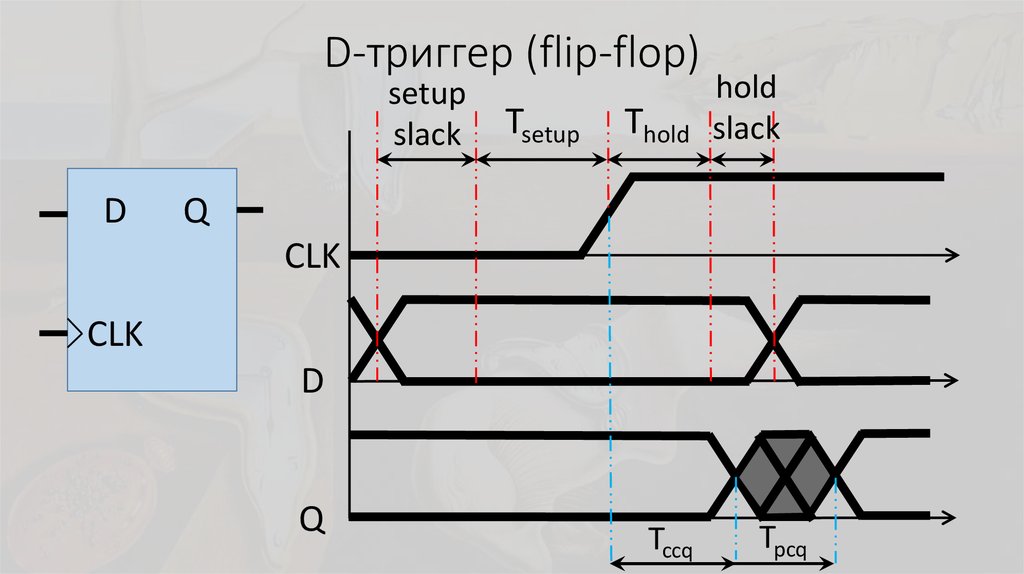

5. D-триггер (flip-flop)

setupslack

D

Tsetup

Thold

hold

slack

Q

CLK

CLK

D

Q

Tccq

Tpcq

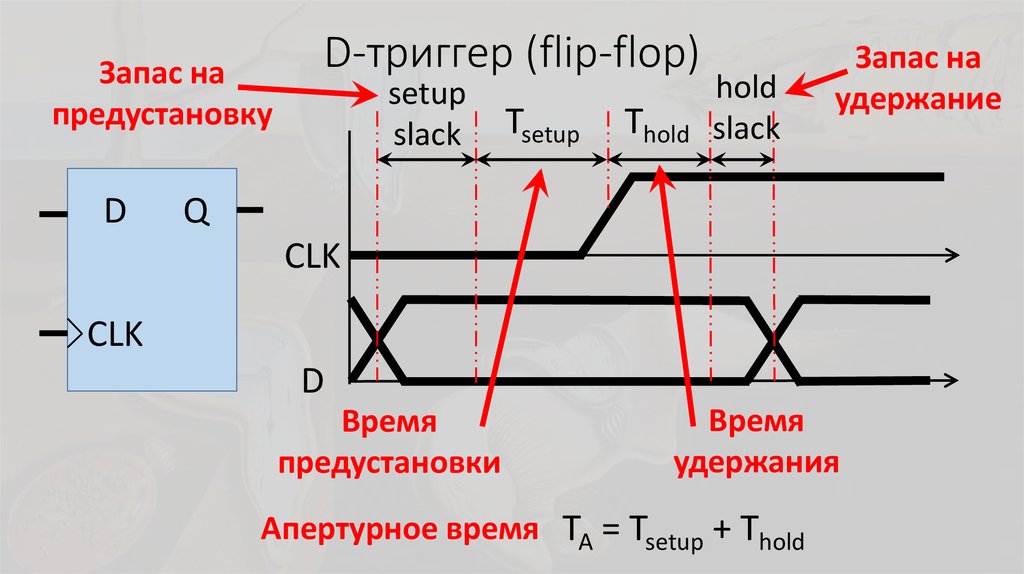

6. D-триггер (flip-flop)

Запас напредустановку

D

D-триггер (flip-flop)

setup

slack

Tsetup

Thold

hold

slack

Запас на

удержание

Q

CLK

CLK

D

Время

предустановки

Время

удержания

Апертурное время TA = Tsetup + Thold

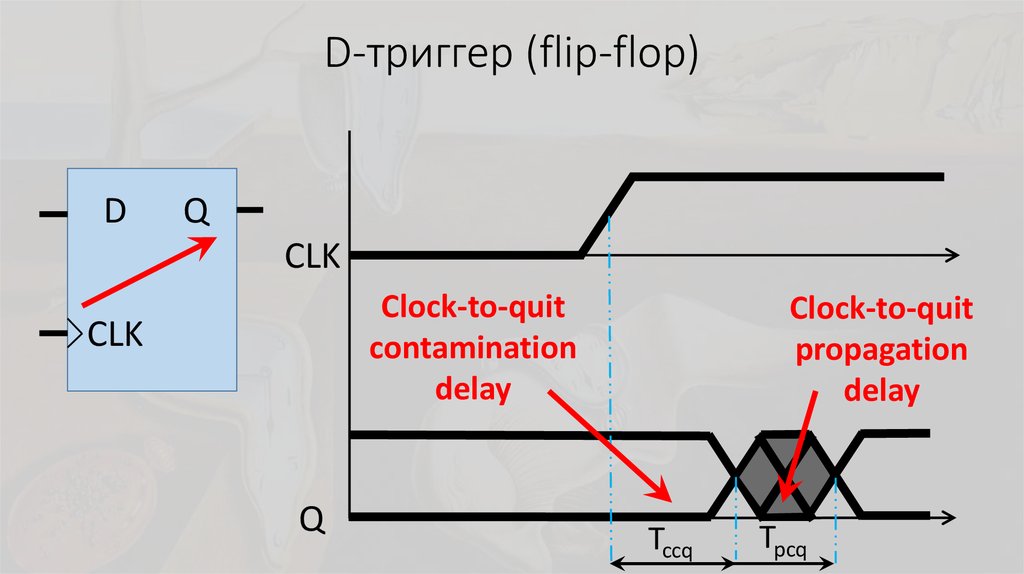

7. D-триггер (flip-flop)

DQ

CLK

Clock-to-quit

contamination

delay

CLK

Q

Clock-to-quit

propagation

delay

Tccq

Tpcq

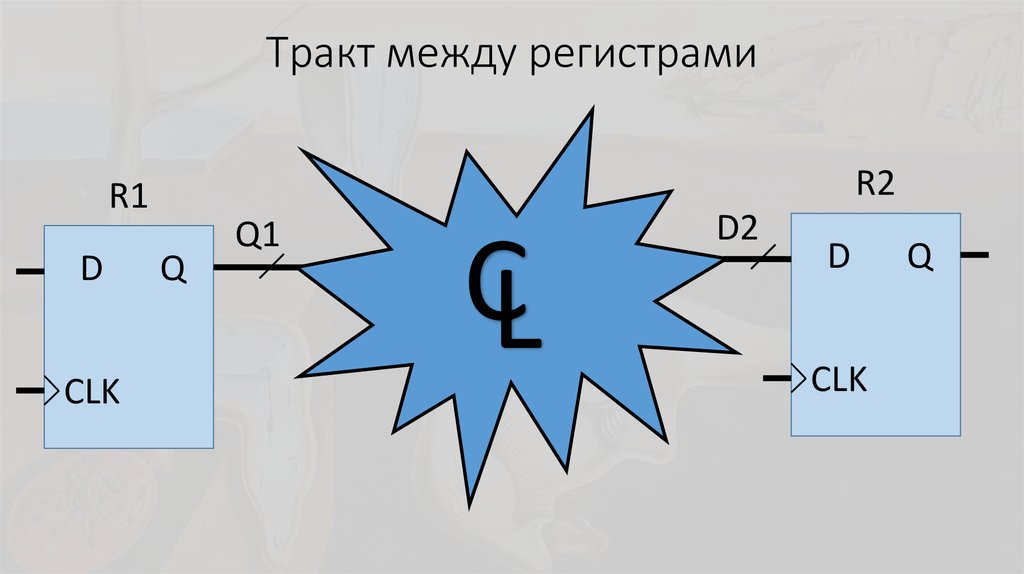

8. Тракт между регистрами

R2R1

D

CLK

Q

Q1

CL

D2

D

CLK

Q

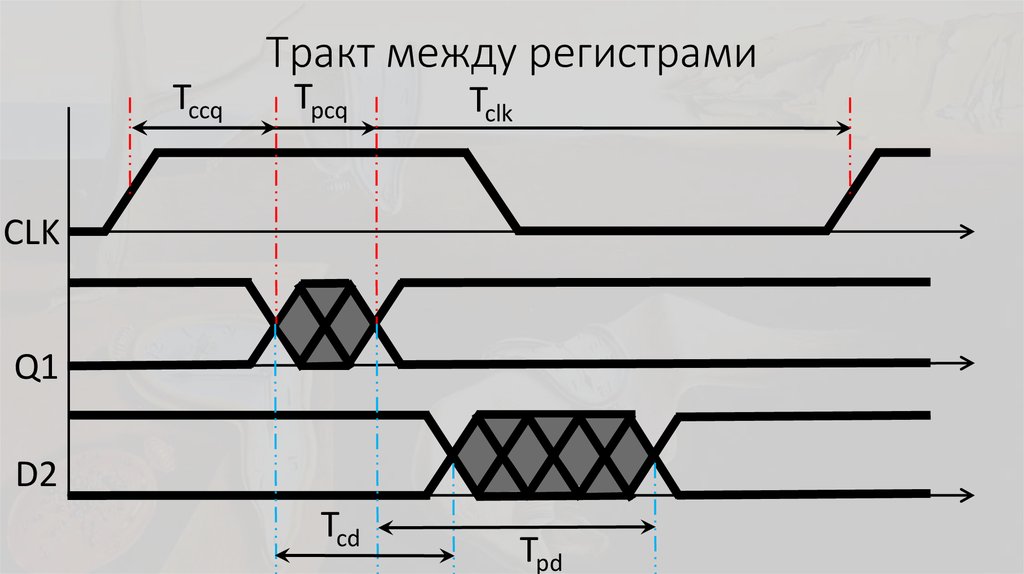

9. Тракт между регистрами

TccqTpcq

Tclk

CLK

Q1

D2

Tcd

Tpd

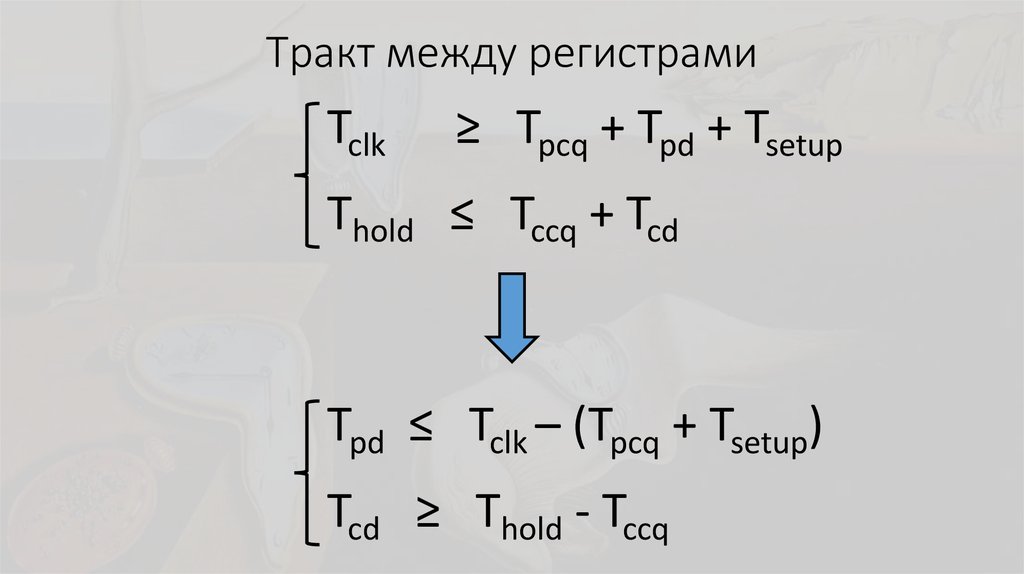

10. Тракт между регистрами

Tclk≥ Tpcq + Tpd + Tsetup

Thold ≤ Tccq + Tcd

Tpd ≤ Tclk – (Tpcq + Tsetup)

Tcd ≥ Thold - Tccq

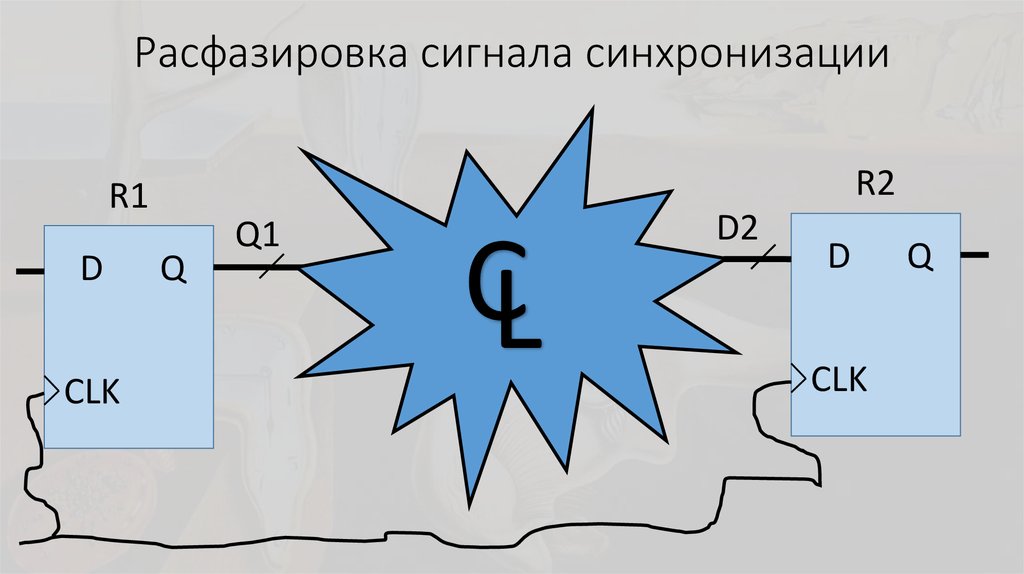

11. Расфазировка сигнала синхронизации

R2R1

D

CLK

Q

Q1

CL

D2

D

CLK

Q

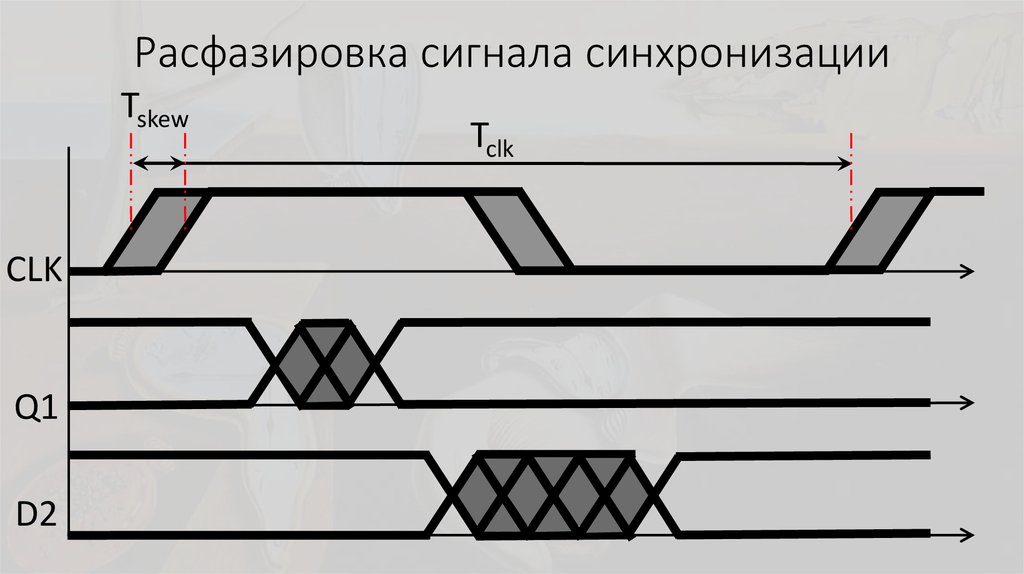

12. Расфазировка сигнала синхронизации

TskewCLK

Q1

D2

Tclk

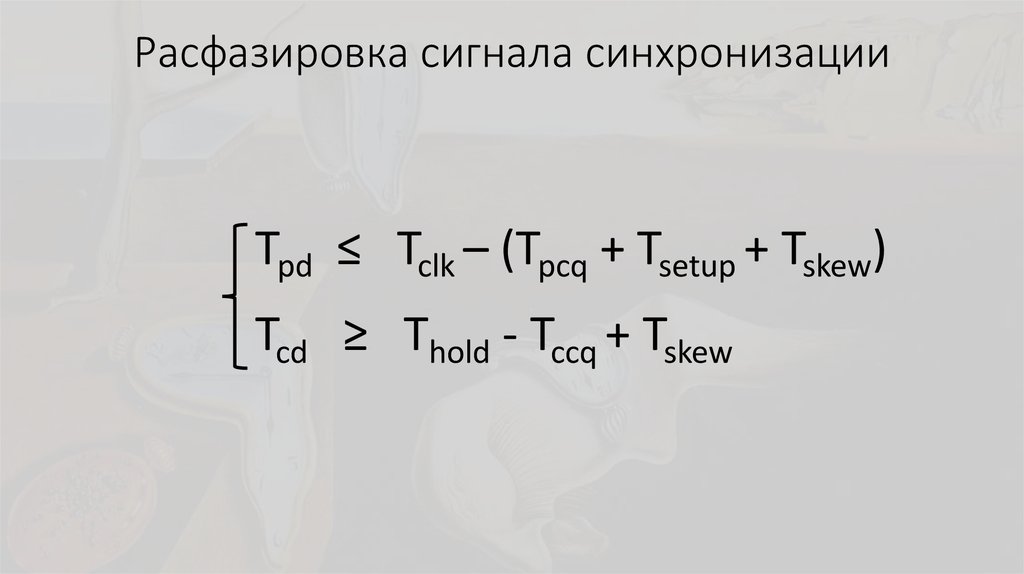

13. Расфазировка сигнала синхронизации

Tpd ≤ Tclk – (Tpcq + Tsetup + Tskew)Tcd ≥ Thold - Tccq + Tskew

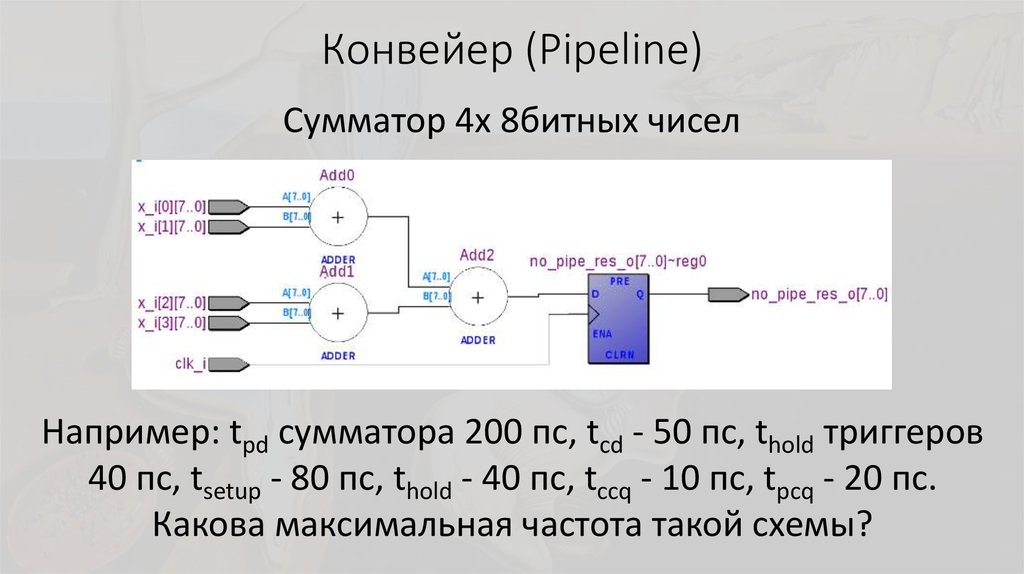

14. Конвейер (Pipeline)

Сумматор 4х 8битных чиселНапример: tpd сумматора 200 пс, tсd - 50 пс, thold триггеров

40 пс, tsetup - 80 пс, thold - 40 пс, tccq - 10 пс, tpcq - 20 пс.

Какова максимальная частота такой схемы?

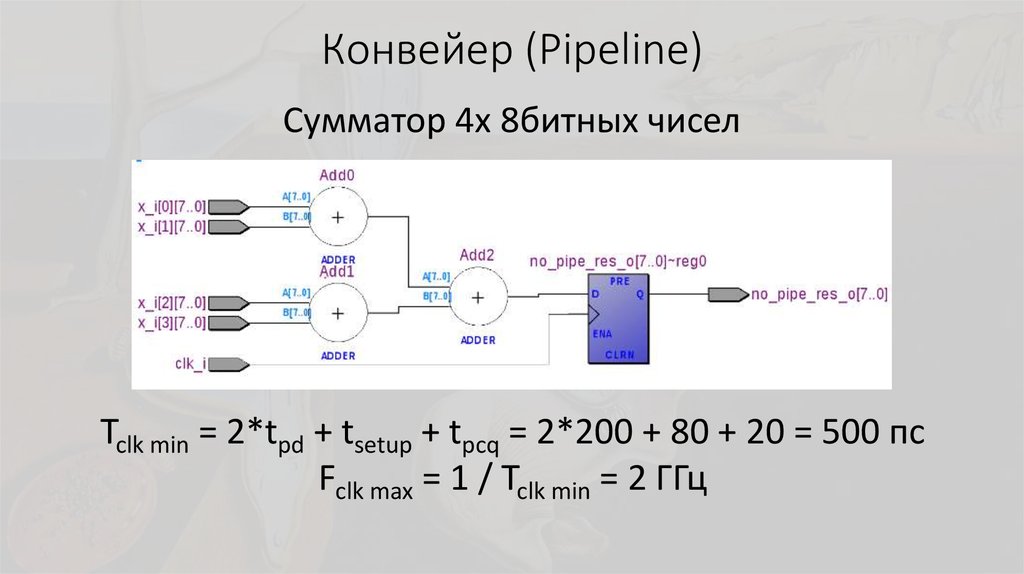

15. Конвейер (Pipeline)

Сумматор 4х 8битных чиселTclk min = 2*tpd + tsetup + tpcq = 2*200 + 80 + 20 = 500 пс

Fclk max = 1 / Tclk min = 2 ГГц

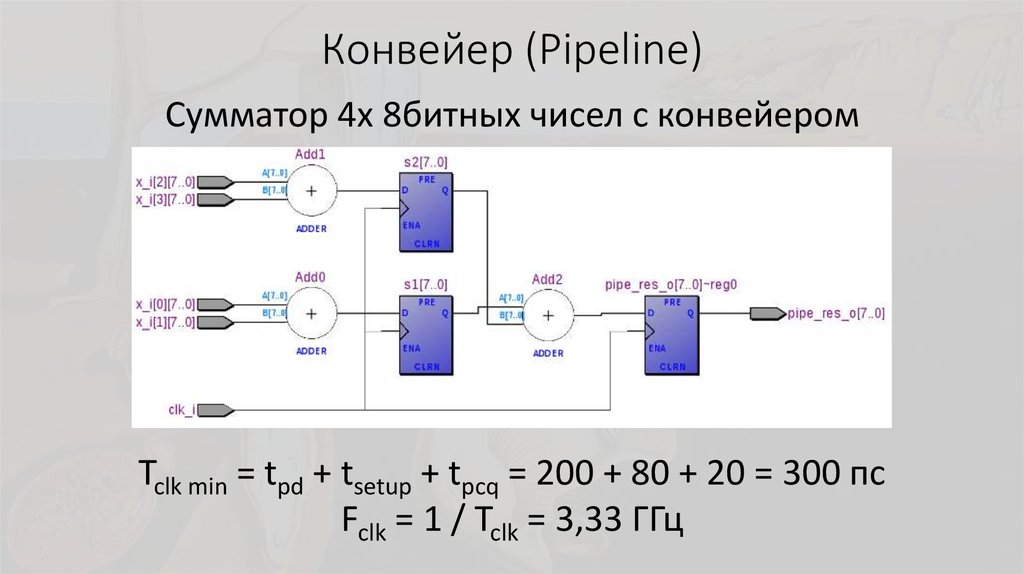

16. Конвейер (Pipeline)

Сумматор 4х 8битных чисел с конвейеромTclk min = tpd + tsetup + tpcq = 200 + 80 + 20 = 300 пс

Fclk = 1 / Tclk = 3,33 ГГц

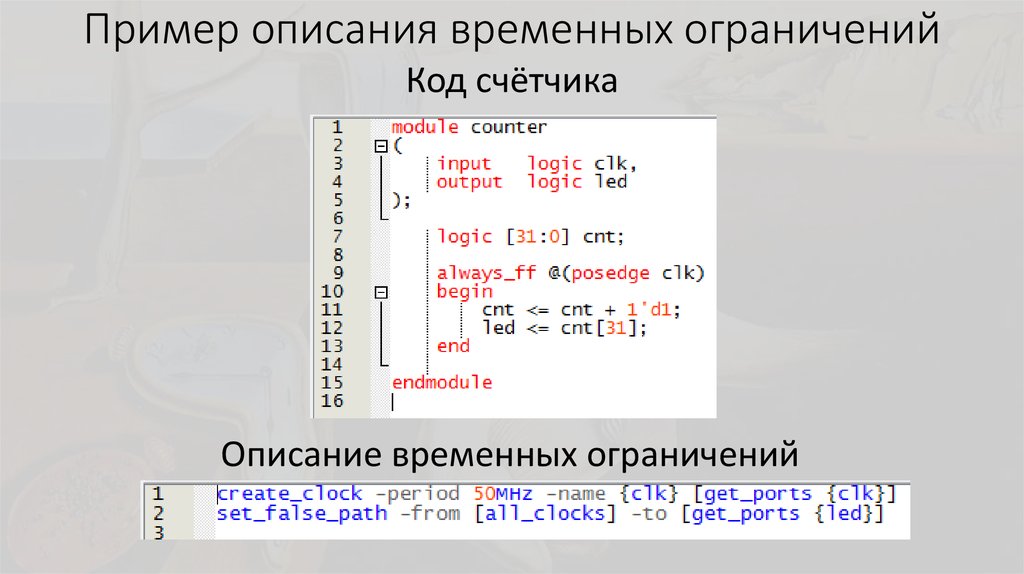

17. Пример описания временных ограничений

Код счётчикаОписание временных ограничений

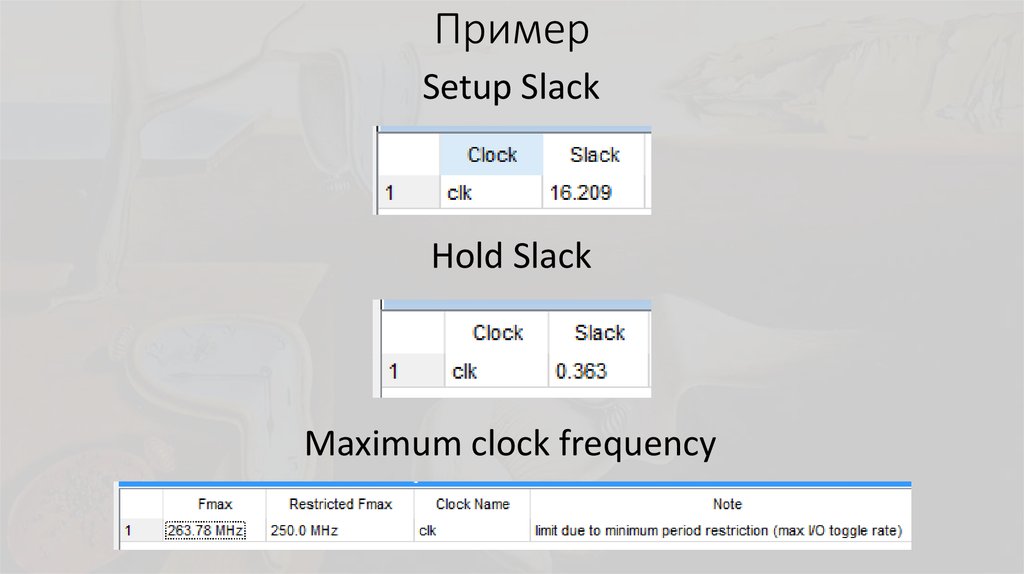

18. Пример

Setup SlackHold Slack

Maximum clock frequency

Информатика

Информатика