Похожие презентации:

Вычислительная техника и информационные технологии

1. Вычислительная техника и информационные технологии

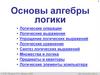

Харина Н.Л., доцент каф.РЭС2. Представление информации физическими сигналами

U0

0

1

U"1"

1

0

1

1

0

t

U"0"

0

1

2

3

4

5

6

7

8

Представление цифровой информации

сигналами потенциального типа

(последовательный код).

Представление информации параллельным

кодом

3. КЛАССИФИКАЦИЯ ЦУ

По способу ввода и выводаУстройства

последовательностн

ого действия

Устройства

параллельного

действия

Устройства

смешанного

действия

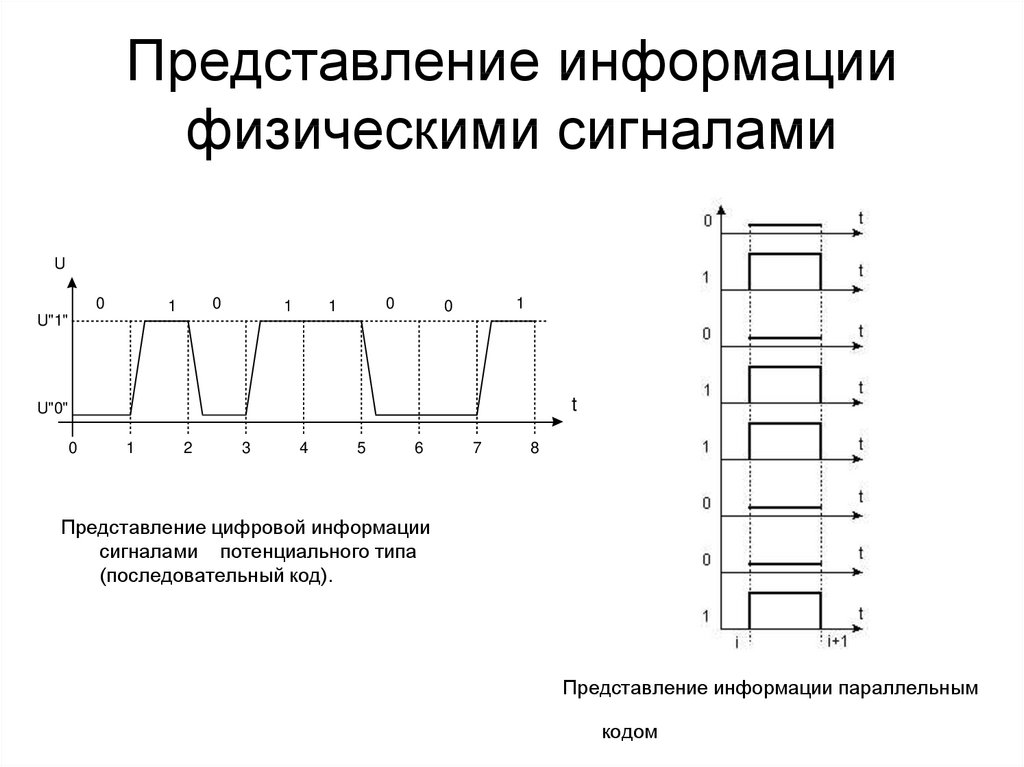

4. КЛАССФИКАЦИЯ ЦУ

По способу функционированияКомбинационные

устройства

Последовательностные

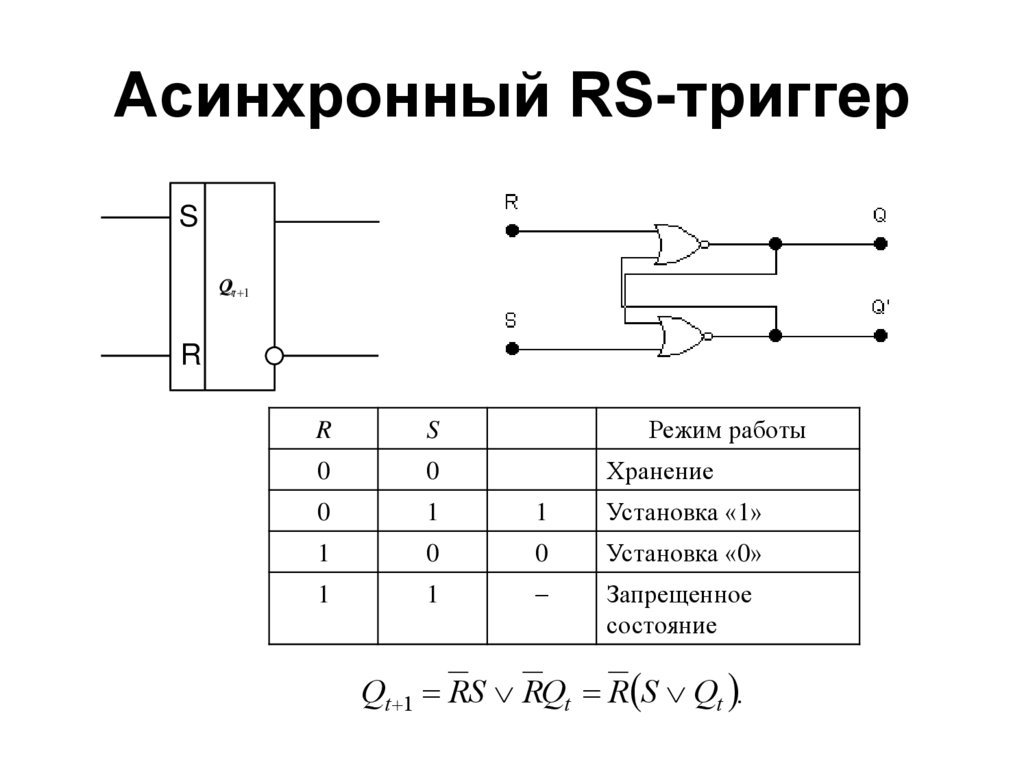

устройства

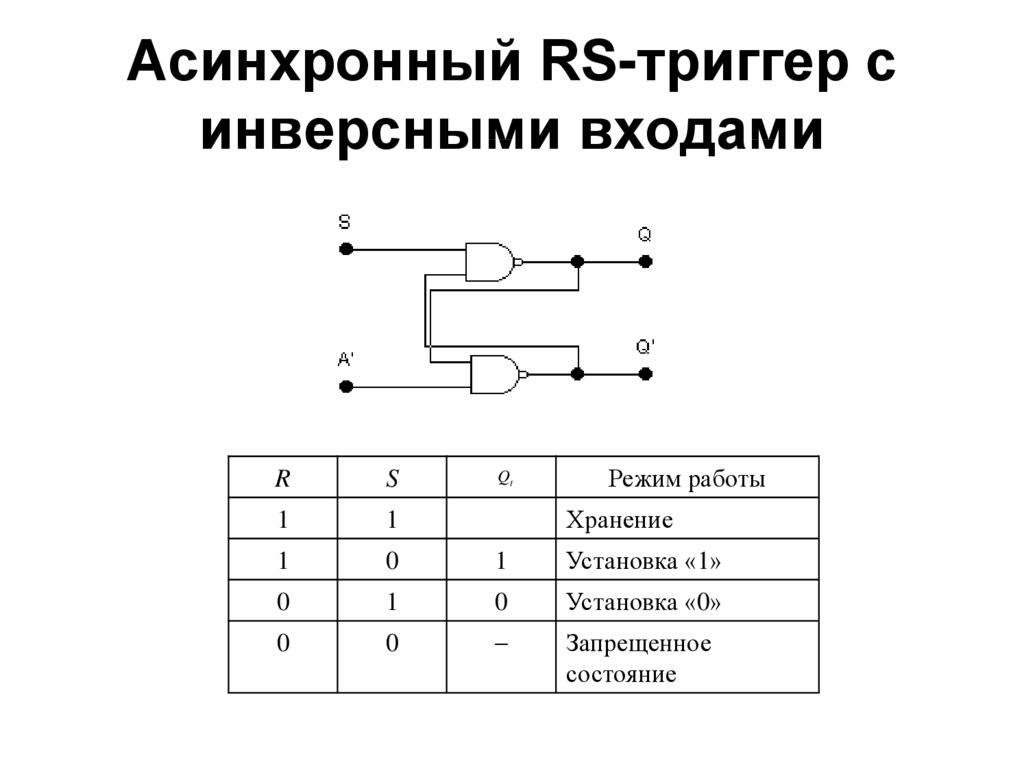

5. БУЛЕВА АЛГЕБРА

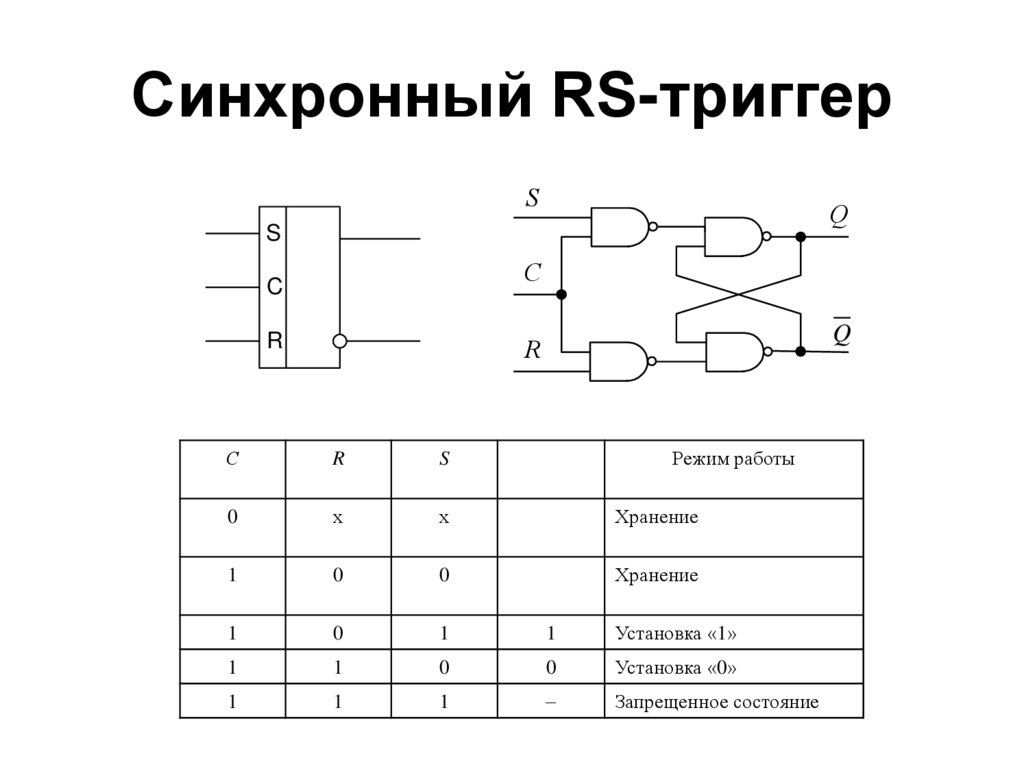

СПОСОБЫ ЗАДАНИЯ ЛОГИЧЕСКИХФУНКЦИЙ

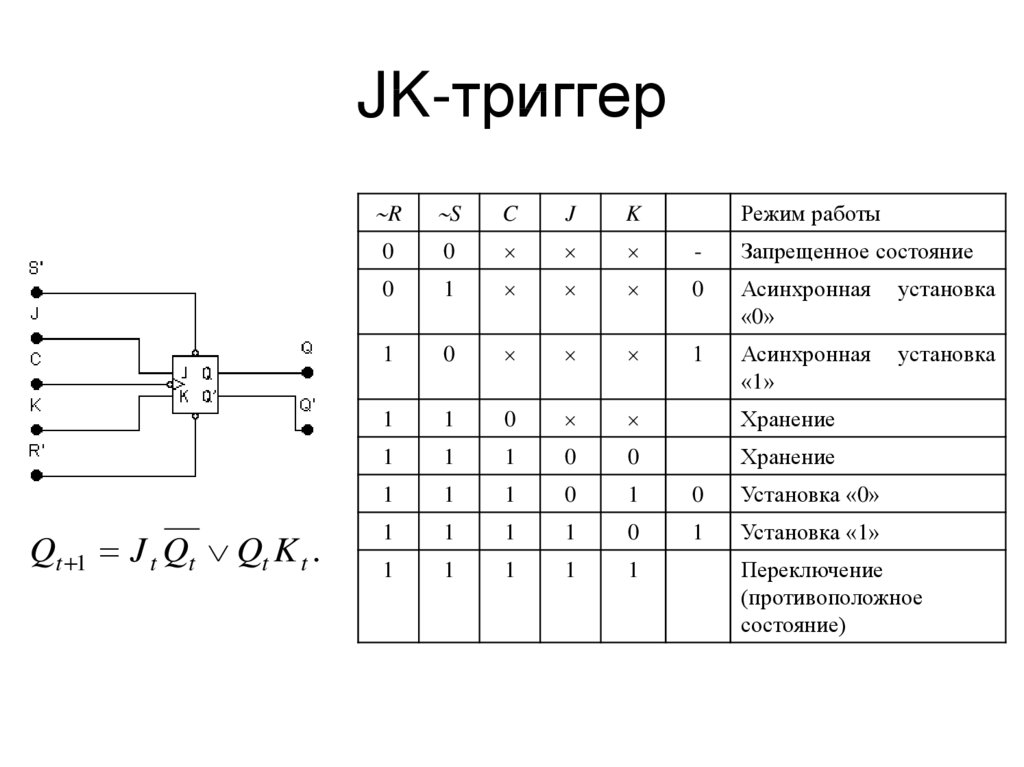

• ТАБЛИЦА ИСТИННОСТИ

• БУЛЕВО ВЫРАЖЕНИЕ

• СХЕМА НА ЛОГИЧЕСКИХ ЭЛЕМЕНТАХ

6. ТАБЛИЦА ИСТИННОСТИ

Аргументы

Значения функции

х

у

F0

F1

F2

F3

F4

F5

F6

F7

F8

F9

F10

F11

F12

F13

F14

F15

0

0

0

0

0

0

0

0

0

0

1

1

1

1

1

1

1

1

0

1

0

0

0

0

1

1

1

1

0

0

0

0

1

1

1

1

1

0

0

0

1

1

0

0

1

1

0

0

1

1

0

0

1

1

1

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

7. ЛОГИЧЕСКИЕ ФУНКЦИИ

Условное обозначениеНазвание

0000

0001

«0»

Константа нуля

«^»(*)

Конъюнкция (И)

0010

0011

0100

~ХY

X

X~Y

Запрет Х

Y

Повторение Y

F6

0101

0110

X+Y

Исключающее ИЛИ

F7

0111

«˅»(+)

Дизъюнкция (ИЛИ)

F0

F1

F2

F3

F4

F5

Повторение Х

Запрет Y

8. ЛОГИЧЕСКИЕ ФУНКЦИИ

Условноеобозначение

Название

1000

1001

Х↓У

Стрелка Пирса (ИЛИ-НЕ)

Х~Y

Равнозначность

~Х

X→Y

~Y

Y→X

Отрицание Х

F14

1010

1011

1100

1101

1110

XǀY

Штрих Шеффера (И-НЕ)

F15

1111

«1»

Константа единицы

F8

F9

F10

F11

F12

F13

Импликация от Х к Y

Отрицание Y

Импликация от Y к Х

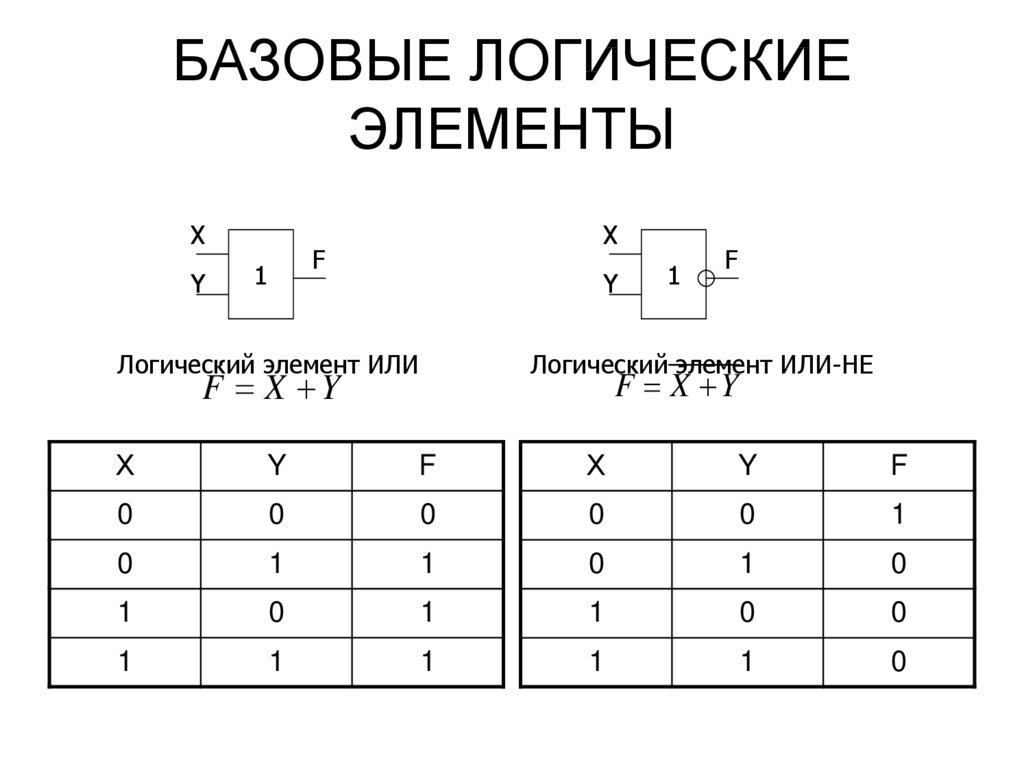

9. БАЗОВЫЕ ЛОГИЧЕСКИЕ ЭЛЕМЕНТЫ

ХY

Х

F

1

Y

Логический элемент ИЛИ

1

F

Логический элемент ИЛИ-НЕ

F X Y

F X Y

Х

Y

F

Х

Y

F

0

0

0

0

0

1

0

1

1

0

1

0

1

0

1

1

0

0

1

1

1

1

1

0

10. БАЗОВЫЕ ЛОГИЧЕСКИЕ ЭЛЕМЕНТЫ

ХХ

Y

&

F

Y

&

F

Логический элемент И-НЕ

Логический элемент И

F X Y

F X Y

Х

Y

F

Х

Y

F

0

0

0

0

0

1

0

1

0

0

1

1

1

0

0

1

0

1

1

1

1

1

1

0

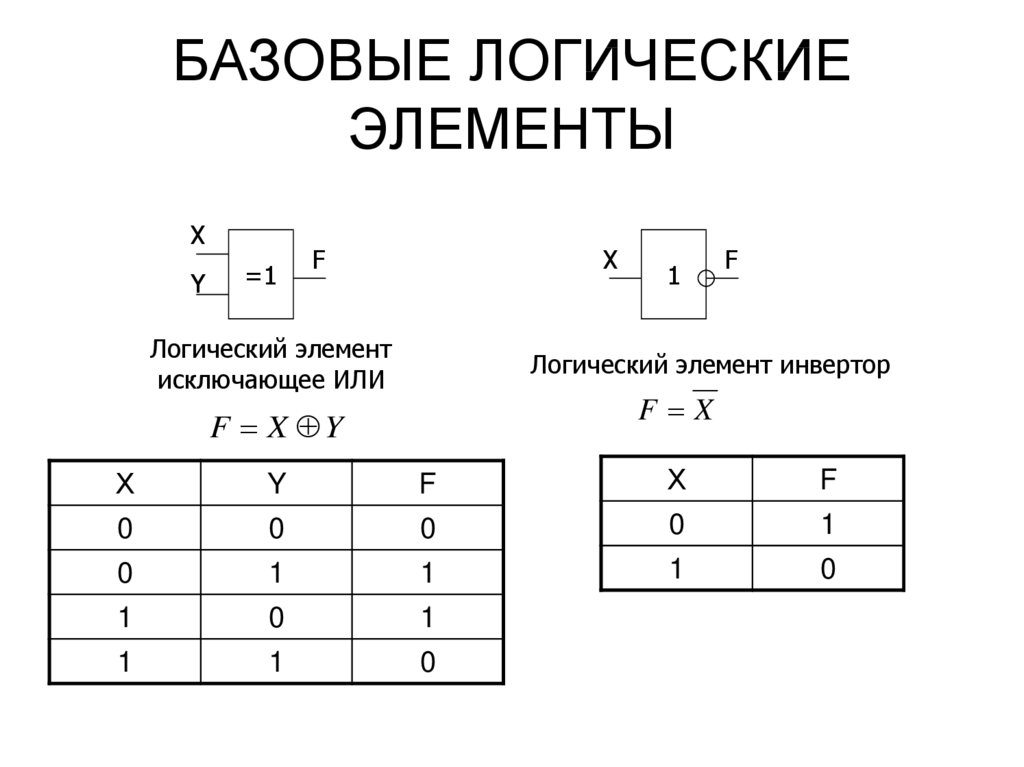

11. БАЗОВЫЕ ЛОГИЧЕСКИЕ ЭЛЕМЕНТЫ

ХY

=1

F

Х

Логический элемент

исключающее ИЛИ

1

F

Логический элемент инвертор

F X

F X Y

Х

Y

F

Х

F

0

0

0

0

1

0

1

1

1

0

1

0

1

1

1

0

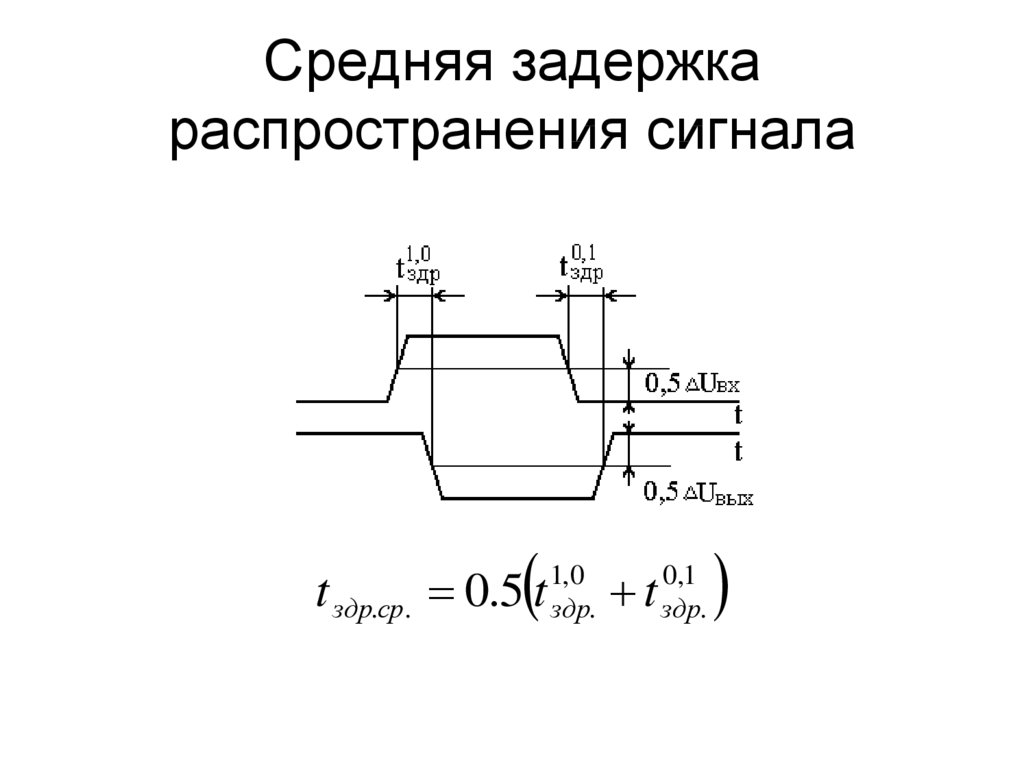

12. Средняя задержка распространения сигнала

t здр.ср. 0.5 t1, 0

здр.

t

0,1

здр.

13. Передаточная характеристика

U выхU1

1

U min

0

U max

U0

U n0

U n1

U вх

14. ЗАКОНЫ АЛГЕБРЫ ЛОГИКИ

Аксиомы операций конъюнкции идизъюнкции:

• 1а) 0 0=0

1б) 1 1=1

• 2а) 1 0=0 1=0

2б) 0 1=1 0=1

• 3а) 1 1=1

3б) 0 0=0

15. ЗАКОНЫ АЛГЕБРЫ ЛОГИКИ

• Переместительный закона) a b=b a

б) a b=b a

• Сочетательный закон

а) a(bc)=(ab)c=abc

б) a (b c)=(a b) c=a b c

• Закон тавтологии

а) a a=a

б) a a=a

16. ЗАКОНЫ АЛГЕБРЫ ЛОГИКИ

Закон обращения: если a=b, то ~a=~b

Закон двойной инверсии: ~~a=a

Закон нулевого множества

а) a 0=0

б) a 0=a

Закон универсального множества

а) a 1=a

б) a 1=1

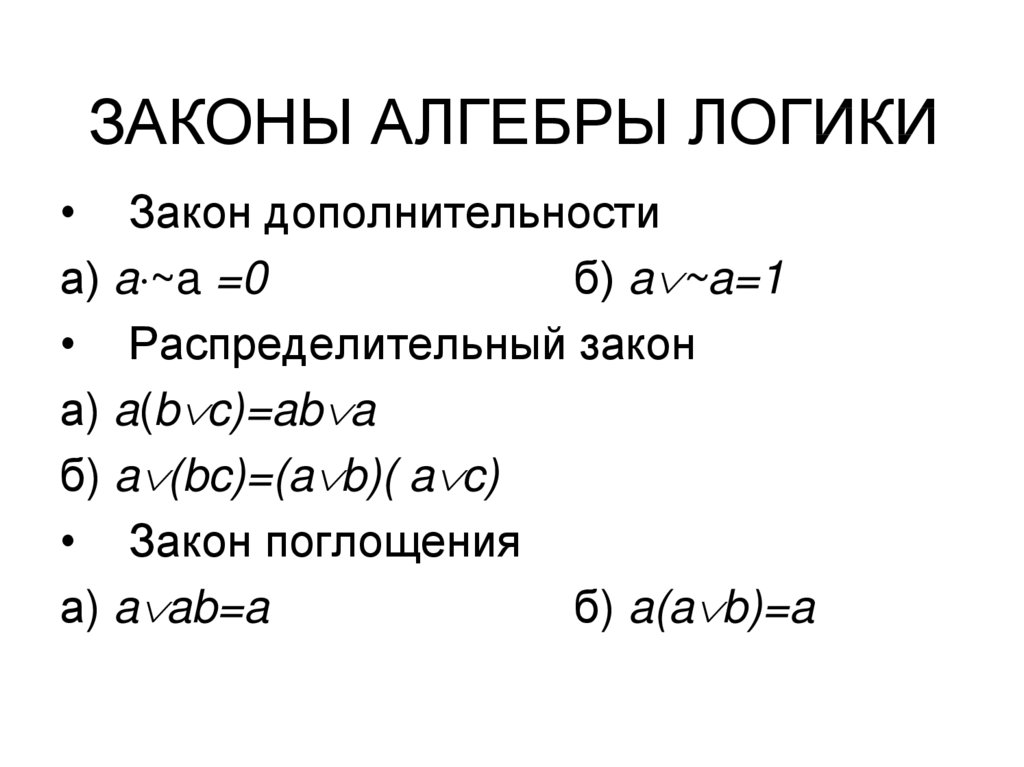

17. ЗАКОНЫ АЛГЕБРЫ ЛОГИКИ

• Закон дополнительностиа) a ~a =0

б) a ~a=1

• Распределительный закон

а) a(b c)=ab a

б) a (bc)=(a b)( a c)

• Закон поглощения

а) a ab=a

б) a(a b)=a

18. ЗАКОНЫ АЛГЕБРЫ ЛОГИКИ

• Закон склеиванияа) (a b)(a ~b)=a

б) a*b a*~b=a

• Закон инверсии (закон Де Моргана)

а) ~(a*b)=~a ~b

б) ~(a b)=~a*~b

• или после инвертирования

в) a*b=~(~a ~b) г) a b=~(~a*~b)

19. Произвольные функции и логические схемы

№Аргументы

Ф-я

a

b

c

y

0

0

0

0

0

1

0

0

1

2

0

1

3

0

1

№

Аргументы

Ф-я

a

b

c

y

4

1

0

0

0

0

5

1

0

1

1

0

0

6

1

1

0

1

1

1

7

1

1

1

1

Y abc abc abc abc

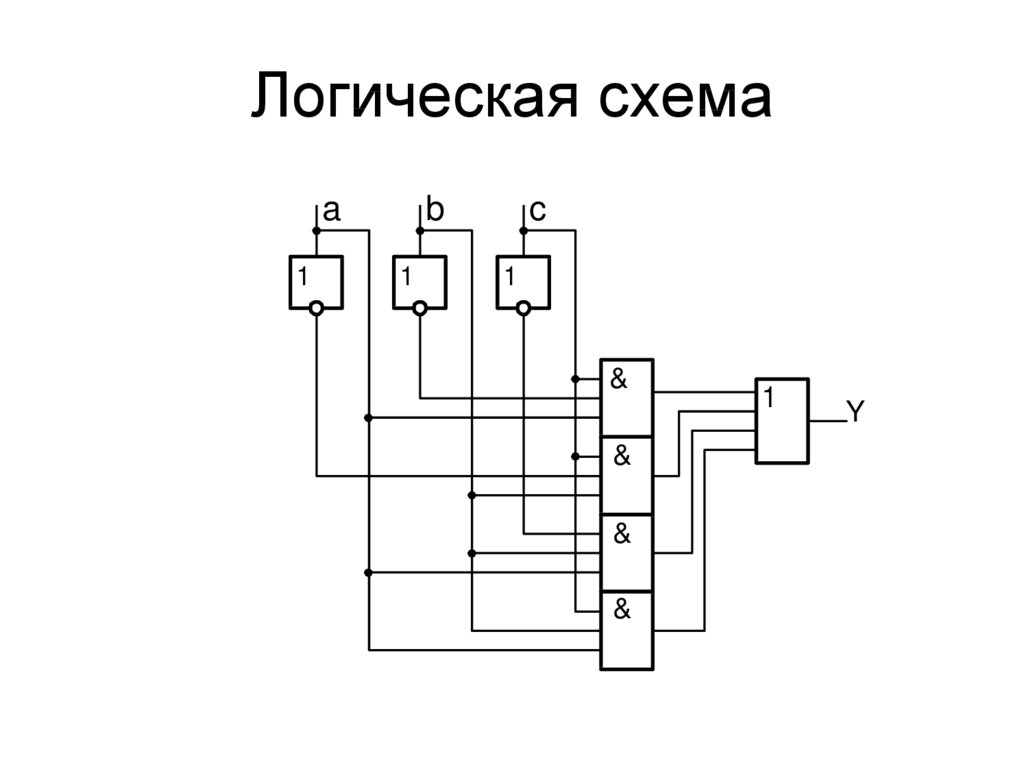

20. Логическая схема

a1

b

1

c

1

&

&

&

&

1

Y

21. Минимизация функций

Y abc abc abc abcY abc abc abc abc abc abc abc

abc abc abc abc abc abc

ас b b bc a a ab c c

ac bc ab

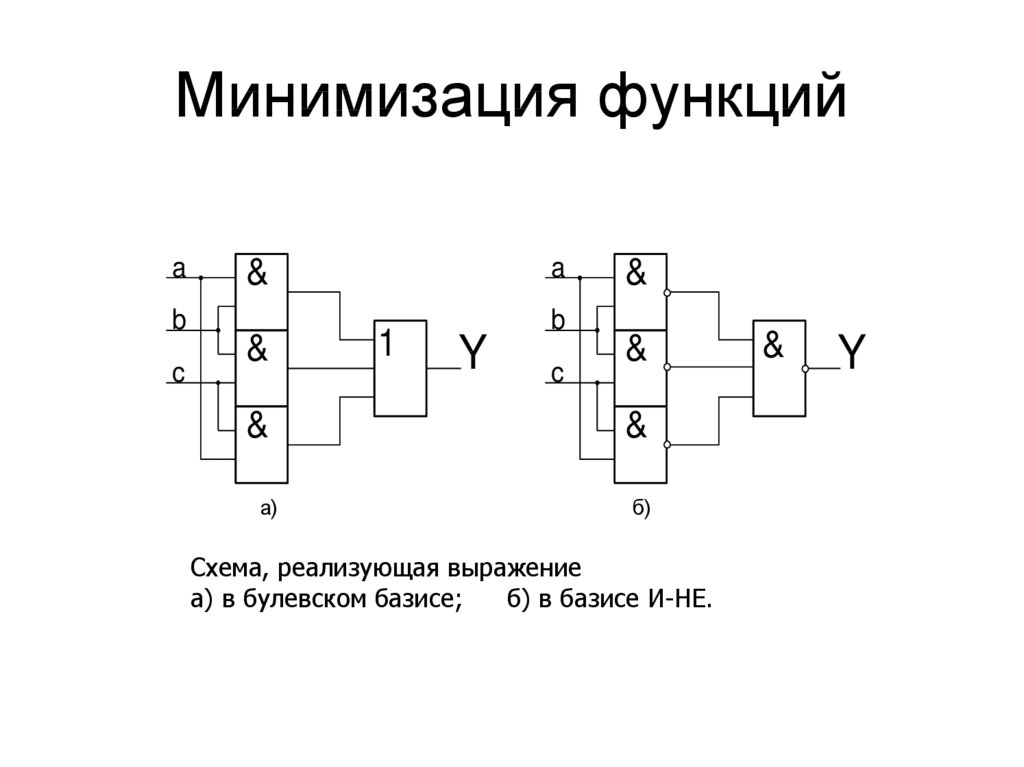

22. Минимизация функций

ab

c

a

&

&

&

а)

1

Y

b

c

&

&

&

б)

Схема, реализующая выражение

а) в булевском базисе;

б) в базисе И-НЕ.

&

Y

23. Минимизация функций (карта Карно)

x20

1

0

f(0,0)

f(0,1)

1

f(1,0)

f(1,1)

x1

Карта Карно для функции

двух переменных

x2,x3

00

01

11

10

0

f(0,0,0)

f(0,0,1)

f(0,1,1)

f(0,1,0)

1

f(1,0,0)

f(1,0,1)

f(1,1,1)

f(1,1,0)

x1

Карта Карно для функции

трех переменных

24. Минимизация функций (карта Карно)

x3,x400

01

11

10

00

f(0,0,0,0)

f(0,0,0,1)

f(0,0,1,1)

f(0,0,1,0)

01

f(0,1,0,0)

f(0,1,0,1)

f(0,1,1,1)

f(0,1,1,0)

11

f(1,1,0,0)

f(1,1,0,1)

f(1,1,1,1)

f(1,1,1,0)

10

f(1,0,0,0)

f(1,0,0,1)

f(1,0,1,1)

f(1,0,1,0)

x1,x2

Карта Карно для функции

четырех переменных

25. Примеры карт Карно

x3,х400

01 1

10

1

x3,х4 0

0

0

1

1

1

1

0

0

0

1

1

1

1

0

00

1

0

0

1

01

0

0

0

0

11

0

0

0

0

1

0

0

1

x3,х4

0

x1,х2

х1,х2

x1,х2

00

0

0

1

0

00

0

1

0

0

01

1

0

0

1

01

0

1

0

1

11

1

0

0

1

11

0

1

0

0

10

0

0

1

0

0

1

0

0

10

а)

10

б)

в)

26. Типовые комбинационные устройства

преобразователи кодов;

коммутаторы;

арифметические устройства;

постоянные запоминающие

устройства (ПЗУ).

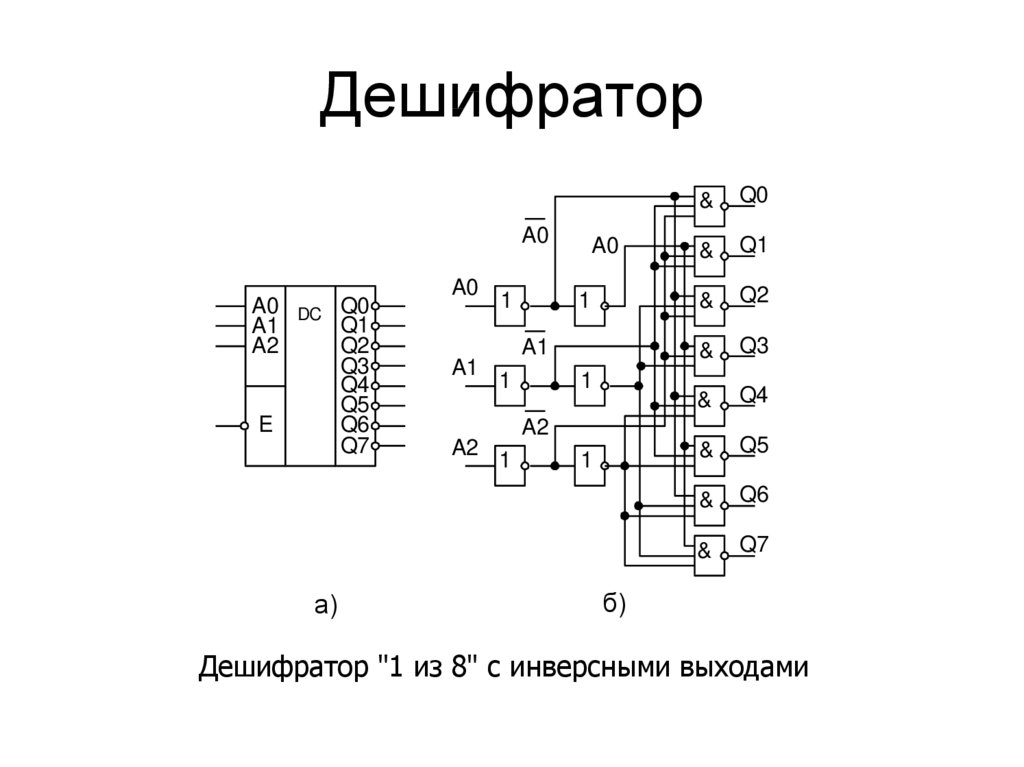

27. Дешифратор

A0A0

A1

A2

DC

E

а)

Q0

Q1

Q2

Q3

Q4

Q5

Q6

Q7

A0

A1

A2

1

A0

1

A1

1

1

&

Q0

&

Q1

&

Q2

&

Q3

&

Q4

&

Q5

&

Q6

&

Q7

A2

1

1

б)

Дешифратор "1 из 8" с инверсными выходами

28. Дешифратор

Е А2 А1 А0Q0

Q1

Q2

Q3

Q4

Q5

Q6

Q7

1

*

*

*

1

1

1

1

1

1

1

1

Q0 A2 * A1* A0

0

0

0

0

0

1

1

1

1

1

1

1

0

0

0

1

1

0

1

1

1

1

1

1

Q1 A2 * A1* A0

0

0

1

0

1

1

0

1

1

1

1

1

Q2 A2 * A1* A0

0

0

1

1

1

1

1

0

1

1

1

1

Q3 A2 * A1* A0

0

1

0

0

1

1

1

1

0

1

1

1

Q4 A2 * A1* A0

0

1

0

1

1

1

1

1

1

0

1

1

0

1

1

0

1

1

1

1

1

1

0

1

0

1

1

1

1

1

1

1

1

1

1

0

Q5 A2 * A1* A0

Q6 A2 * A1* A0

Q7 A2 * A1* A0

29. Каскадное соединение дешифраторов

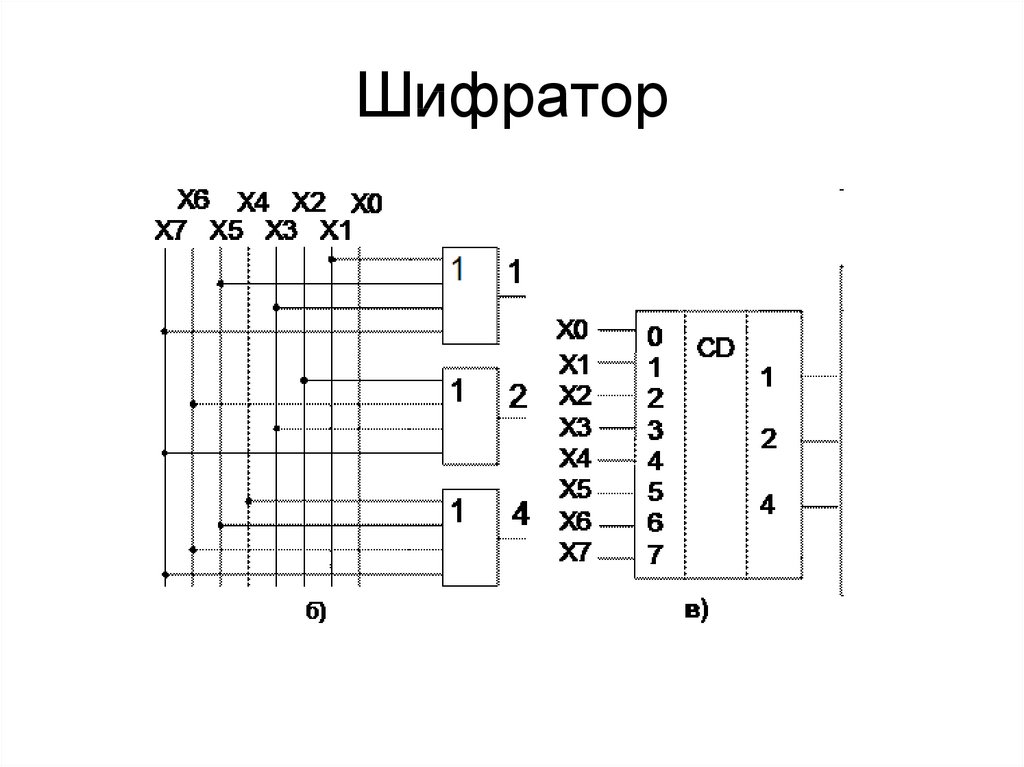

30. Шифратор

31. Шифратор

X0X1

X2

X3

X4

X5

X6

X7

1

0

0

0

0

0

0

0

0

0

0

0

1

0

0

0

0

0

0

0

0

1

0

0

1

0

0

0

0

0

0

1

0

0

0

0

1

0

0

0

0

0

1

1

0

0

0

0

1

0

0

0

1

0

0

0

0

0

0

0

1

0

0

1

0

1

0

0

0

0

0

0

1

0

1

1

0

0

0

0

0

0

0

0

1

1

1

1

Y0 X 4 X5 X 6 X 7

Y1 X 2 X 3 X 6 X 7

Y 2 X1 X 3 X 5 X 7

Y0(4) Y1(2)

Y2(1)

32. Приоритетный шифратор

X0X1

X2

X3

X4

X5

X6

X7

Y0(

4)

Y1(

2)

Y2(1

)

0

1

1

1

1

1

1

1

1

1

1

Ф

0

1

1

1

1

1

1

1

1

0

Ф

Ф

0

1

1

1

1

1

1

0

1

Ф

Ф

Ф

0

1

1

1

1

1

0

0

Ф

Ф

Ф

Ф

0

1

1

1

0

1

1

Ф

Ф

Ф

Ф

Ф

0

1

1

0

1

0

Ф

Ф

Ф

Ф

Ф

Ф

0

1

0

0

1

Ф

Ф

Ф

Ф

Ф

Ф

Ф

0

0

0

0

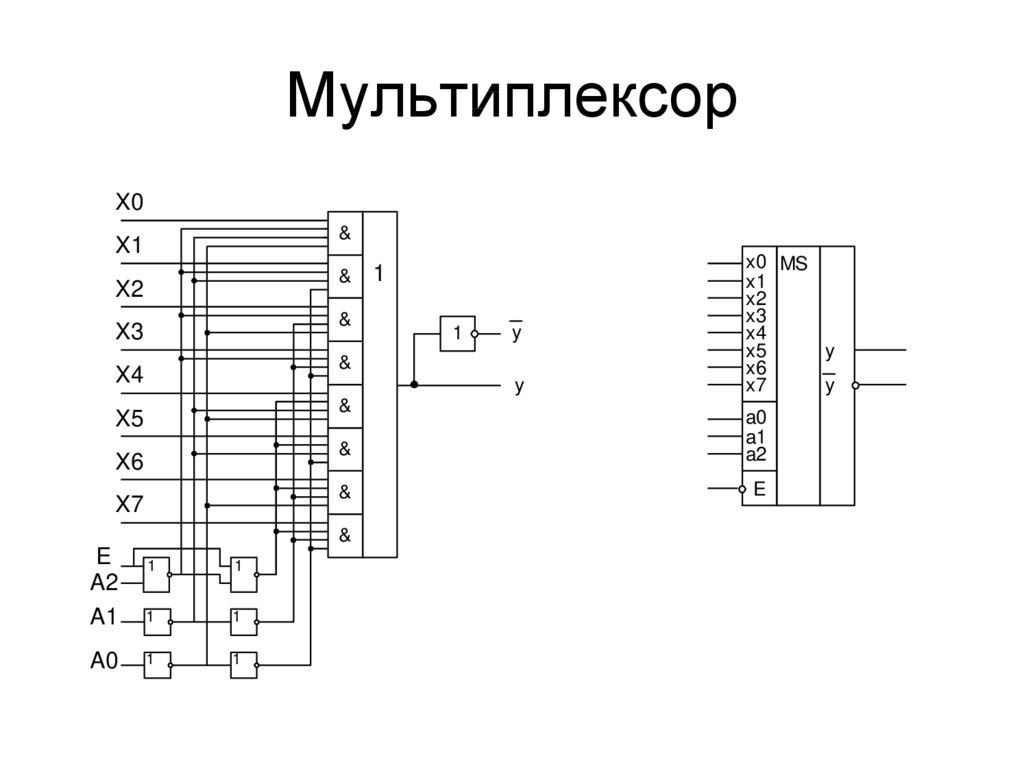

33. Мультиплексор

X0&

X1

&

X2

&

X3

1

1

y

&

X4

y

&

X5

X6

X7

&

a0

a1

a2

&

E

&

E

A2

A1

1

1

1

1

A0

1

1

x0 MS

x1

x2

x3

x4

x5

y

x6

x7

y

34. Мультиплексор

ЕА2

А1

А0

Y

1

*

*

*

0

Y E A2 A1 A0 X 0

0

0

0

0

X0

A2 A1 A0 X 1

0

0

0

1

X1

A2 A1 A0 X 2

0

0

1

0

X2

A2 A1 A0 X 3

0

0

1

1

X3

0

1

0

0

X4

A2 A1 A0 X 4

0

1

0

1

X5

0

1

1

0

X6

0

1

1

1

X7

A2 A1 A0 X 5

A2 A1 A0 X 6

A2 A1 A0 X 7

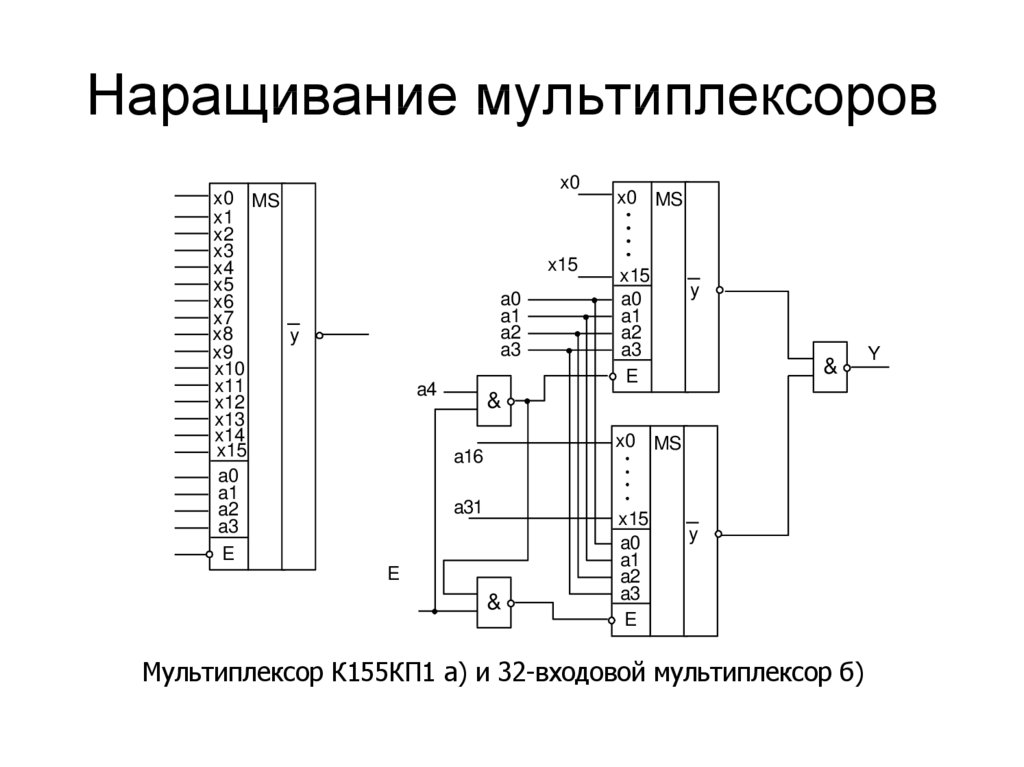

35. Наращивание мультиплексоров

x0x0 MS

x1

x2

x3

x4

x5

x6

x7

x8

y

x9

x10

x11

x12

x13

x14

x15

a0

a1

a2

a3

E

x15

a0

a1

a2

a3

a4

x0 MS

x15

a0

a1

a2

a3

E

y

&

&

x0 MS

a16

a31

E

&

x15

a0

a1

a2

a3

E

y

Мультиплексор К155КП1 а) и 32-входовой мультиплексор б)

Y

36. АРИФМЕТИЧЕСКИЕ УСТРОЙСТВА

ПОЛУСУММАТОРA

HS

B

S

A

P

B

SM

S1

P1

P0

а)

б)

A

S

P

0

0

0

0

0

1

1

0

1

0

1

0

1

1

0

1

В

S A B,

P AB

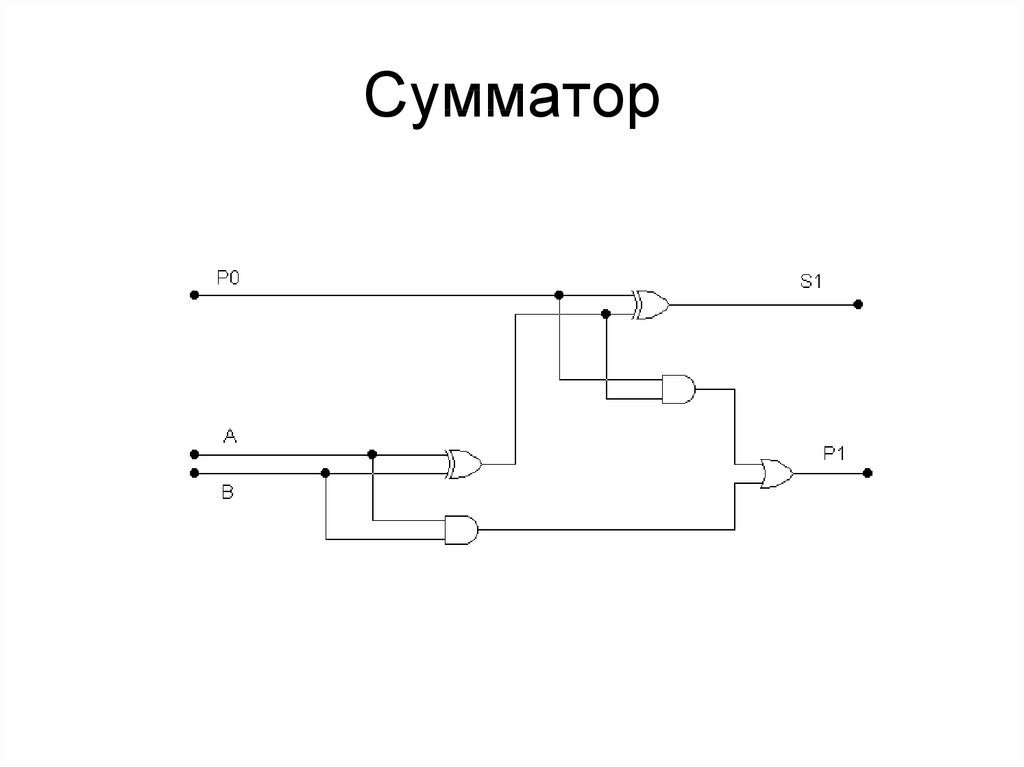

37. Сумматор

ВA

S1

P1

0

0

0

0

0

S1

0

0

1

1

0

P1

0

1

0

1

0

0

1

1

0

1

1

0

0

1

0

1

0

1

0

1

1

1

0

0

1

1

1

1

1

1

Р0

A

SM

B

P0

б)

38. Сумматор

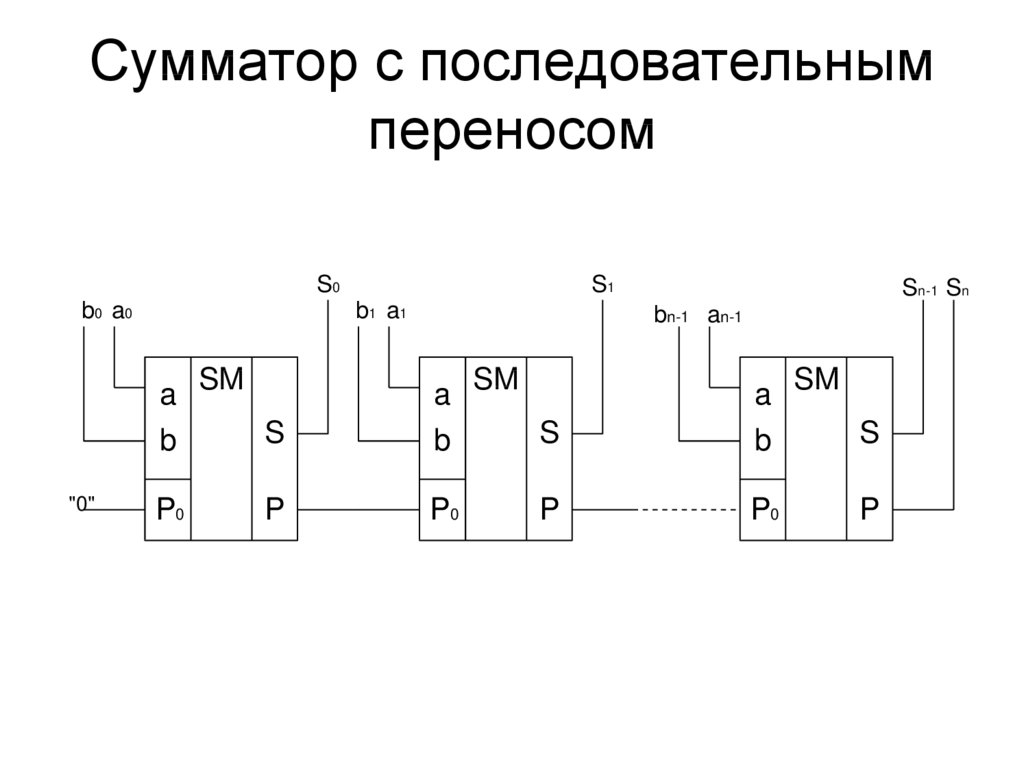

39. Сумматор с последовательным переносом

S0b0 a0

b1 a1

a SM

"0"

S1

Sn-1 Sn

bn-1 an-1

a SM

a SM

b

S

b

S

b

S

P0

P

P0

P

P0

P

40. Цифровой компаратор

77

7

i 0

i 0

i 0

(аi bi) (ai bi) (ai bi)

A0

B0

==

==

A7

B7

&

B0

A=B

A1

B1

A0

==

A3

B3

A4

B4

A7

К555СП1

A0

A1 COMP

M2

A2

A3

B0

B1 M2

B2

B3

>

<

= M2

1

>

<

=

&

1

A=B

41. Контроль четности

К примеру, в числе 0111 числоединиц нечетно.

00111 - нечетный паритет;

10111 - четный паритет.

42. Контроль четности

УсловноеК155ИП2.

изображение

микросхемы

43. Асинхронный RS-триггер

SQtt 1

R

Режим работы

R

S

0

0

0

1

1

Установка «1»

1

0

0

Установка «0»

1

1

Запрещенное

состояние

Хранение

Qt 1 RS RQt R S Qt .

44. Асинхронный RS-триггер с инверсными входами

Режим работыR

S

1

1

1

0

1

Установка «1»

0

1

0

Установка «0»

0

0

Запрещенное

состояние

Qt

Хранение

45. Синхронный RS-триггер

SQ

S

C

C

R

Q

R

С

R

S

Режим работы

0

х

х

Хранение

1

0

0

Хранение

1

0

1

1

Установка «1»

1

1

0

0

Установка «0»

1

1

1

Запрещенное состояние

46. JK-триггер

Qt 1 J t Qt Qt K t .R

S

C

J

K

0

0

-

Запрещенное состояние

0

1

0

Асинхронная

«0»

установка

1

0

1

Асинхронная

«1»

установка

1

1

0

Хранение

1

1

1

0

0

Хранение

1

1

1

0

1

0

Установка «0»

1

1

1

1

0

1

Установка «1»

1

1

1

1

1

Режим работы

Переключение

(противоположное

состояние)

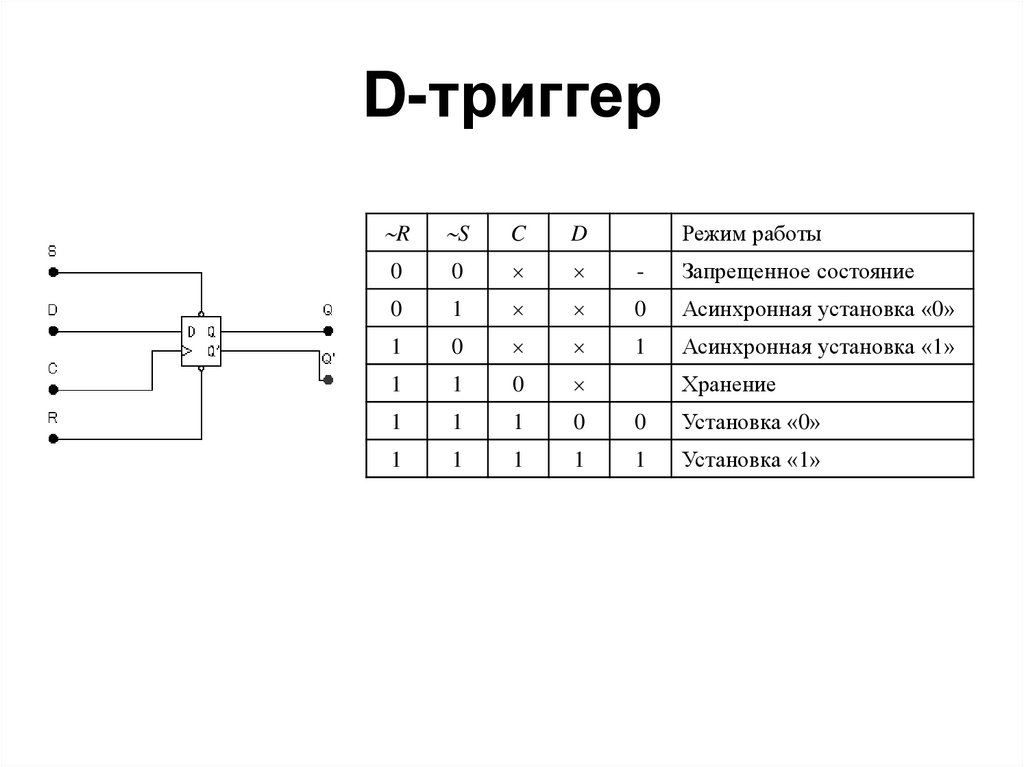

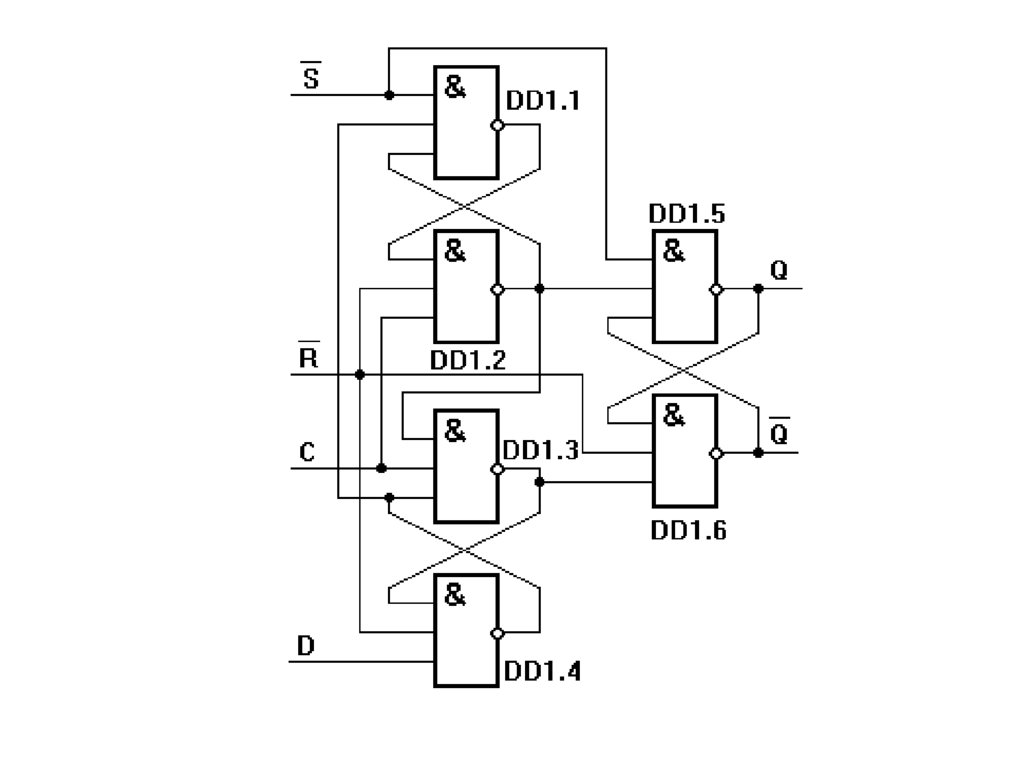

47. D-триггер

RS

C

D

0

0

-

Запрещенное состояние

0

1

0

Асинхронная установка «0»

1

0

1

Асинхронная установка «1»

1

1

0

1

1

1

0

0

Установка «0»

1

1

1

1

1

Установка «1»

Режим работы

Хранение

48.

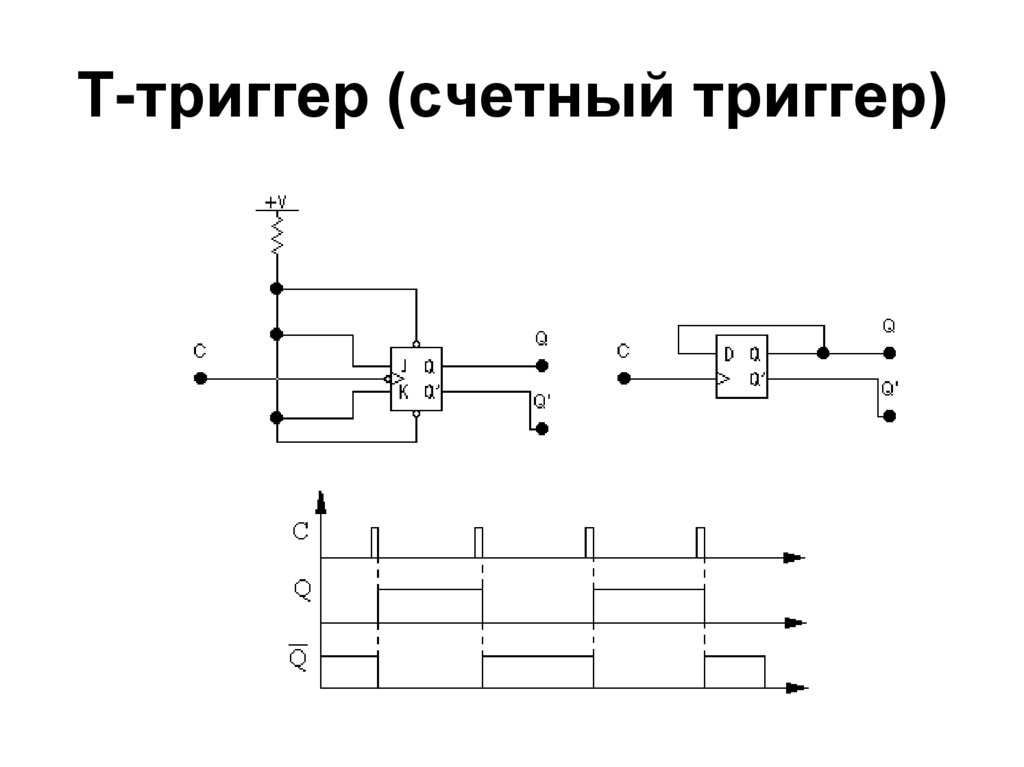

49. Т-триггер (счетный триггер)

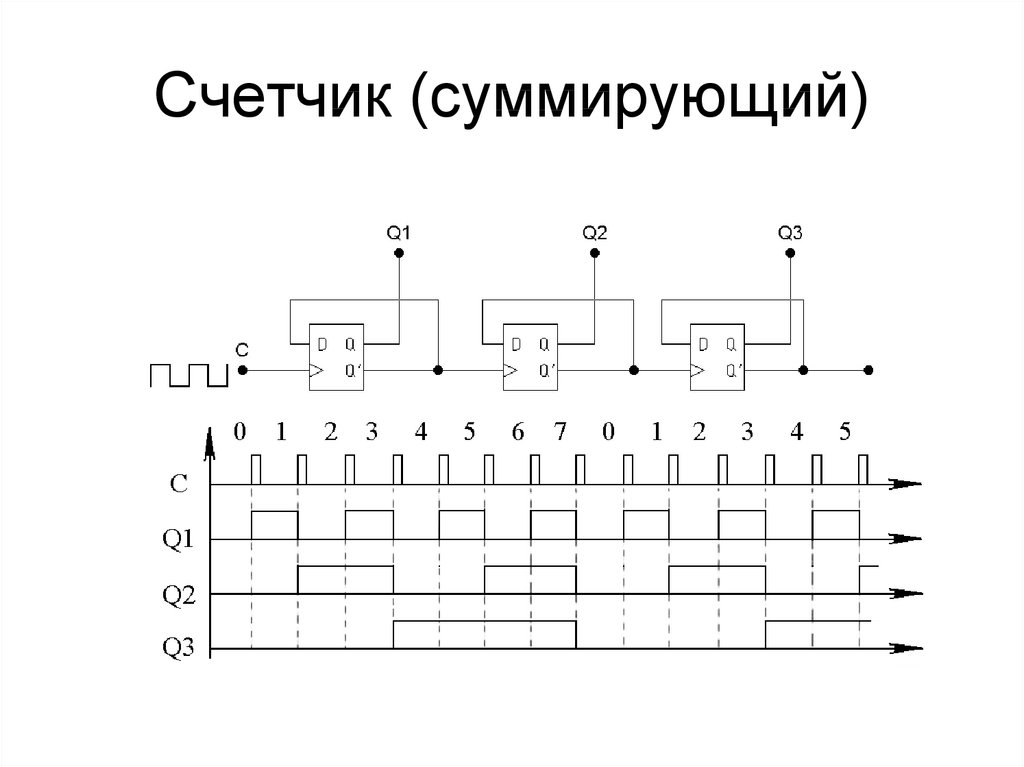

50. Счетчик (суммирующий)

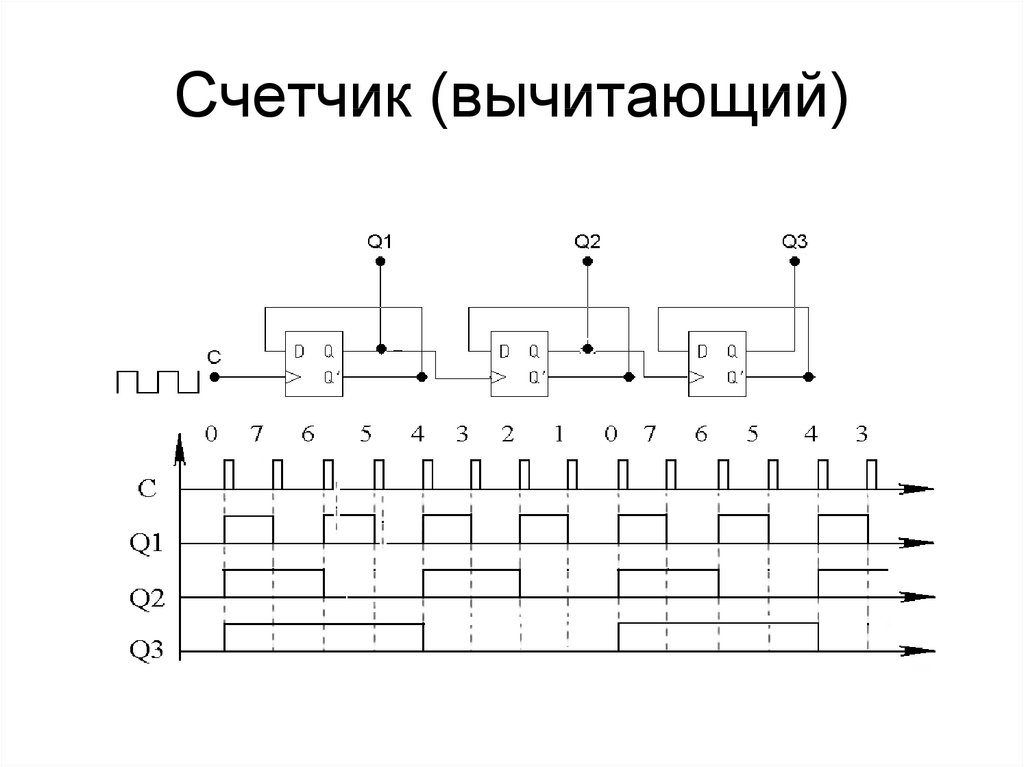

51. Счетчик (вычитающий)

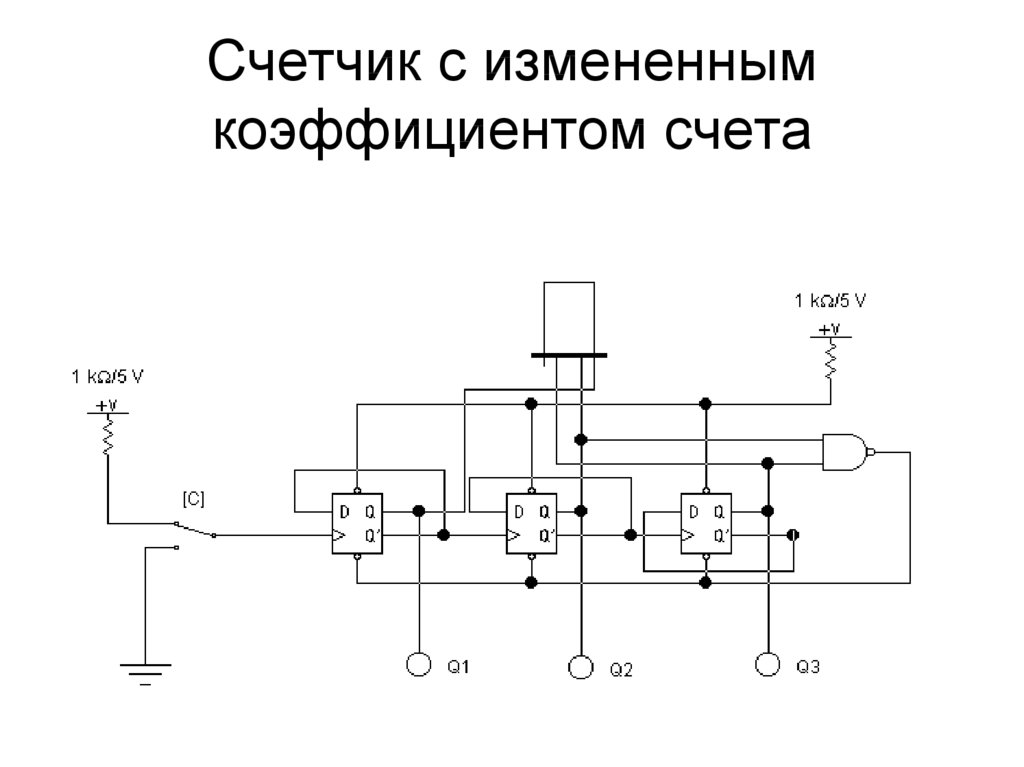

52. Счетчик с измененным коэффициентом счета

53. Реверсивный счетчик

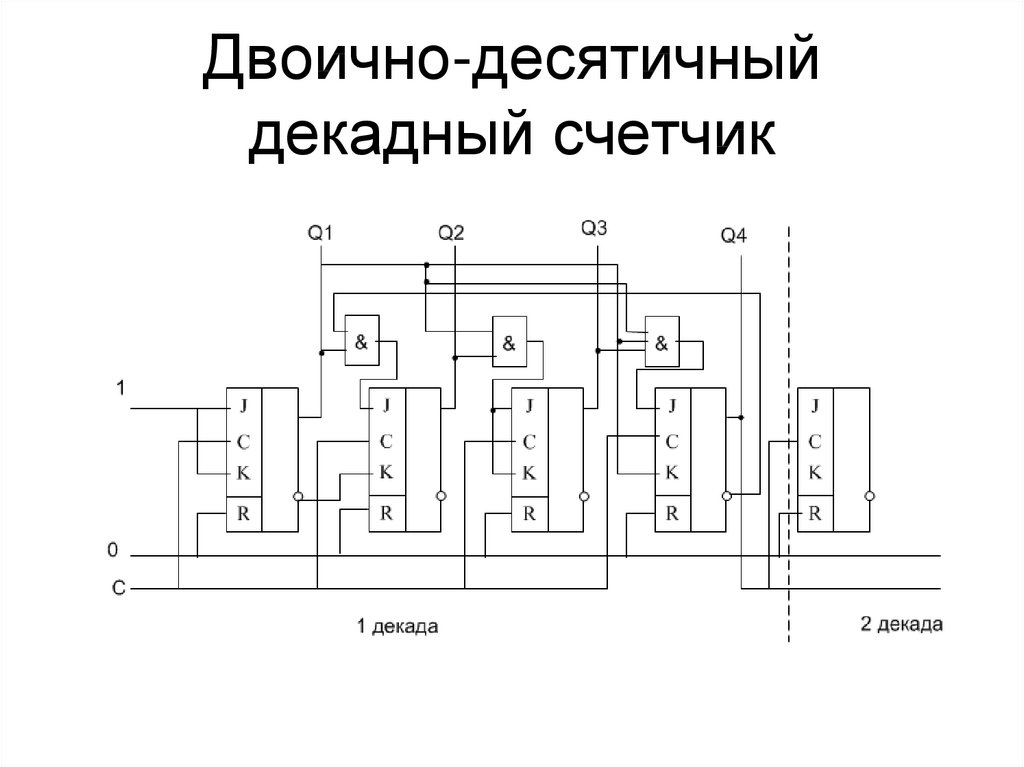

54. Двоично-десятичный декадный счетчик

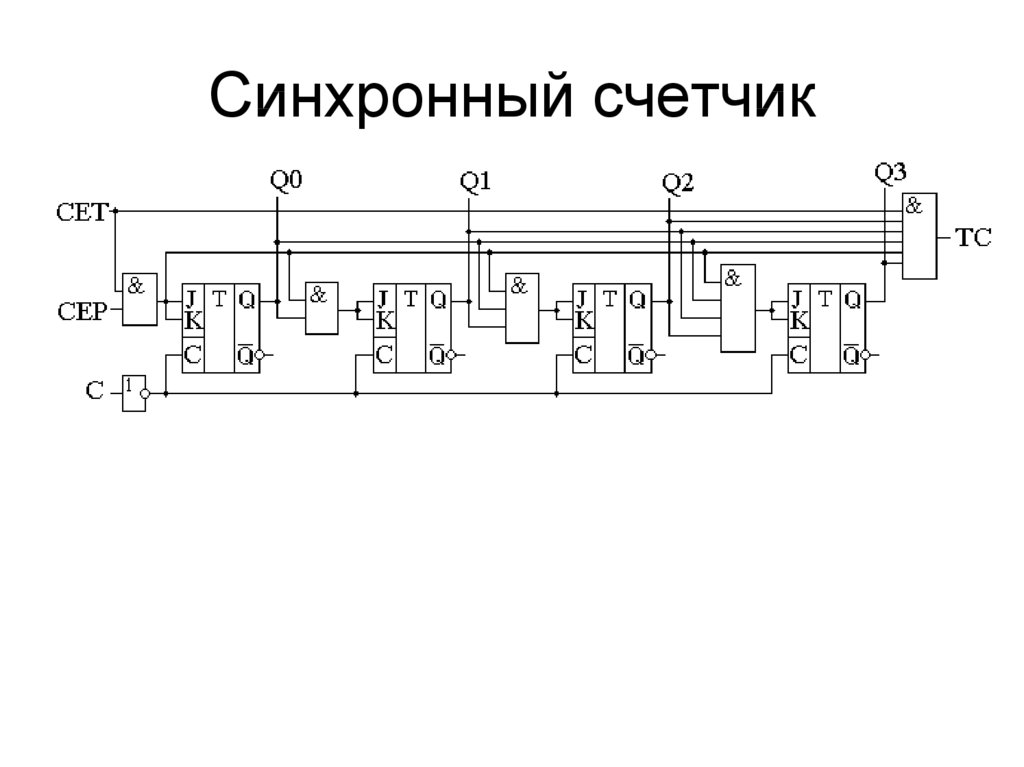

55. Синхронный счетчик

56.

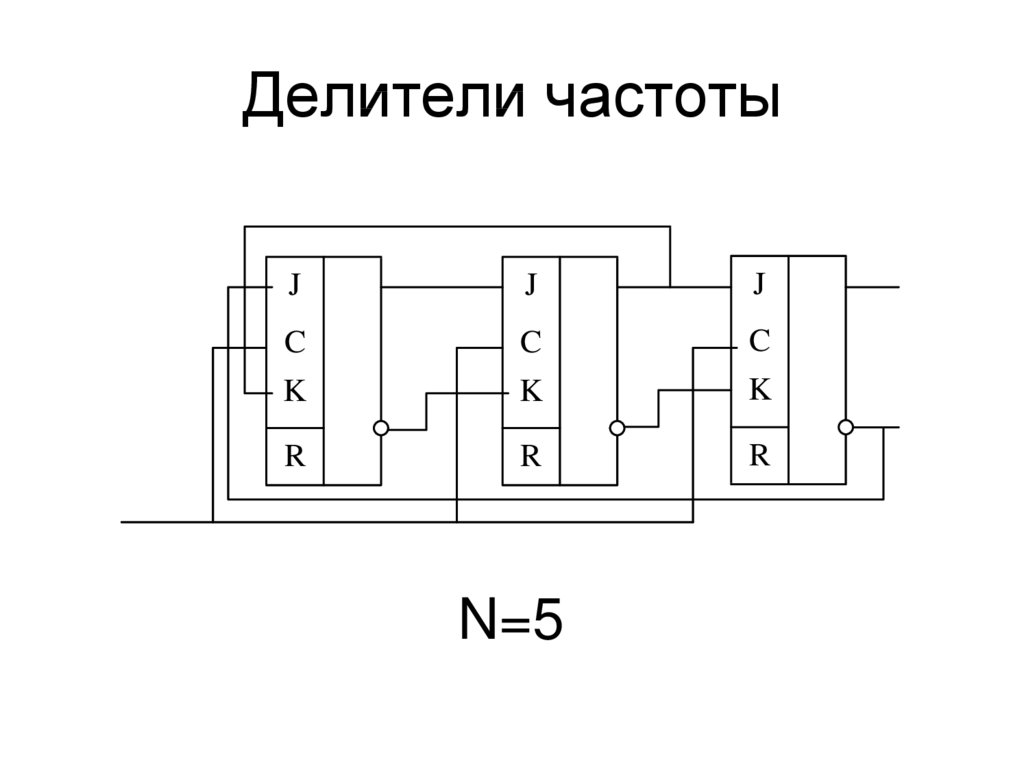

К1533ИЕ1057. Делители частоты

JJ

J

C

C

C

K

K

K

R

R

R

N=5

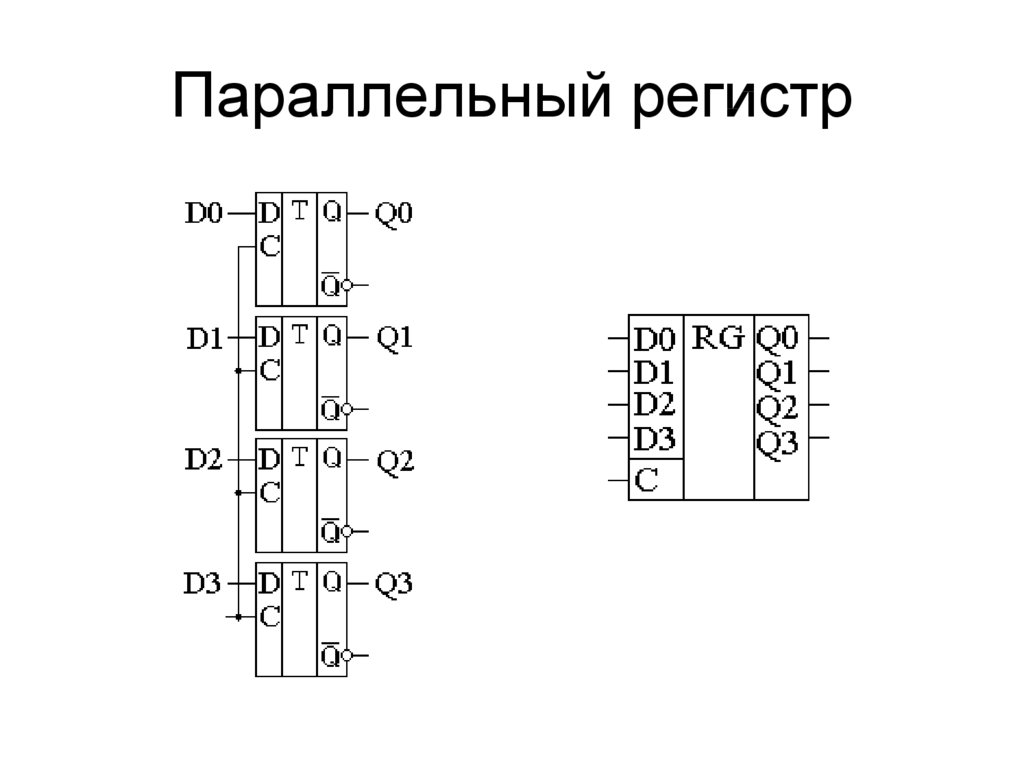

58. Параллельный регистр

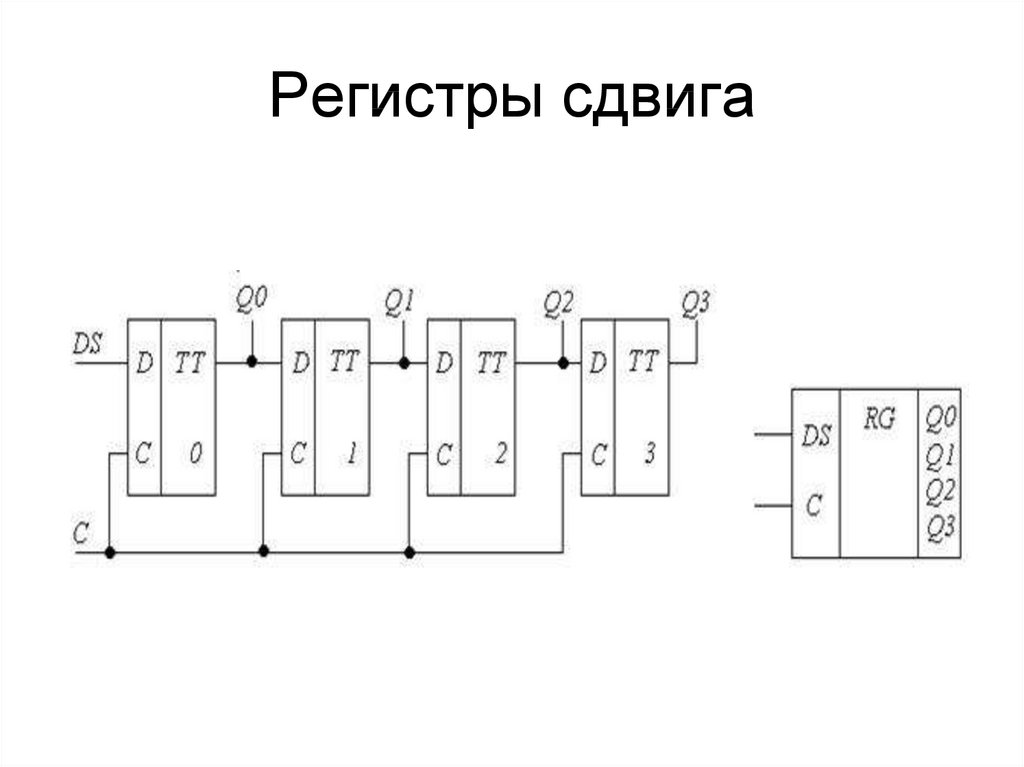

59. Регистры сдвига

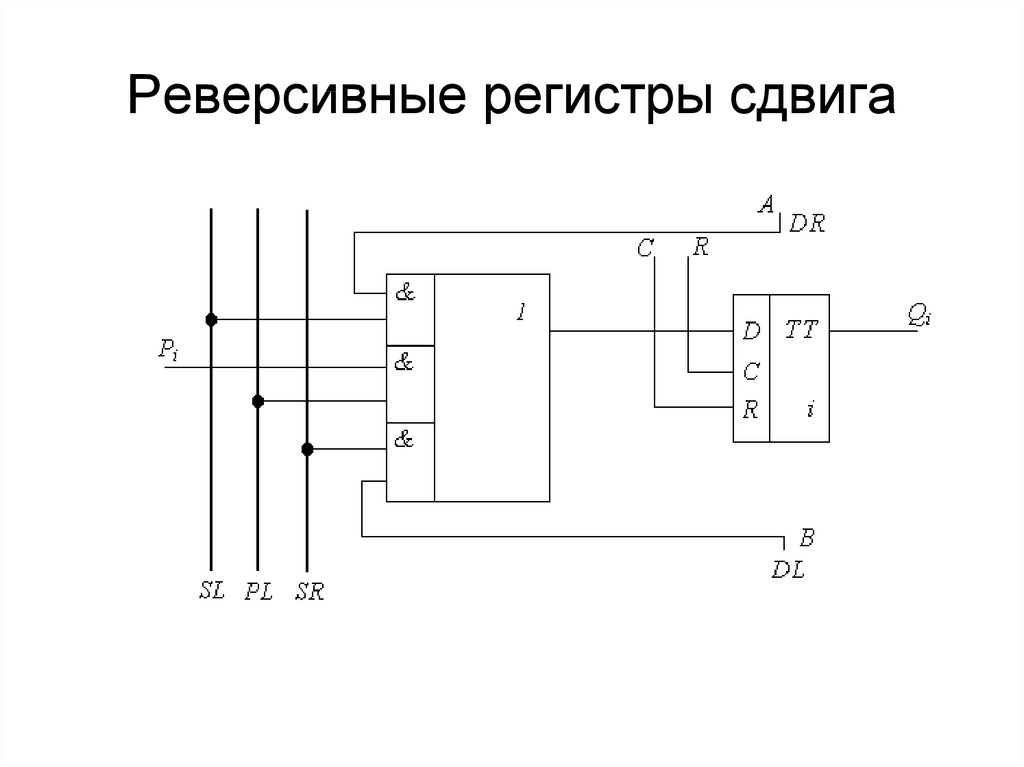

60. Реверсивные регистры сдвига

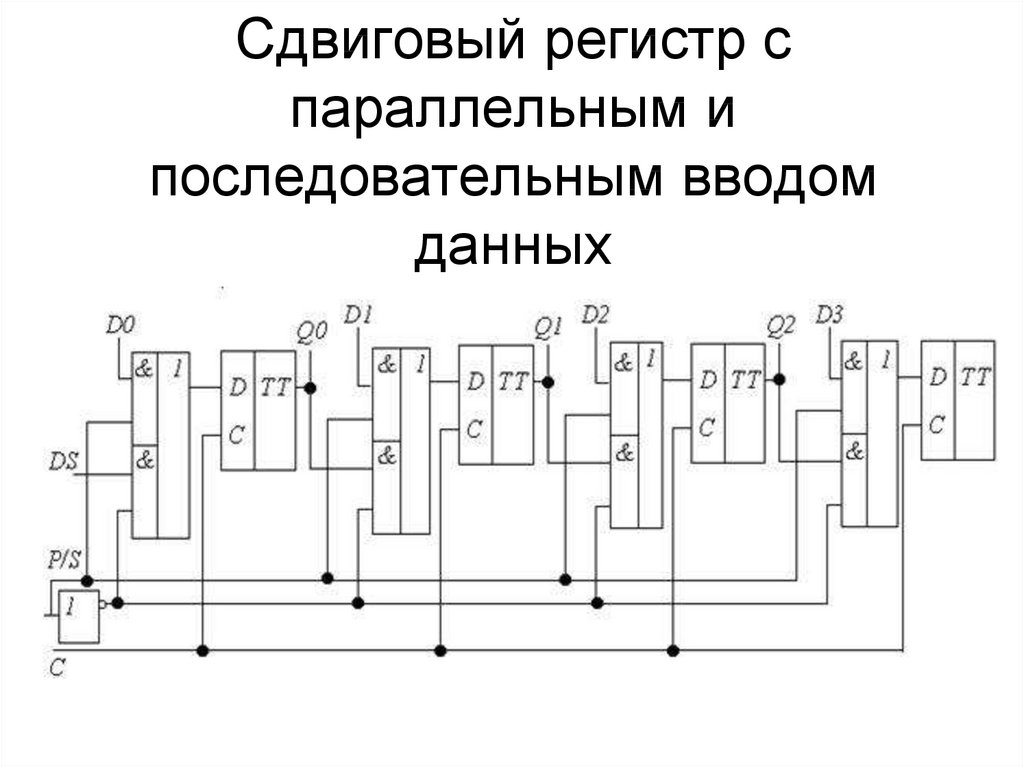

61. Сдвиговый регистр с параллельным и последовательным вводом данных

62. Типы ОЗУ

1. Динамическая память (DRAM) – энергозависимая полупроводниковаяпамять с произвольным доступом, в которой каждый разряд хранится в

конденсаторе, требующем постоянной регенерации для сохранения

информации.

2. Статическая память (SRAM) – энергозависимая полупроводниковая

память с произвольным доступом, в которой каждый разряд хранится в

триггере, позволяющем поддерживать состояние разряда без постоянной

перезаписи.

3. Магниторезистивная оперативная память (MRAM) – это

энергонезависимое запоминающее устройство с произвольным доступом,

сохраняющее информацию при помощи магнитных моментов, а именно,

направления намагниченности ферромагнитного слоя ячейки памяти.

63. Перспективные разработки ОЗУ

- FRAM (Ferroelectric Random Access Memory) – сегнетоэлектрическаяпамять, основывающаяся на сегнетоэлектриках – диэлектриках, способных

менять дипольный момент под действием температуры и внешнего

электрического поля;

- PCM (Phase Change Memory) – память, основанная на изменении

фазового состояния вещества (Халькогенида) с кристаллического на

аморфный и обратно;

- PMC (Programmable Metallization Cell) – память на базе программируемой

металлизации ячейки, основанной на изменении положения атомов под

действием электрического заряда;

- RRAM (Resistive Random-Access Memory) – резистивная память,

построенная на основе элементов, способных изменять свое

сопротивление, в зависимости от величины пропущенного через них тока;

64. Устройство ячейки статической памяти

65.

66. Достоинства и недостатки статической памяти

Достоинства:высокая скорость работы;

нет необходимости регенерации ячеек.

Недостатки:

высокая цена;

низкая плотность упаковки;

небольшой объем;

высокое энергопотребление.

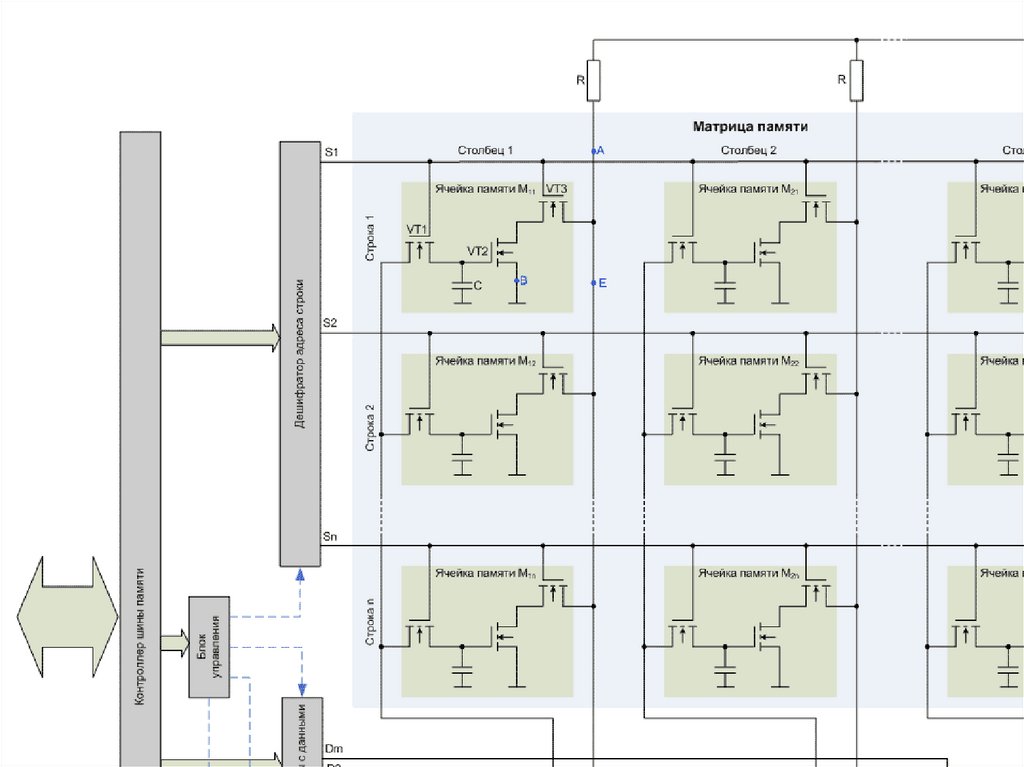

67. Устройство динамической оперативной памяти (DRAM – Dynamic Random Access Memory)

68.

69. Условно-графические обозначения запоминающих устройств с различной организацией: а - 1К*8 разрядов; б - 8К*8 разрядов

70.

71. Достоинства и недостатки динамической памяти

Преимущества динамической памяти:низкая себестоимость;

высокая степень упаковки, позволяющая создавать чипы памяти большого

объема.

Недостатки динамической памяти:

относительно невысокое быстродействие, так как процесс зарядки и

разрядки конденсатора, пусть и микроскопического, занимает гораздо

больше времени, чем переключение триггера;

высокая латентность, в основном, из-за внутренней шины данных, в

несколько раз более широкой, чем внешняя, и необходимости

использования мультиплексора/демультиплексора;

необходимость регенерации заряда конденсатора, из-за его быстрого

саморазряда, ввиду микроскопических размеров.

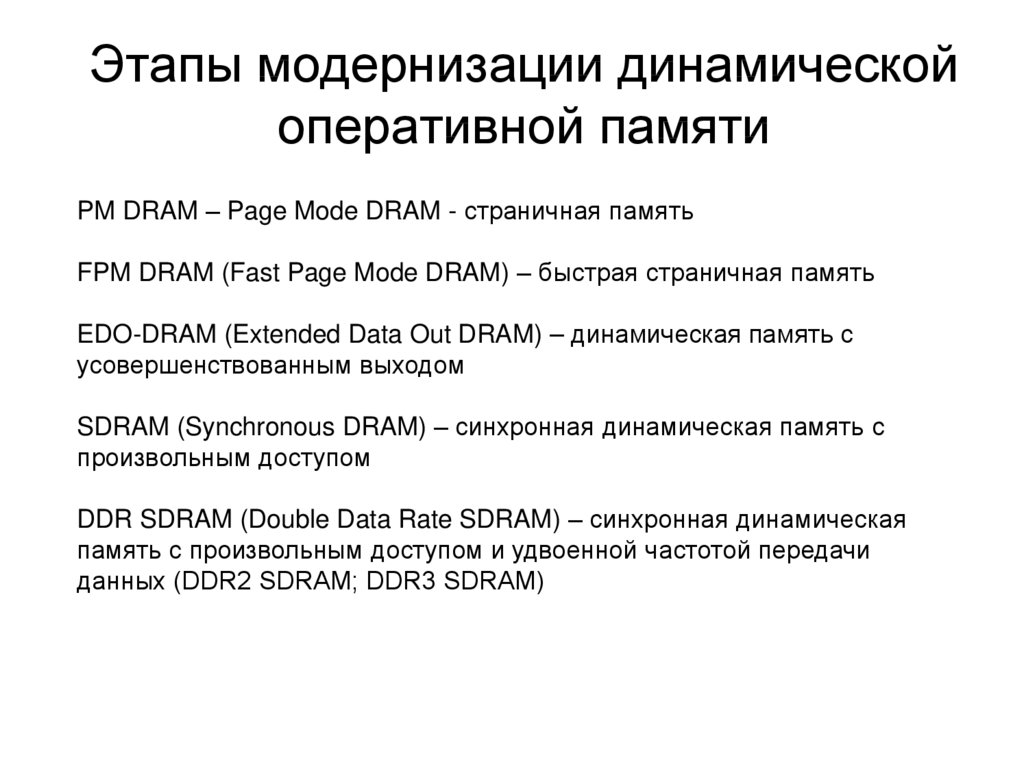

72. Этапы модернизации динамической оперативной памяти

PM DRAM – Page Mode DRAM - страничная памятьFPM DRAM (Fast Page Mode DRAM) – быстрая страничная память

EDO-DRAM (Extended Data Out DRAM) – динамическая память с

усовершенствованным выходом

SDRAM (Synchronous DRAM) – синхронная динамическая память с

произвольным доступом

DDR SDRAM (Double Data Rate SDRAM) – синхронная динамическая

память с произвольным доступом и удвоенной частотой передачи

данных (DDR2 SDRAM; DDR3 SDRAM)

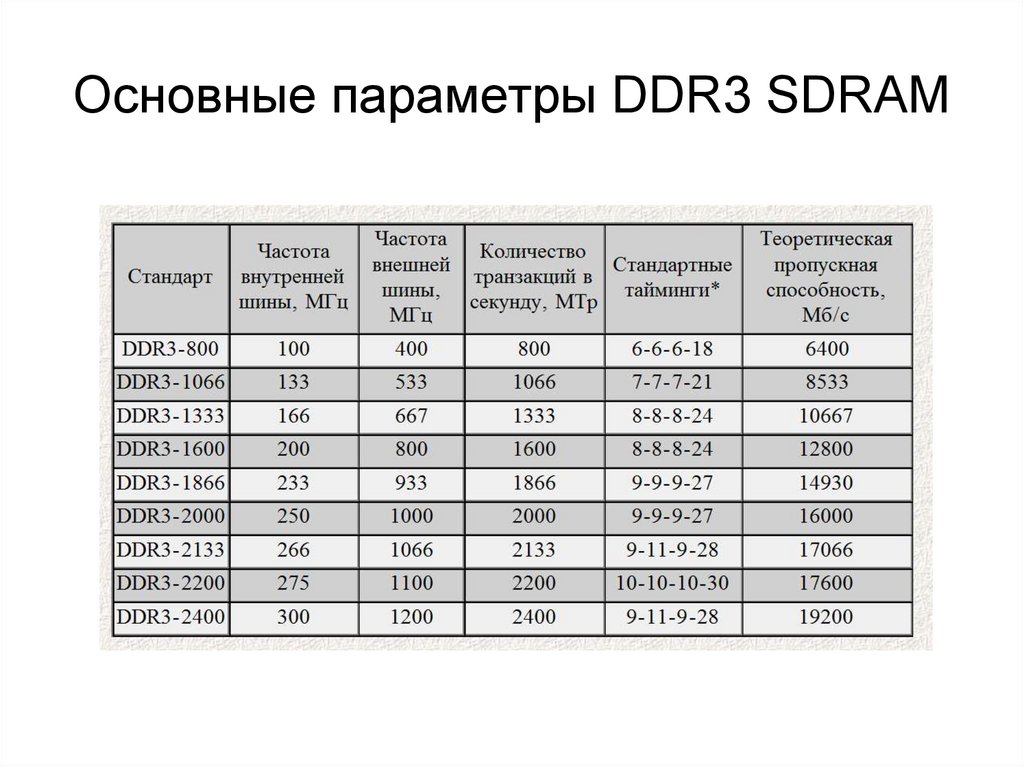

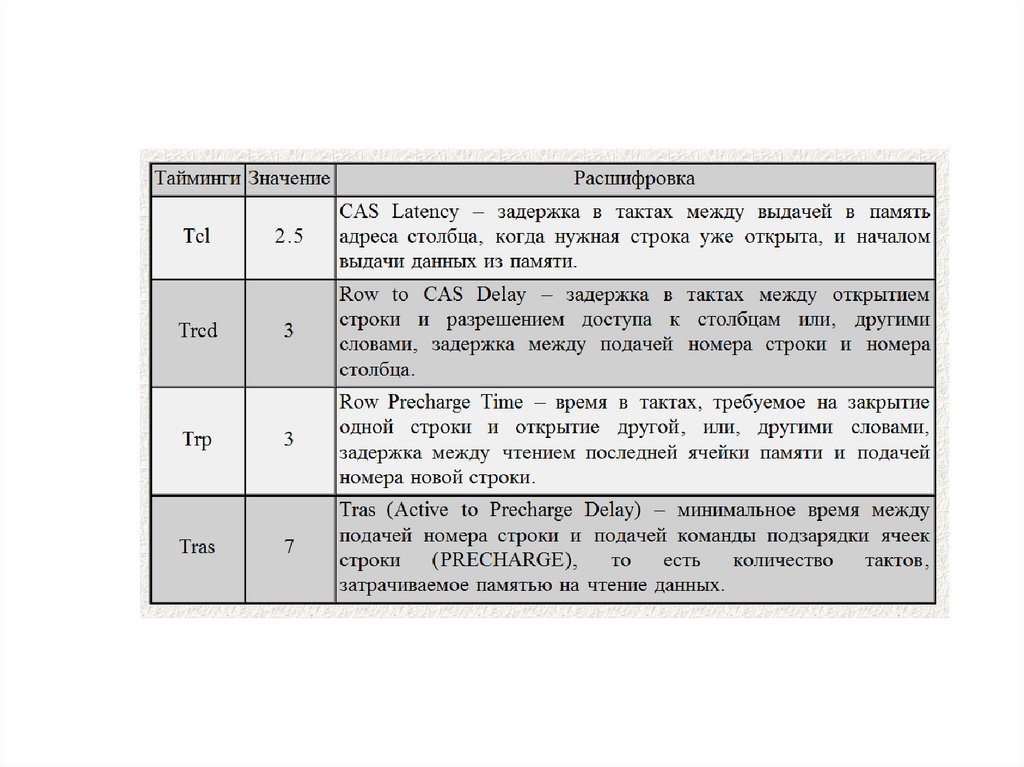

73. Основные параметры DDR3 SDRAM

74.

75. Магниторезистивная оперативная память

76.

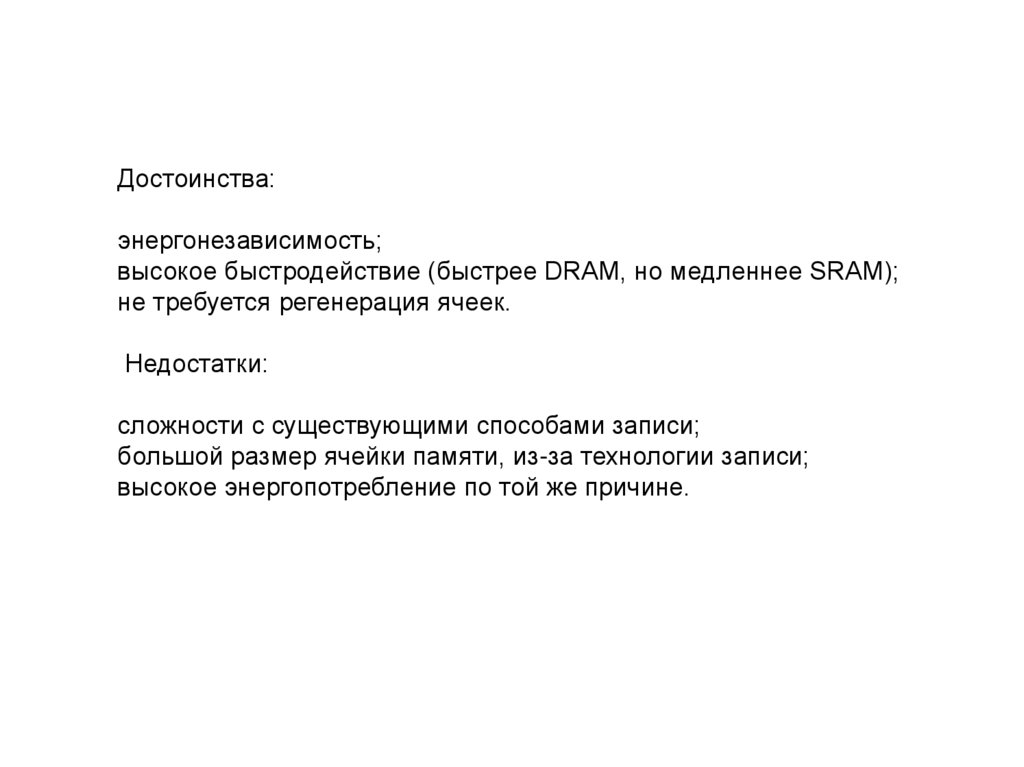

Достоинства:энергонезависимость;

высокое быстродействие (быстрее DRAM, но медленнее SRAM);

не требуется регенерация ячеек.

Недостатки:

сложности с существующими способами записи;

большой размер ячейки памяти, из-за технологии записи;

высокое энергопотребление по той же причине.

Информатика

Информатика