Похожие презентации:

Логические элементы

1. Вычислительная техника и информационные технологии

МикушинАлександр

Владимирович

2. тема 1 ЛОГИЧЕСКИЕ ЭЛЕМЕНТЫ

ИнверторЛогический

элемент «И»

Логический элемент «ИЛИ»

Вычислительная Техника и Информационные Технологии http://digital.sibsutis.ru/contCU.htm

2

19.09.2018

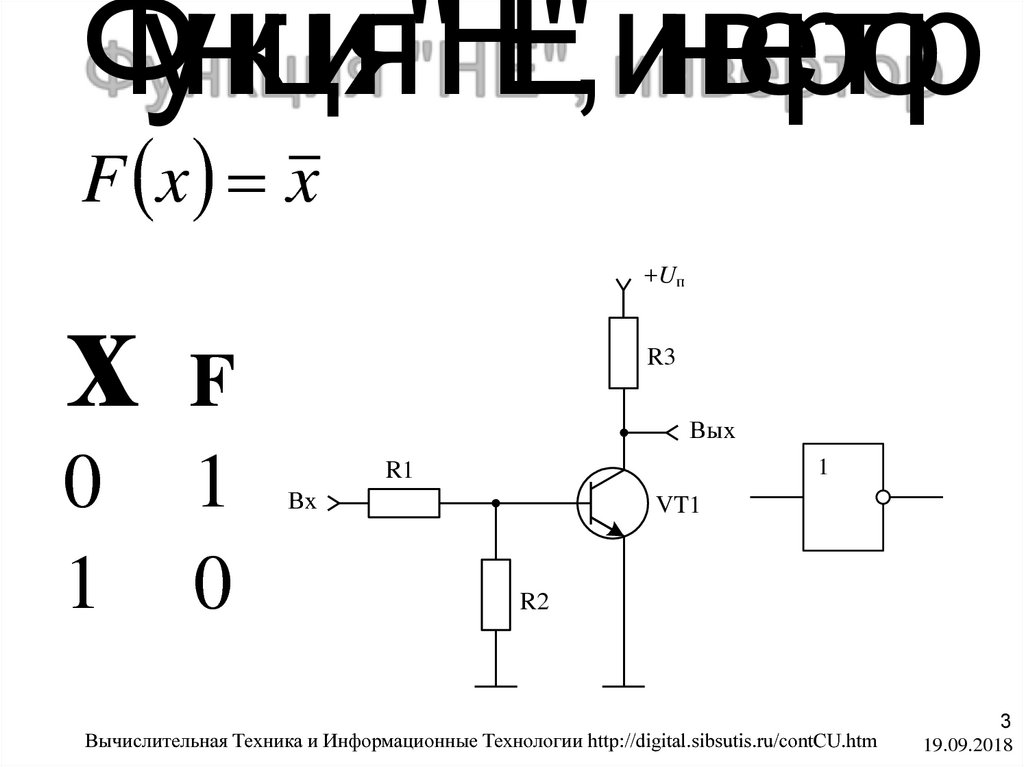

3. Функция "НЕ", инвертор

Функция "НЕ", инверторF x x

+Uп

х

0

1

F

1

0

R3

Вых

1

R1

Вх

VT1

R2

Вычислительная Техника и Информационные Технологии http://digital.sibsutis.ru/contCU.htm

3

19.09.2018

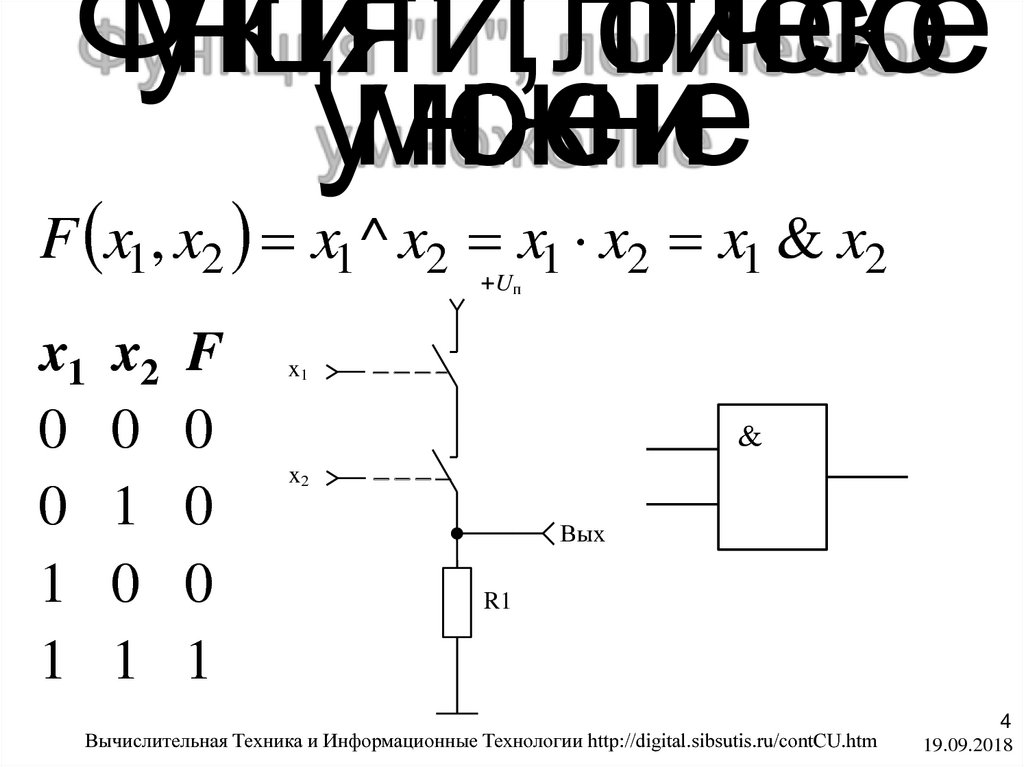

4. Функция "И", логическое умножение

Функция "И", логическоеумножение

F x1, x2 x1 ^ x2 x1 x2 x1 & x2

+Uп

x1

0

0

1

1

x2

0

1

0

1

F

0

0

0

1

x1

&

x2

Вых

R1

Вычислительная Техника и Информационные Технологии http://digital.sibsutis.ru/contCU.htm

4

19.09.2018

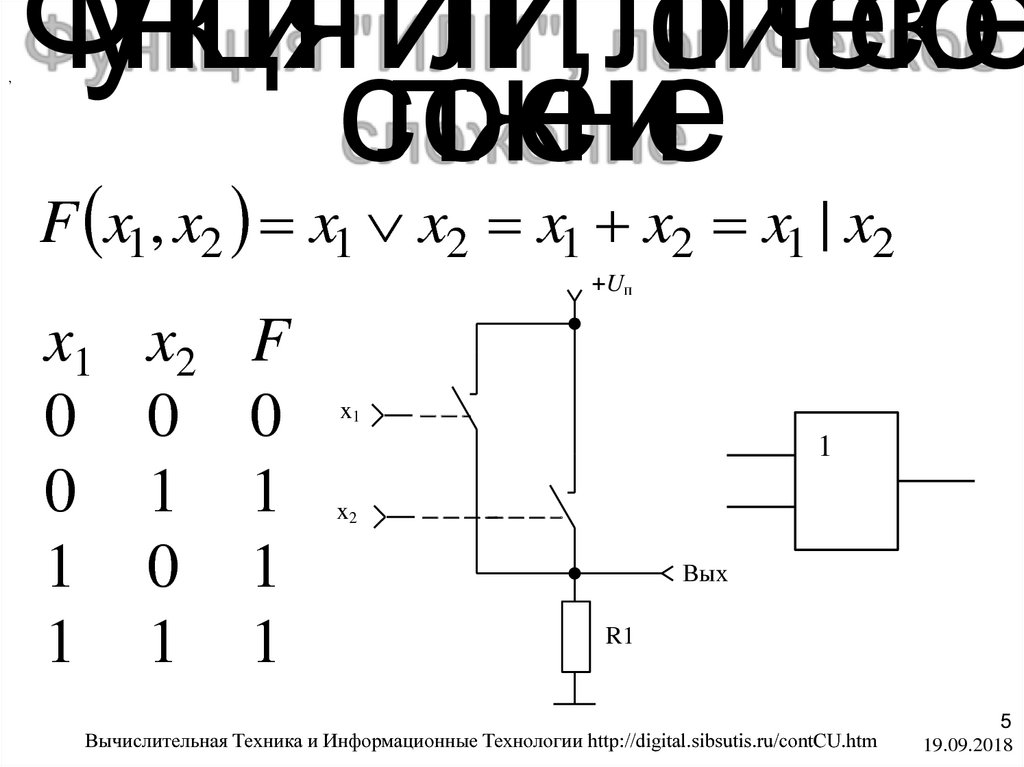

5. Функция "ИЛИ", логическое сложение

,Функция "ИЛИ", логическое

сложение

F x1, x2 x1 x2 x1 x2 x1 | x2

+Uп

x1

0

0

1

1

x2

0

1

0

1

F

0

1

1

1

x1

1

x2

Вых

R1

Вычислительная Техника и Информационные Технологии http://digital.sibsutis.ru/contCU.htm

5

19.09.2018

6. Диодно-транзисторная логика (ДТЛ)

Вычислительная Техника и Информационные Технологии http://digital.sibsutis.ru/contCU.htm6

19.09.2018

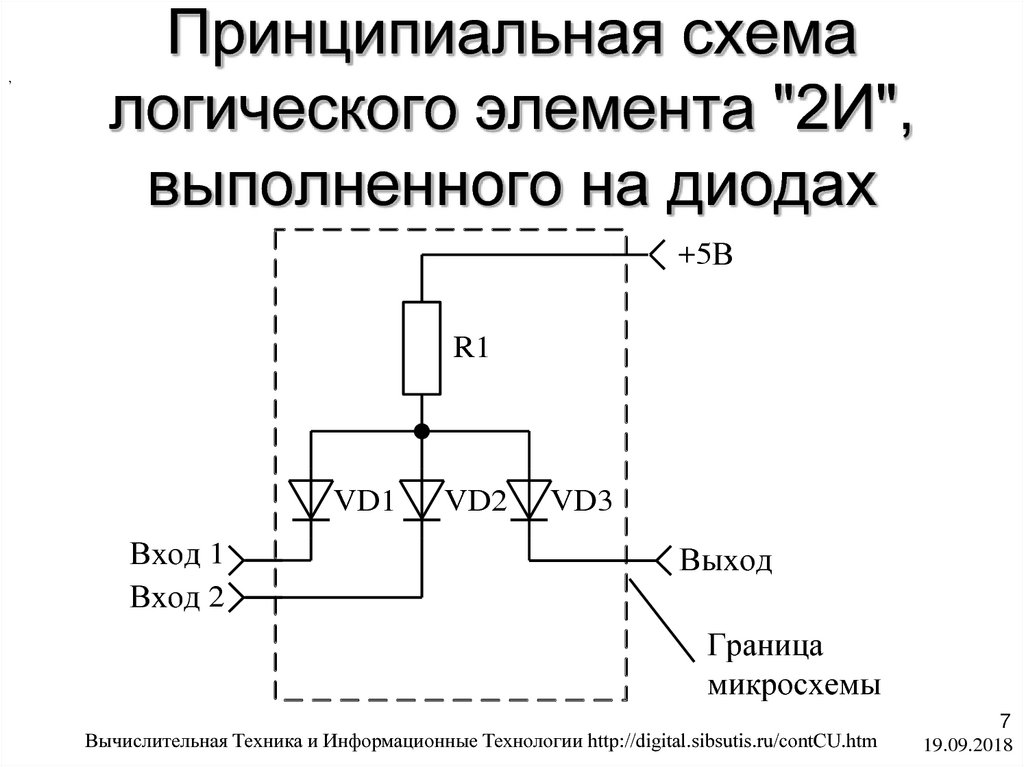

7. Принципиальная схема логического элемента "2И", выполненного на диодах

,Принципиальная схема

логического элемента "2И",

выполненного на диодах

+5В

R1

VD1

Вход 1

Вход 2

VD2

VD3

Выход

Граница

микросхемы

Вычислительная Техника и Информационные Технологии http://digital.sibsutis.ru/contCU.htm

7

19.09.2018

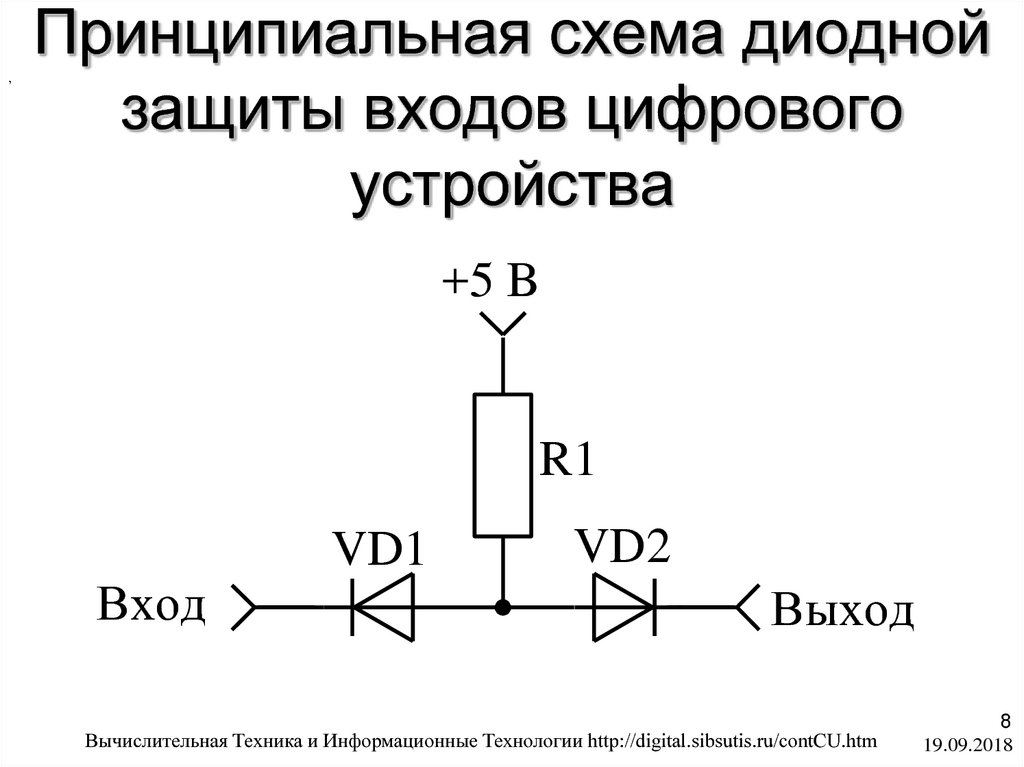

8. Принципиальная схема диодной защиты входов цифрового устройства

,Принципиальная схема диодной

защиты входов цифрового

устройства

+5 B

R1

Вход

VD1

VD2

Выход

Вычислительная Техника и Информационные Технологии http://digital.sibsutis.ru/contCU.htm

8

19.09.2018

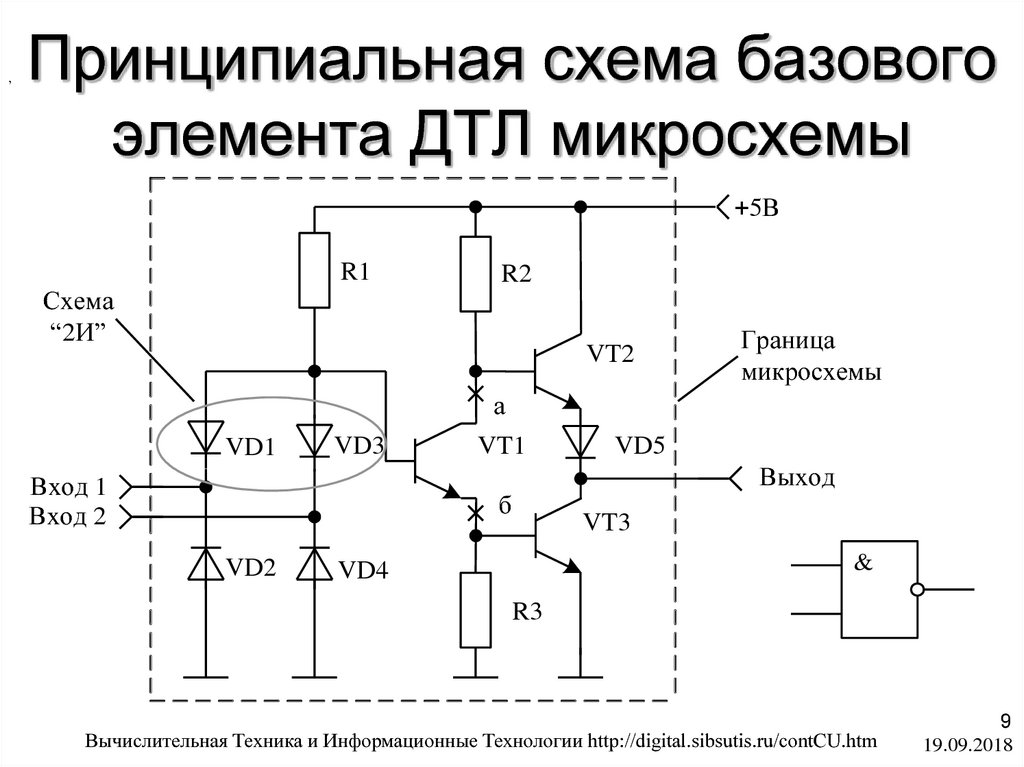

9. Принципиальная схема базового элемента ДТЛ микросхемы

,Принципиальная схема базового

элемента ДТЛ микросхемы

+5В

R1

Схема

“2И”

R2

VT2

Граница

микросхемы

а

VD1

VD3

Вход 1

Вход 2

VT1

Выход

б

VD2

VD5

VT3

&

VD4

R3

Вычислительная Техника и Информационные Технологии http://digital.sibsutis.ru/contCU.htm

9

19.09.2018

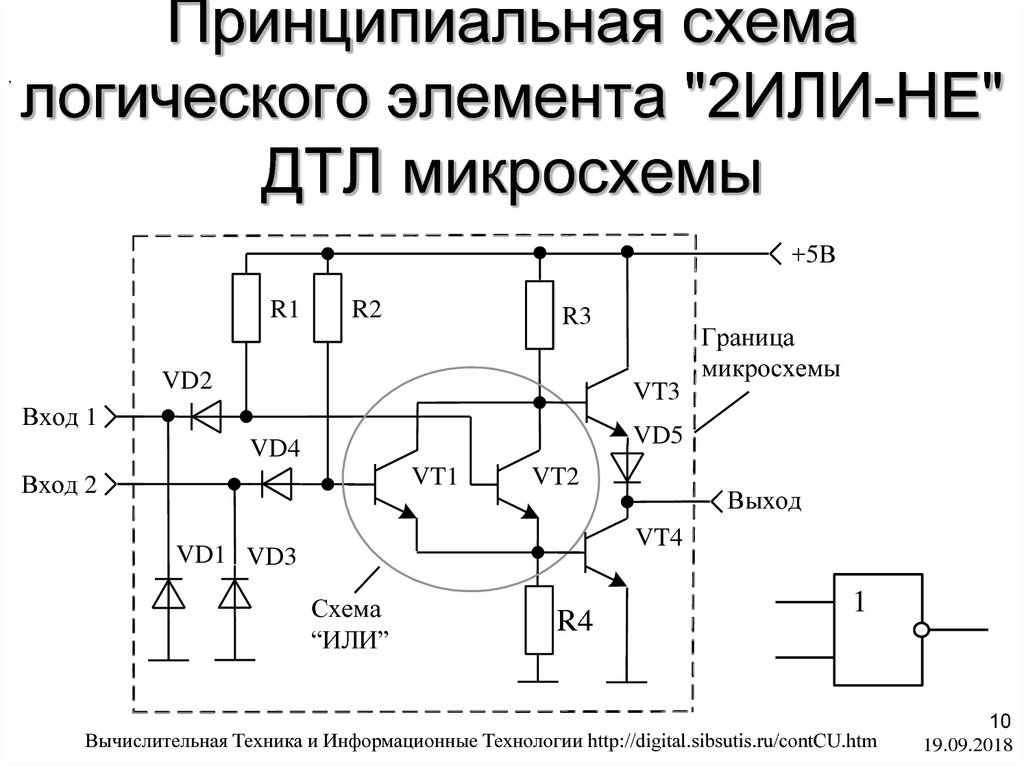

10. Принципиальная схема логического элемента "2ИЛИ-НЕ" ДТЛ микросхемы

,Принципиальная схема

логического элемента "2ИЛИ-НЕ"

ДТЛ микросхемы

+5В

R1

R2

R3

VD2

VT3

Вход 1

Граница

микросхемы

VD5

VD4

VT1

Вход 2

VT2

Выход

VT4

VD1 VD3

Схема

“ИЛИ”

R4

1

Вычислительная Техника и Информационные Технологии http://digital.sibsutis.ru/contCU.htm

10

19.09.2018

11. Транзисторно-транзисторная логика (ТТЛ)

Транзисторнотранзисторная логика(ТТЛ)

Вычислительная Техника и Информационные Технологии http://digital.sibsutis.ru/contCU.htm

11

19.09.2018

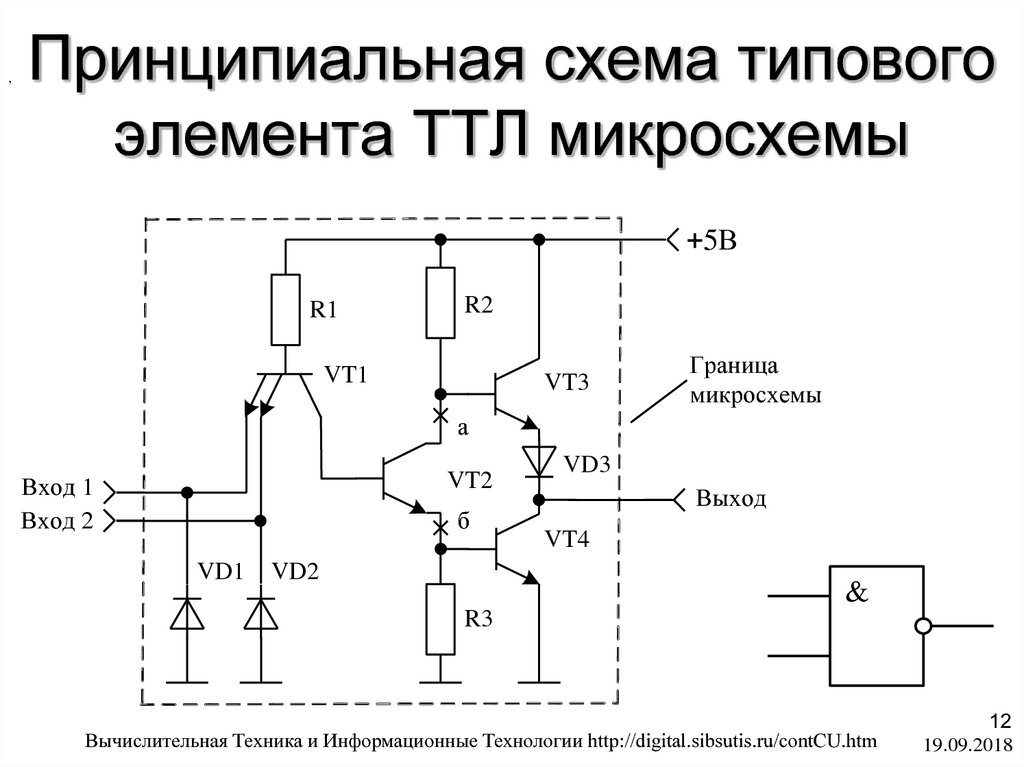

12. Принципиальная схема типового элемента ТТЛ микросхемы

,Принципиальная схема типового

элемента ТТЛ микросхемы

+5В

R1

R2

VT1

VT3

Граница

микросхемы

а

VT2

Вход 1

Вход 2

б

VD1

VD2

VD3

Выход

VT4

&

R3

Вычислительная Техника и Информационные Технологии http://digital.sibsutis.ru/contCU.htm

12

19.09.2018

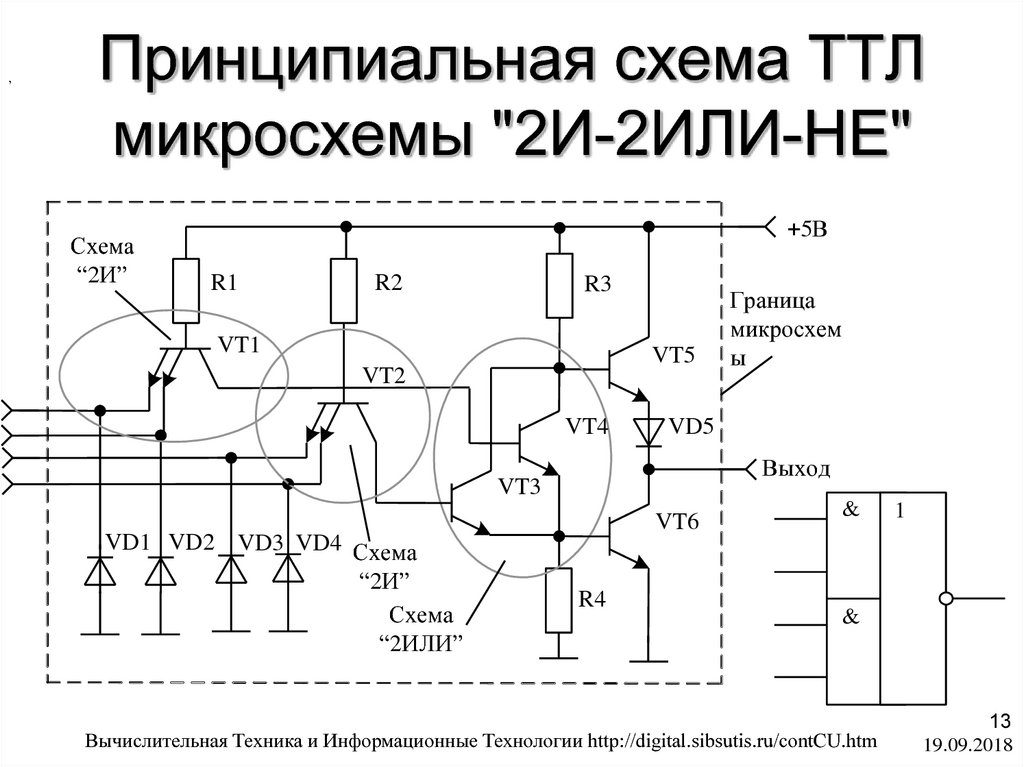

13. Принципиальная схема ТТЛ микросхемы "2И-2ИЛИ-НЕ"

,Принципиальная схема ТТЛ

микросхемы "2И-2ИЛИ-НЕ"

Схема

“2И”

+5В

R1

R2

R3

VT1

VT5

VT2

VT4

VD5

Выход

VT3

VD1 VD2 VD3 VD4 Схема

“2И”

Схема

“2ИЛИ”

Граница

микросхем

ы

VT6

R4

&

1

&

Вычислительная Техника и Информационные Технологии http://digital.sibsutis.ru/contCU.htm

13

19.09.2018

14. Логика на комплементарных МОП транзисторах (КМДП)

Вычислительная Техника и Информационные Технологии http://digital.sibsutis.ru/contCU.htm14

19.09.2018

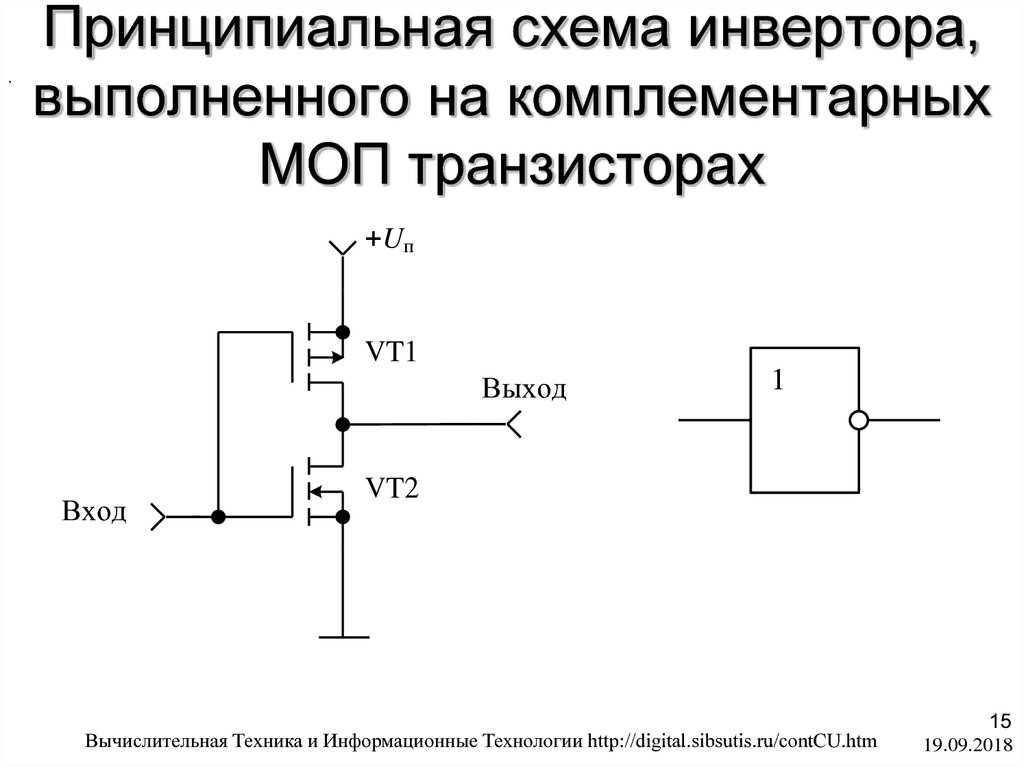

15. Принципиальная схема инвертора, выполненного на комплементарных МОП транзисторах

,Принципиальная схема инвертора,

выполненного на комплементарных

МОП транзисторах

+Uп

VT1

Выход

Вход

1

VT2

Вычислительная Техника и Информационные Технологии http://digital.sibsutis.ru/contCU.htm

15

19.09.2018

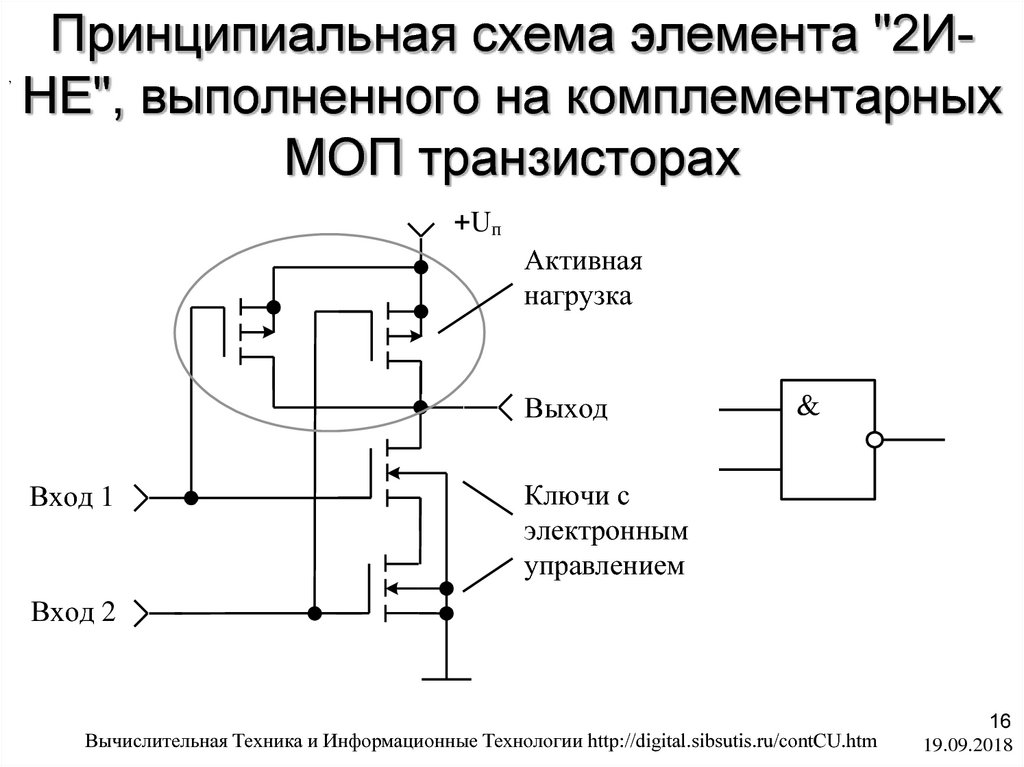

16. Принципиальная схема элемента "2И-НЕ", выполненного на комплементарных МОП транзисторах

,Принципиальная схема элемента "2ИНЕ", выполненного на комплементарных

МОП транзисторах

+Uп

Активная

нагрузка

Выход

Вход 1

&

Ключи с

электронным

управлением

Вход 2

Вычислительная Техника и Информационные Технологии http://digital.sibsutis.ru/contCU.htm

16

19.09.2018

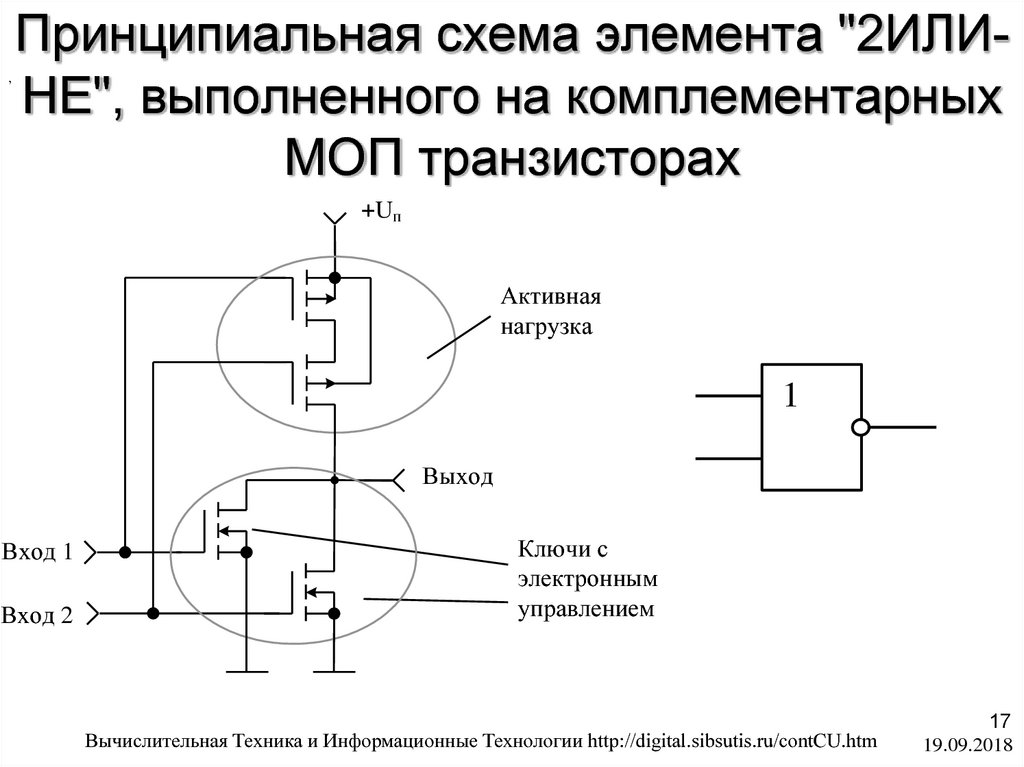

17. Принципиальная схема элемента "2ИЛИ-НЕ", выполненного на комплементарных МОП транзисторах

,Принципиальная схема элемента "2ИЛИНЕ", выполненного на комплементарных

МОП транзисторах

+Uп

Активная

нагрузка

1

Выход

Вход 1

Вход 2

Ключи с

электронным

управлением

Вычислительная Техника и Информационные Технологии http://digital.sibsutis.ru/contCU.htm

17

19.09.2018

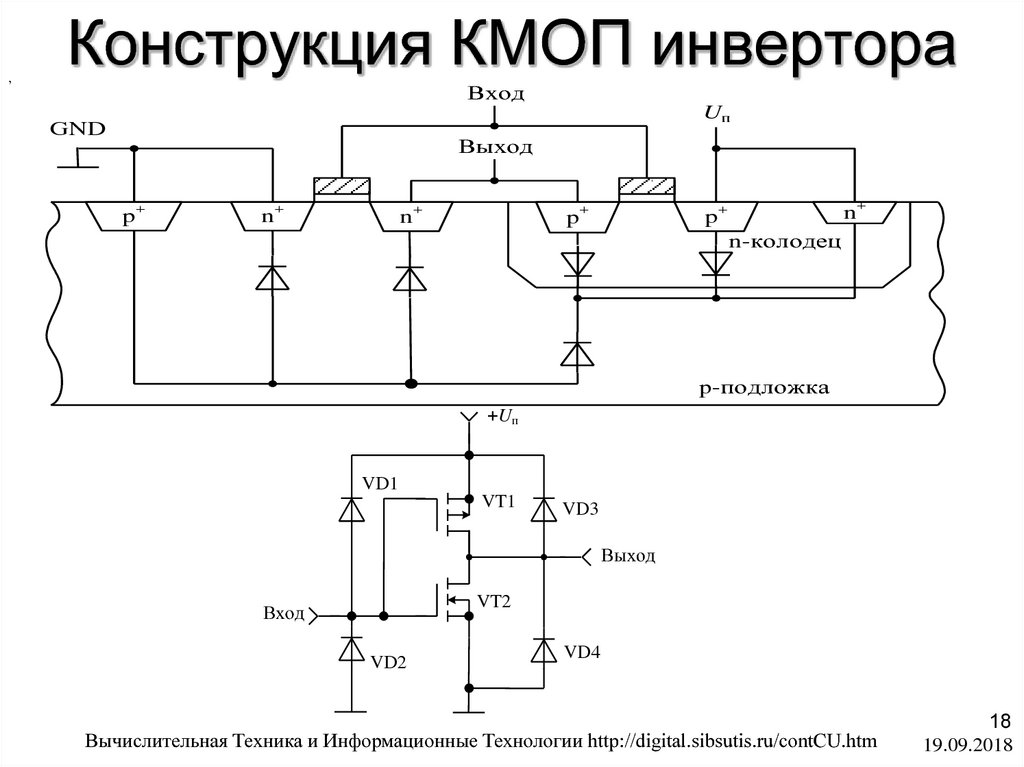

18. Конструкция КМОП инвертора

,Конструкция КМОП инвертора

Вход

Uп

GND

Выход

p+

n+

n+

n+

p+

p+

n-колодец

p-подложка

+Uп

VD1

VT1

VD3

Выход

VT2

Вход

VD2

VD4

Вычислительная Техника и Информационные Технологии http://digital.sibsutis.ru/contCU.htm

18

19.09.2018

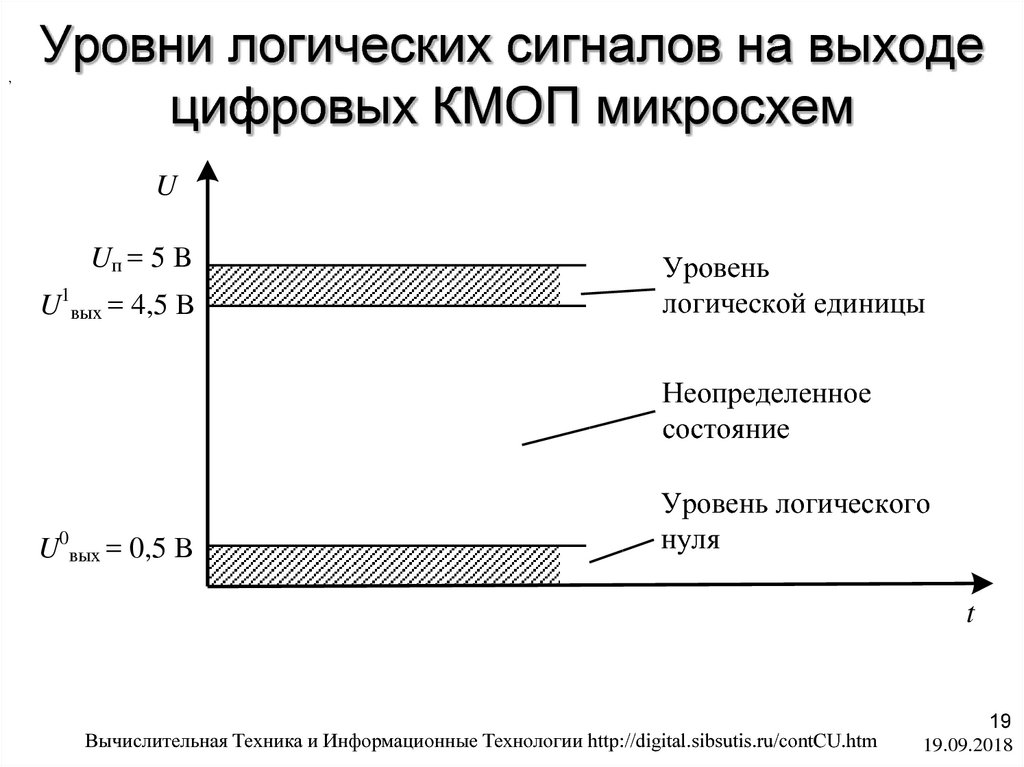

19. Уровни логических сигналов на выходе цифровых КМОП микросхем

,Уровни логических сигналов на выходе

цифровых КМОП микросхем

U

Uп = 5 B

U1вых = 4,5 B

Уровень

логической единицы

Неопределенное

состояние

U0вых = 0,5 B

Уровень логического

нуля

t

Вычислительная Техника и Информационные Технологии http://digital.sibsutis.ru/contCU.htm

19

19.09.2018

20. Регенерация цифрового сигнала

Вычислительная Техника и Информационные Технологии http://digital.sibsutis.ru/contCU.htm20

19.09.2018

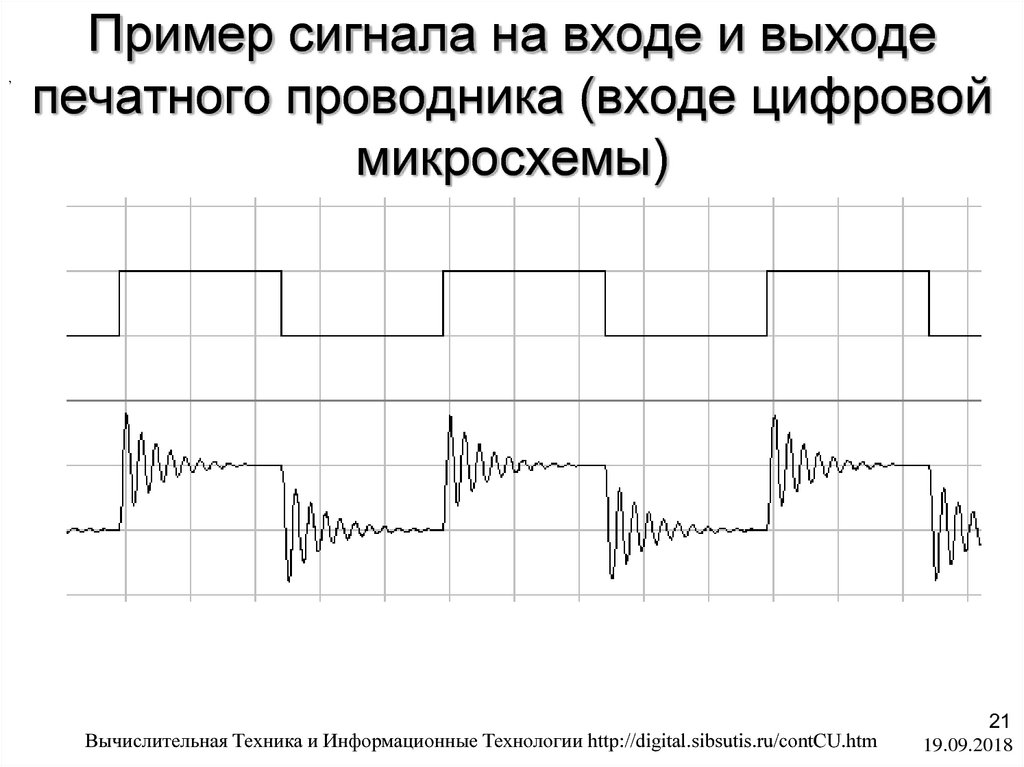

21. Пример сигнала на входе и выходе печатного проводника (входе цифровой микросхемы)

,Пример сигнала на входе и выходе

печатного проводника (входе цифровой

микросхемы)

Вычислительная Техника и Информационные Технологии http://digital.sibsutis.ru/contCU.htm

21

19.09.2018

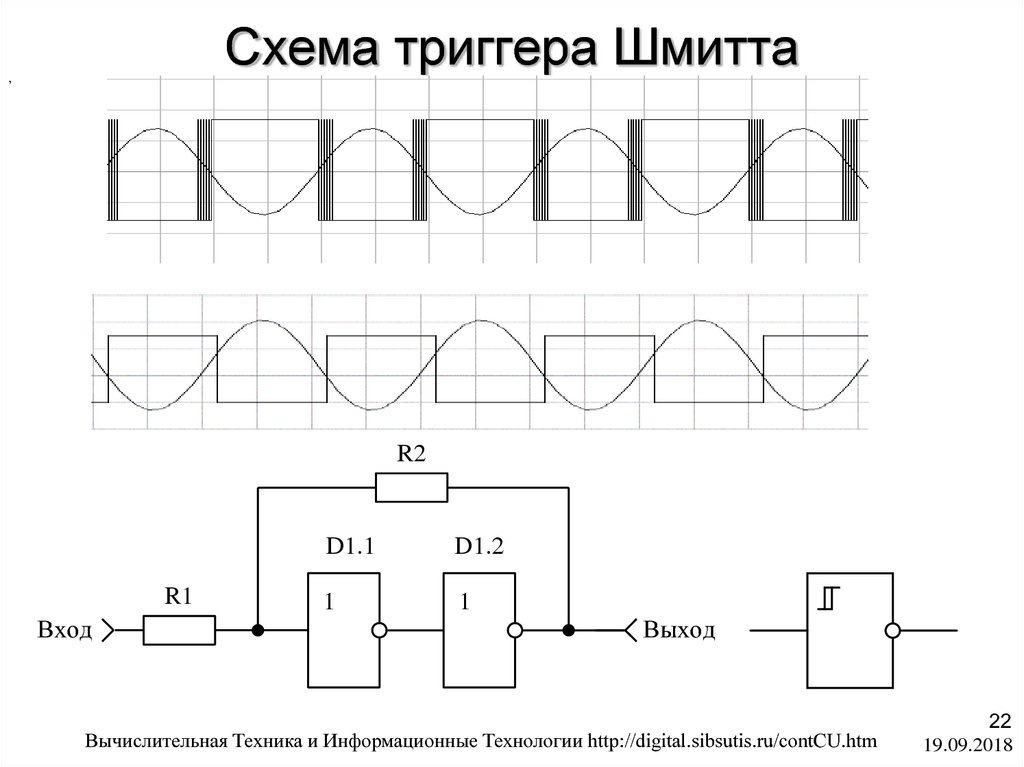

22. Схема триггера Шмитта

,R2

R1

Вход

D1.1

D1.2

1

1

Выход

Вычислительная Техника и Информационные Технологии http://digital.sibsutis.ru/contCU.htm

22

19.09.2018

23.

Вычислительная Техника и Информационные Технологии http://digital.sibsutis.ru/contCU.htm23

19.09.2018

Информатика

Информатика