Похожие презентации:

Цифровая схемотехника и архитектура компьютера, второе издание. Глава 1

1.

Глава 1Цифровая схемотехника и архитектура

компьютера, второе издание

Дэвид М. Харрис и Сара Л. Харрис

Глава 1 <1>

2.

Логические элементы• Выполняют логические функции

– Инверсия (НЕ), И (AND), ИЛИ (OR), И-НЕ(NAND),

ИЛИ-НЕ(NOR), и т.д.

• С одним входом

– Элемент НЕ, буфер

• С двумя входами

– И, ИЛИ, И-НЕ, ИЛИ-НЕ, Исключающее ИЛИ,

Исключающее ИЛИ-НЕ

• С несколькими входами

Глава 1 <2>

3.

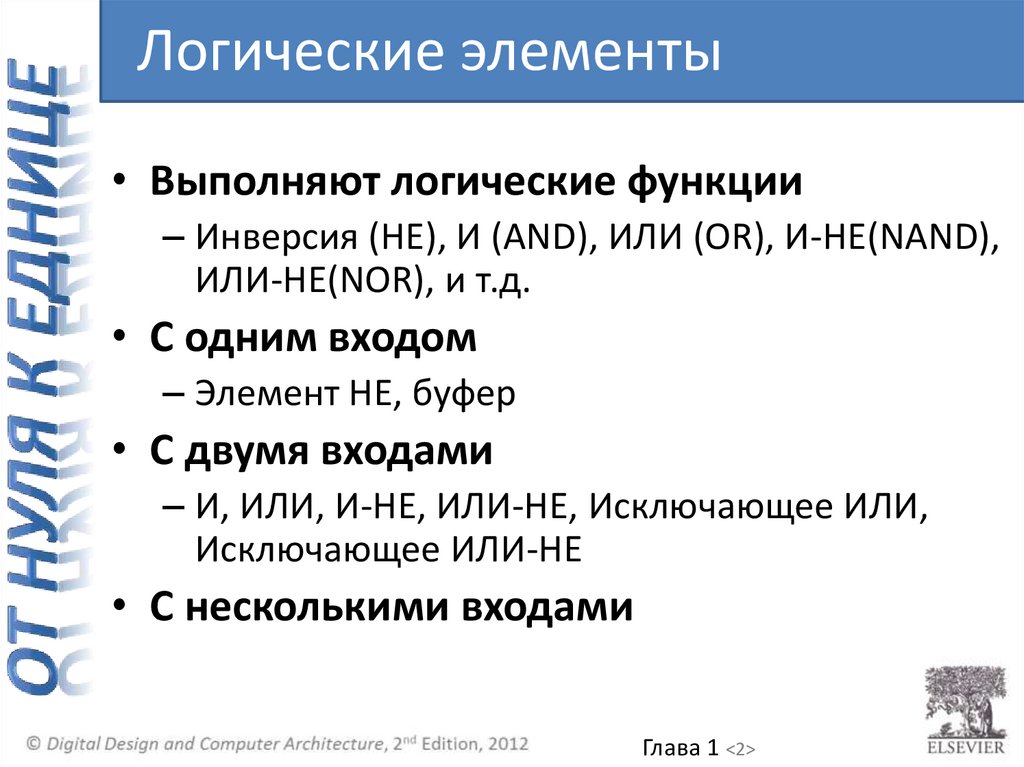

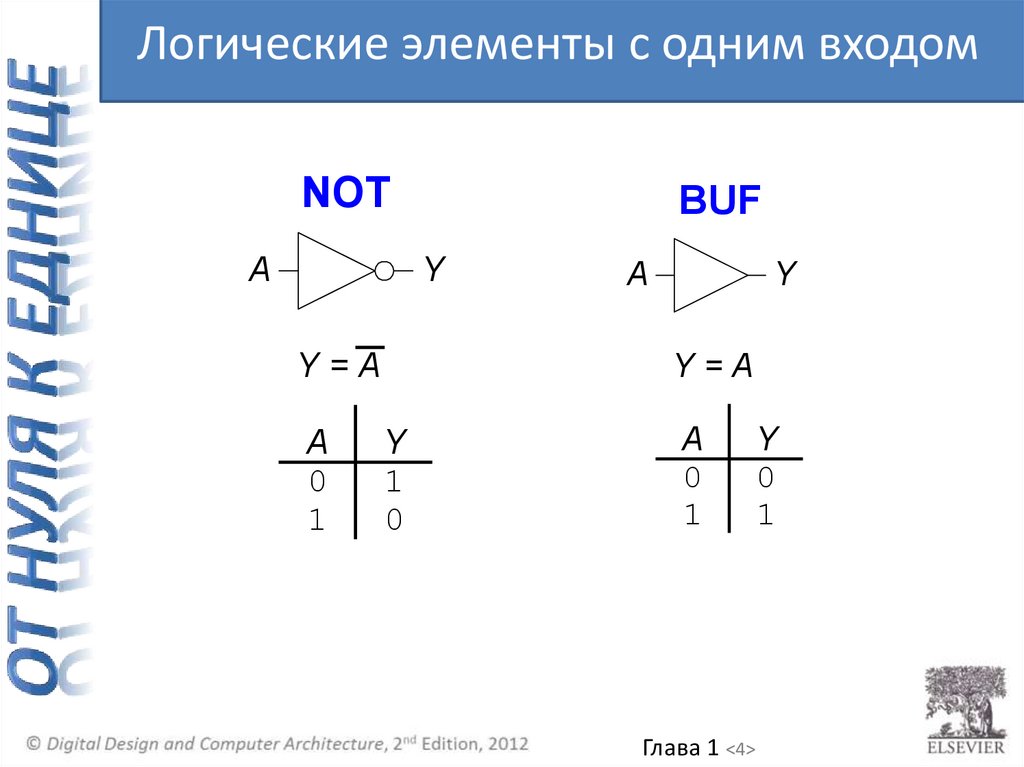

Логические элементы с одним входомNOT

A

BUF

Y

Y=A

A

0

1

A

Y

Y=A

Y

A

0

1

Y

Глава 1 <3>

4.

Логические элементы с одним входомNOT

A

BUF

Y

Y=A

A

0

1

A

Y

Y=A

Y

1

0

A

0

1

Y

0

1

Глава 1 <4>

5.

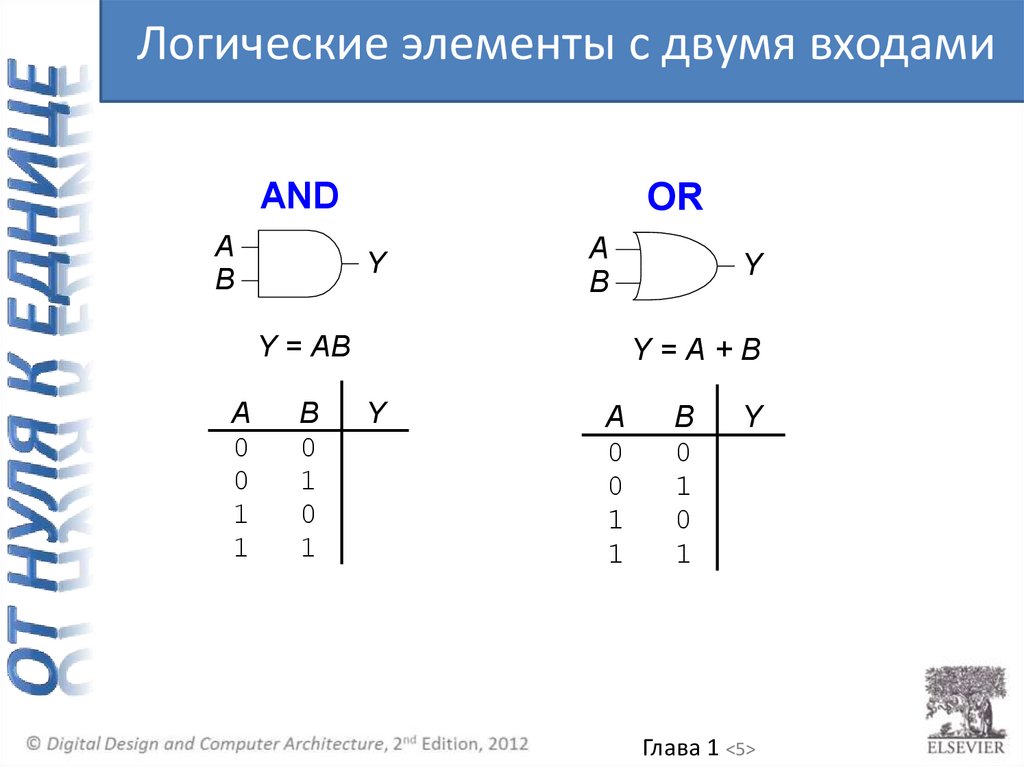

Логические элементы с двумя входамиAND

A

B

OR

Y

A

B

Y = AB

A

0

0

1

1

B

0

1

0

1

Y

Y=A+B

Y

A

0

0

1

1

B

0

1

0

1

Y

Глава 1 <5>

6.

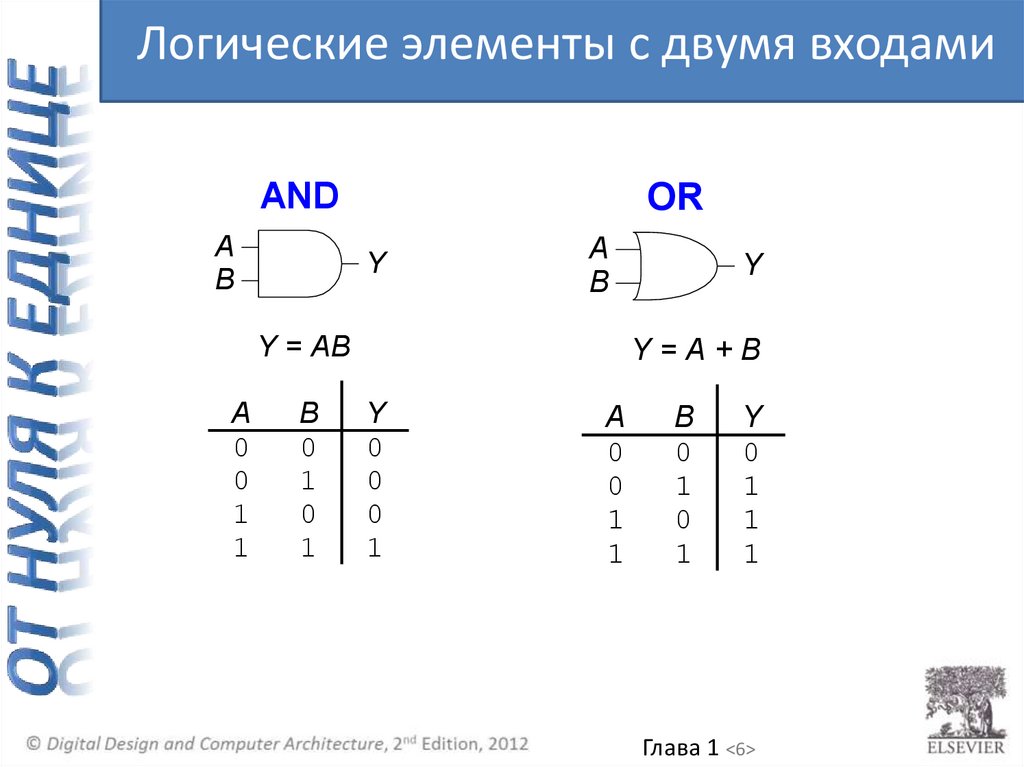

Логические элементы с двумя входамиAND

A

B

OR

Y

A

B

Y = AB

A

0

0

1

1

B

0

1

0

1

Y

Y=A+B

Y

0

0

0

1

A

0

0

1

1

B

0

1

0

1

Y

0

1

1

1

Глава 1 <6>

7.

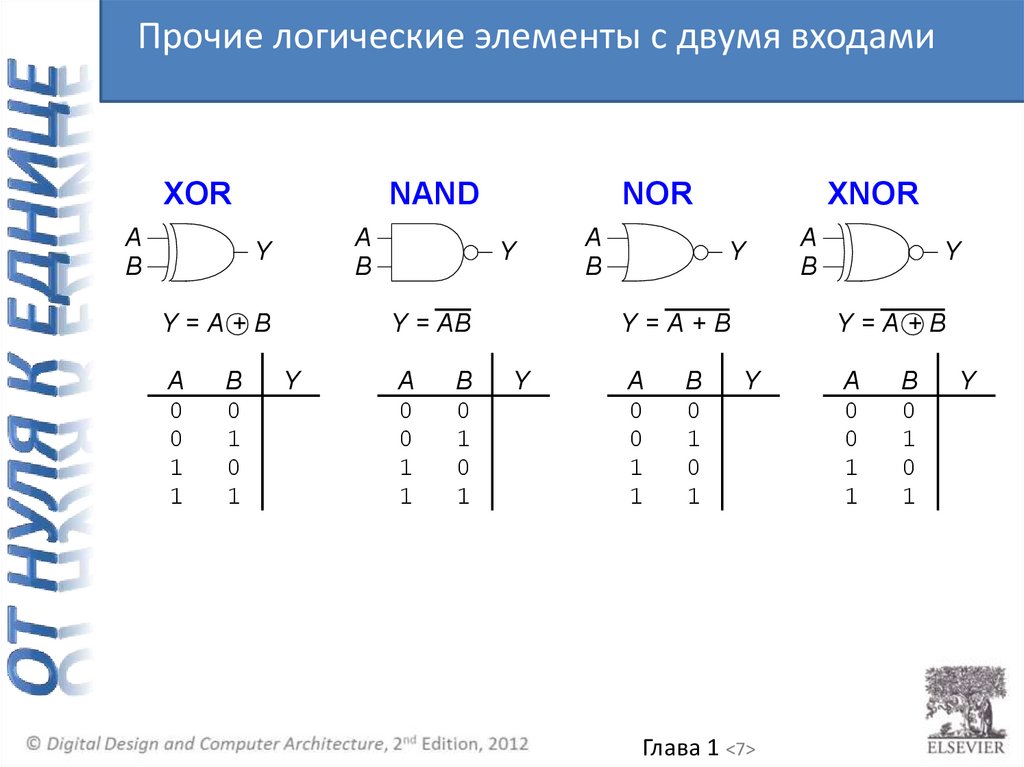

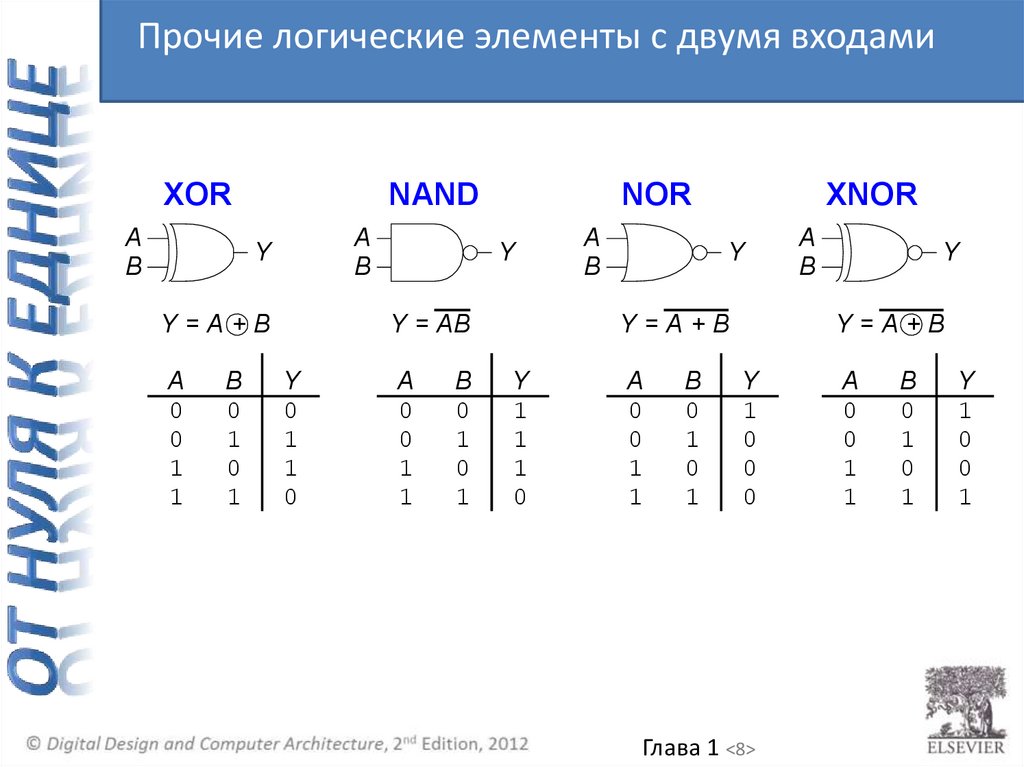

Прочие логические элементы с двумя входамиXOR

A

B

NAND

A

B

Y

Y=A+B

A

0

0

1

1

B

0

1

0

1

NOR

Y

Y = AB

Y

A

0

0

1

1

B

0

1

0

1

A

B

XNOR

Y

Y=A+B

Y

A

0

0

1

1

B

0

1

0

1

A

B

Y

Y=A+B

Y

Глава 1 <7>

A

0

0

1

1

B

0

1

0

1

Y

8.

Прочие логические элементы с двумя входамиXOR

A

B

NAND

A

B

Y

Y=A+B

A

0

0

1

1

B

0

1

0

1

NOR

Y

Y = AB

Y

0

1

1

0

A

0

0

1

1

B

0

1

0

1

A

B

XNOR

Y

Y=A+B

Y

1

1

1

0

A

0

0

1

1

B

0

1

0

1

A

B

Y

Y=A+B

Y

1

0

0

0

Глава 1 <8>

A

0

0

1

1

B

0

1

0

1

Y

1

0

0

1

9.

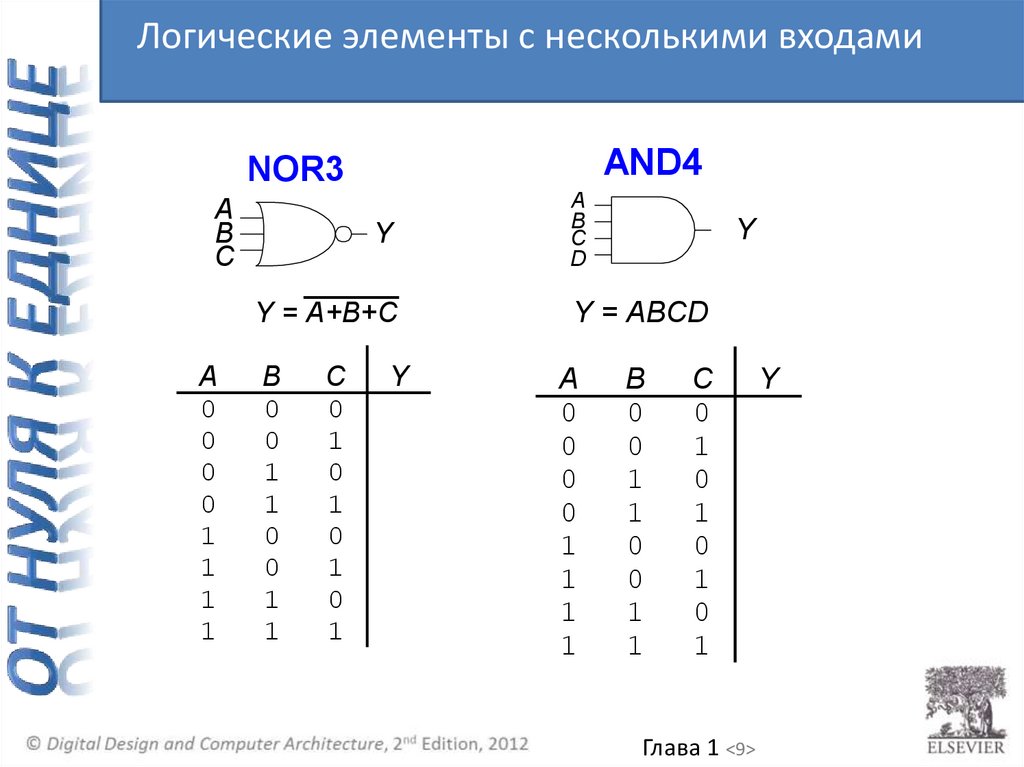

Логические элементы с несколькими входамиAND4

NOR3

A

B

C

Y

Y = A+B+C

A

0

0

0

0

1

1

1

1

B

0

0

1

1

0

0

1

1

C

0

1

0

1

0

1

0

1

Y

A

B

C

D

Y

Y = ABCD

A

0

0

0

0

1

1

1

1

B

0

0

1

1

0

0

1

1

C

0

1

0

1

0

1

0

1

Глава 1 <9>

Y

10.

Логические элементы с несколькими входамиAND4

NOR3

A

B

C

Y

Y = A+B+C

A

0

0

0

0

1

1

1

1

B

0

0

1

1

0

0

1

1

C

0

1

0

1

0

1

0

1

Y

1

0

0

0

0

0

0

0

A

B

C

D

Y

Y = ABCD

A

0

0

0

0

1

1

1

1

B

0

0

1

1

0

0

1

1

C

0

1

0

1

0

1

0

1

Y

0

0

0

0

0

0

0

1

• Многовходовый элемент XOR: Контроль четности

Глава 1 <10>

11.

Логические уровни• Дискретные уровни напряжения

представляют 1 и 0

• Например:

– 0 = земля (GND) или 0 В

– 1 = VDD или 5 В

• Как трактовать напряжение 4.99 В? Это 0

или 1?

• Как трактовать напряжение 3.2 В?

Глава 1 <11>

12.

Логические уровни• Диапазон напряжений для 1 и 0

• Разные диапазоны для входов и

выходов обеспечивают работу схем

при наличии помех и шумов

Глава 1 <12>

13.

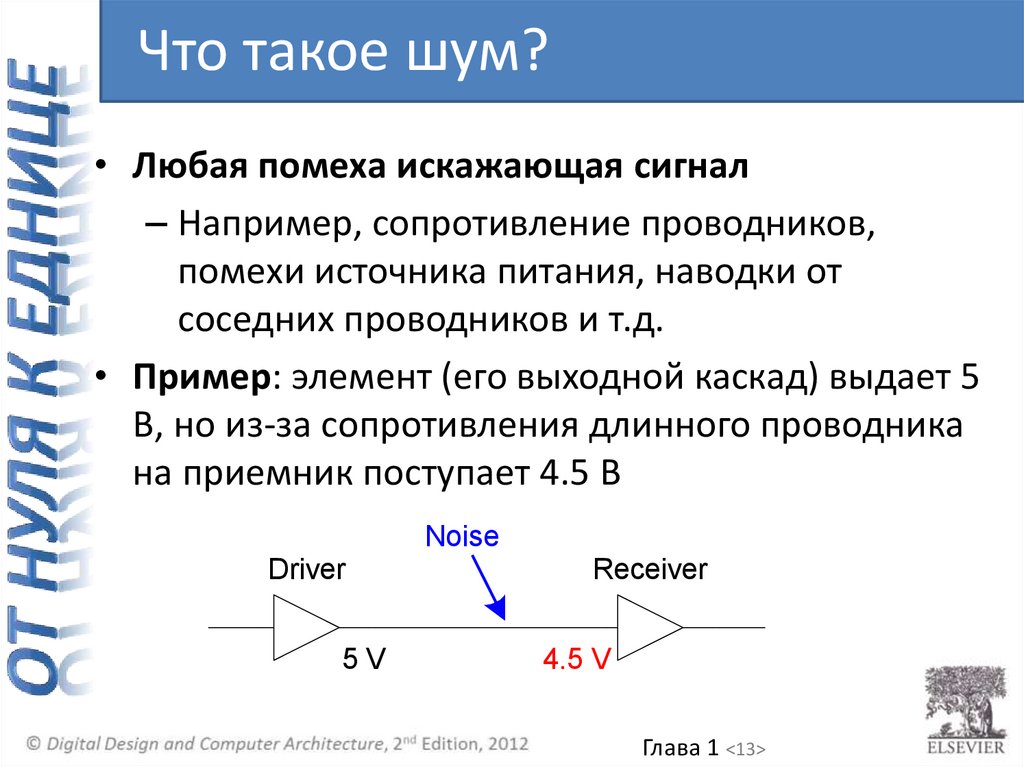

Что такое шум?• Любая помеха искажающая сигнал

– Например, сопротивление проводников,

помехи источника питания, наводки от

соседних проводников и т.д.

• Пример: элемент (его выходной каскад) выдает 5

В, но из-за сопротивления длинного проводника

на приемник поступает 4.5 В

Noise

Driver

5V

Receiver

4.5 V

Глава 1 <13>

14.

Статическая дисциплина• Если на вход элемента поступают

корректные логические значения, на

его выходе формируются корректные

выходные сигналы

• Для представления дискретных

величин используется ограниченный

диапазон напряжений

Глава 1 <14>

15.

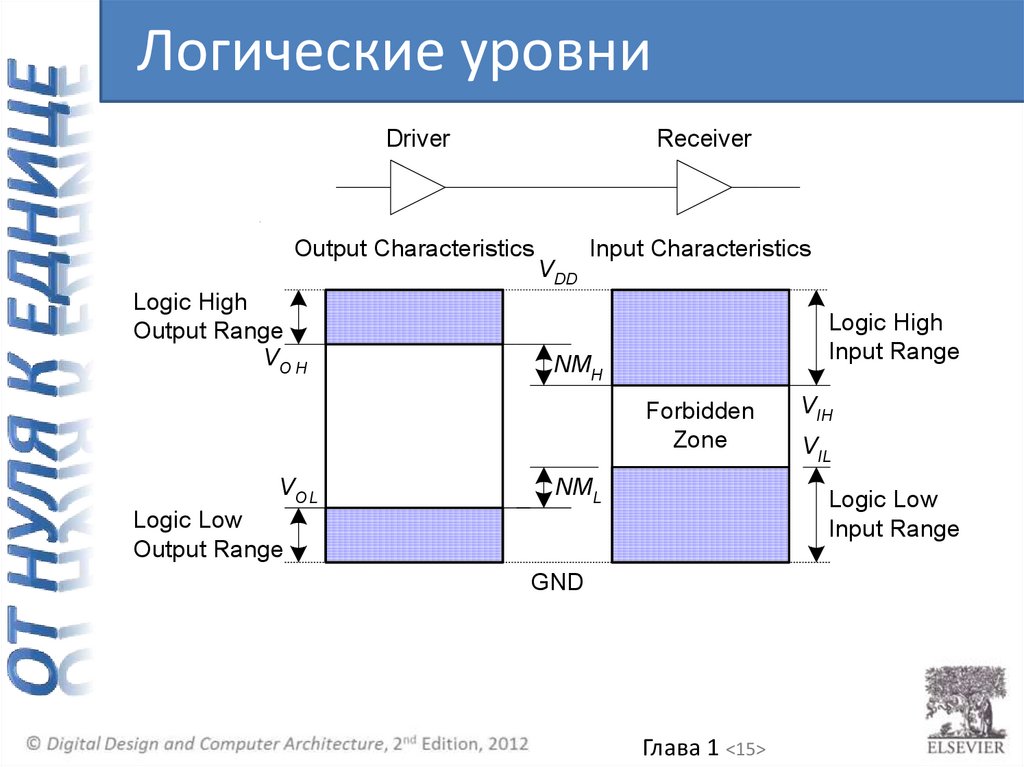

Логические уровниDriver

Receiver

Output Characteristics

Logic High

Output Range

VO H

VDD

Input Characteristics

Logic High

Input Range

NMH

Forbidden

Zone

VO L

NML

VIH

VIL

Logic Low

Input Range

Logic Low

Output Range

GND

Глава 1 <15>

16.

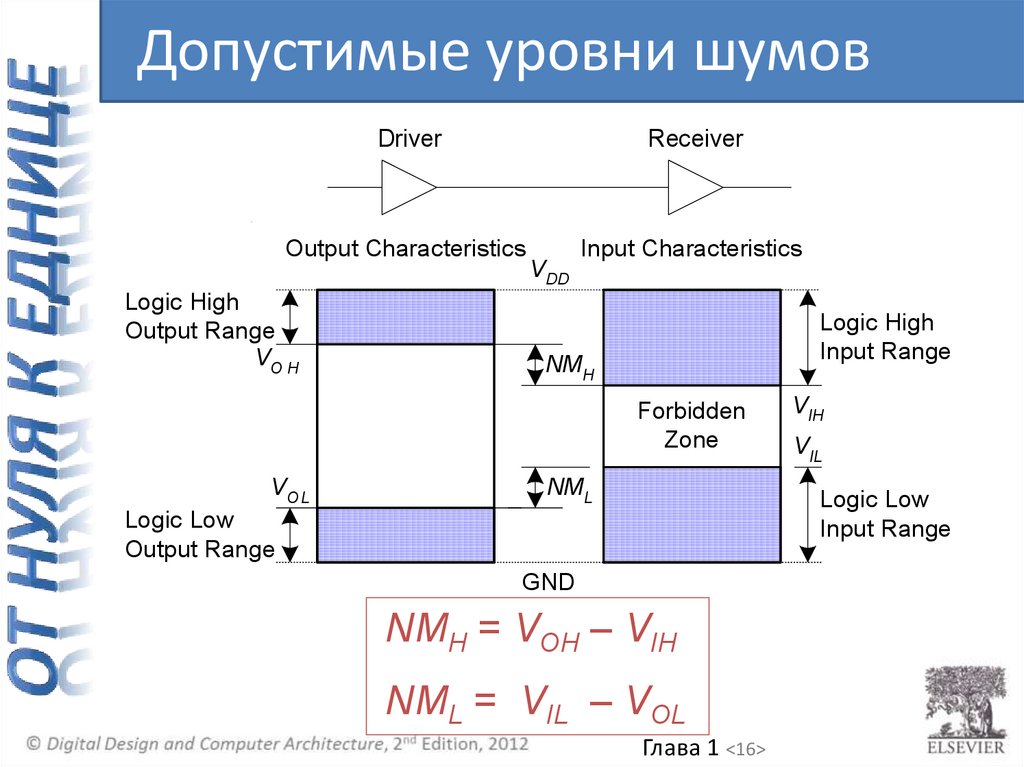

Допустимые уровни шумовDriver

Receiver

Output Characteristics

Logic High

Output Range

VO H

VDD

Input Characteristics

Logic High

Input Range

NMH

Forbidden

Zone

VO L

NML

VIH

VIL

Logic Low

Input Range

Logic Low

Output Range

GND

NMH = VOH – VIH

NML = VIL – VOL

Глава 1 <16>

17.

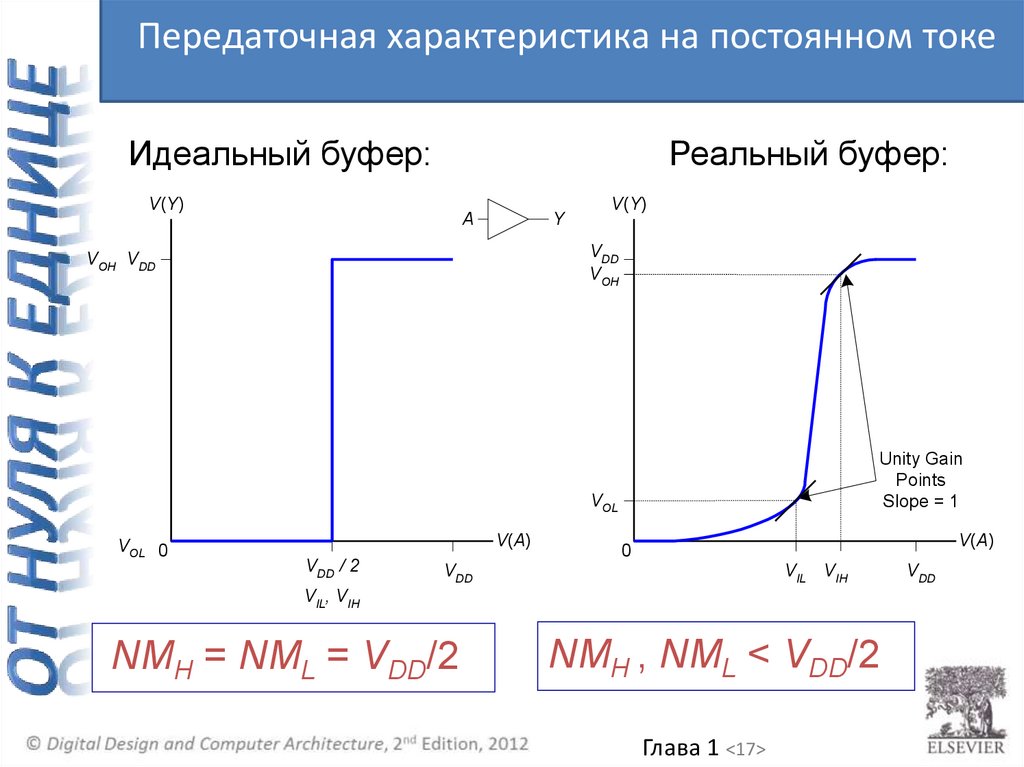

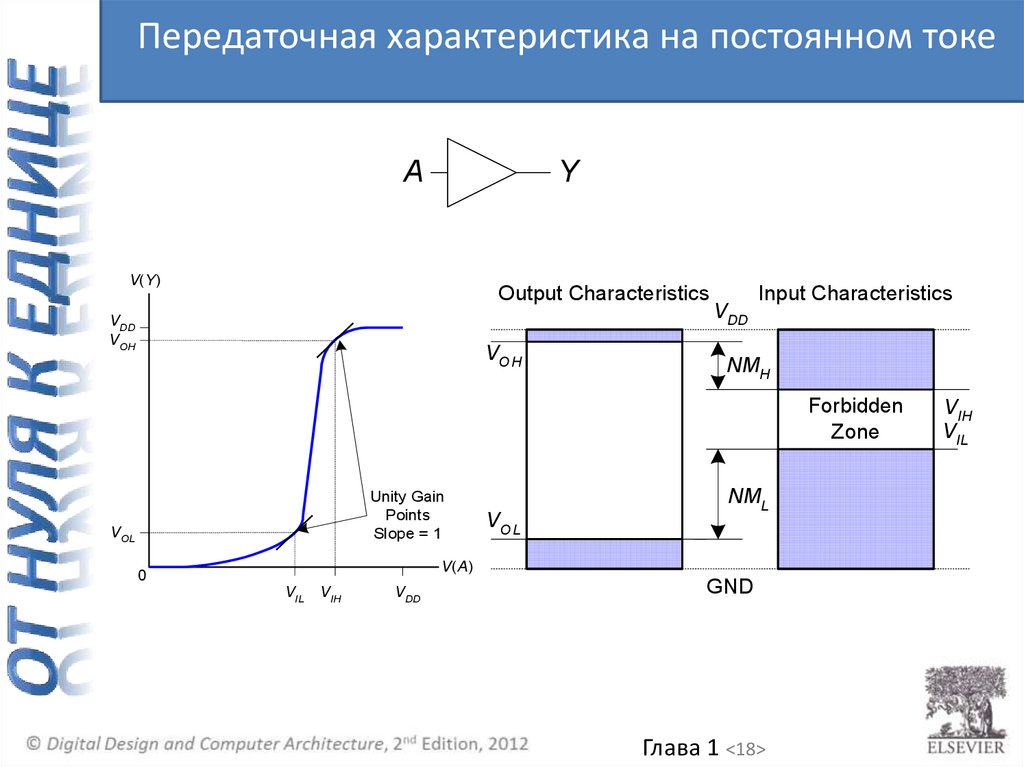

Передаточная характеристика на постоянном токеИдеальный буфер:

Реальный буфер:

V(Y)

A

Y

V(Y)

VDD

VOH

VOH VDD

Unity Gain

Points

Slope = 1

VOL

VOL 0

V(A)

VDD / 2

V(A)

0

VDD

VIL VIH

VIL, VIH

NMH = NML = VDD/2

NMH , NML < VDD/2

Глава 1 <17>

VDD

18.

Передаточная характеристика на постоянном токеA

Y

V(Y)

Output Characteristics

VDD

VOH

VO H

VDD

Input Characteristics

NMH

Forbidden

Zone

Unity Gain

Points

Slope = 1

VOL

VO L

NML

V(A)

0

VIL

VIH

VDD

GND

Глава 1 <18>

VIH

VIL

19.

Изменение VDD• В 1970 и 1980 годы, VDD = 5 В

• В следующие годы VDD уменьшается

– Уменьшается нагрев транзисторов

– Уменьшается энергопотребление

• 3.3 В, 2.5 В, 1.8 В, 1.5 В, 1.2 В, 1.0 В, …

• При соединении микросхем с

разными напряжениями питания

нужно быть очень осторожным

Микросхемы работают, пока они

содержат волшебный дым

Доказательство:

– Если волшебный дым покидает

микросхему, она перестает работать

Глава 1 <19>

20.

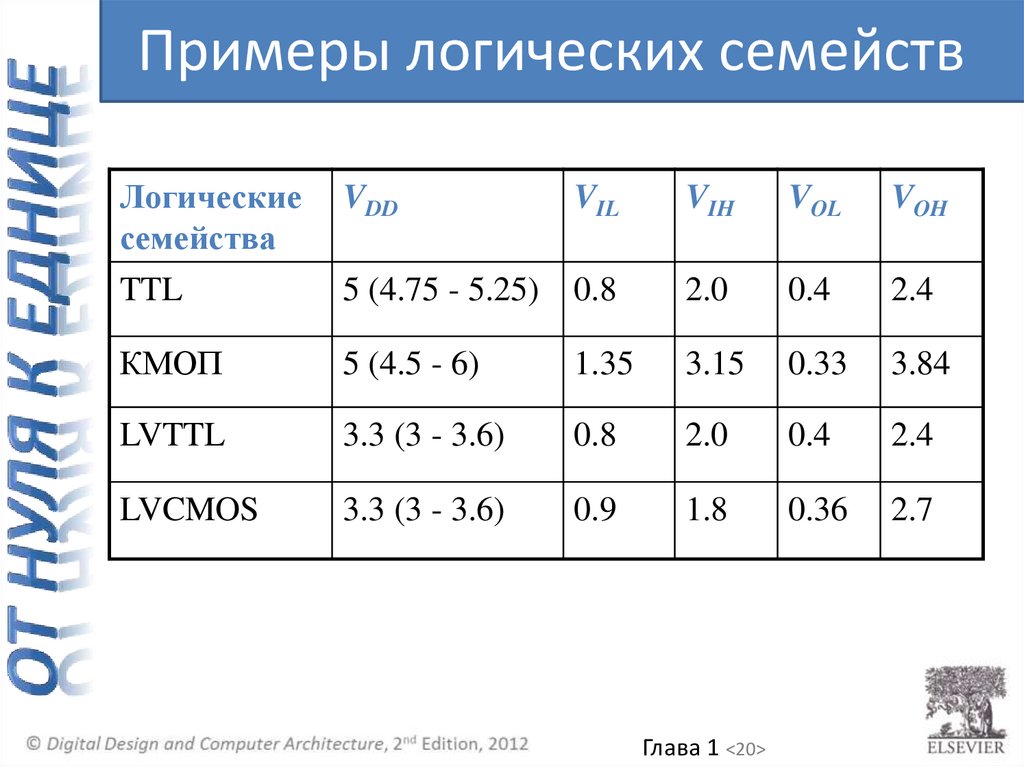

Примеры логических семействЛогические

семейства

TTL

VDD

VIL

VIH

VOL

VOH

5 (4.75 - 5.25)

0.8

2.0

0.4

2.4

КМОП

5 (4.5 - 6)

1.35

3.15

0.33

3.84

LVTTL

3.3 (3 - 3.6)

0.8

2.0

0.4

2.4

LVCMOS

3.3 (3 - 3.6)

0.9

1.8

0.36

2.7

Глава 1 <20>

21.

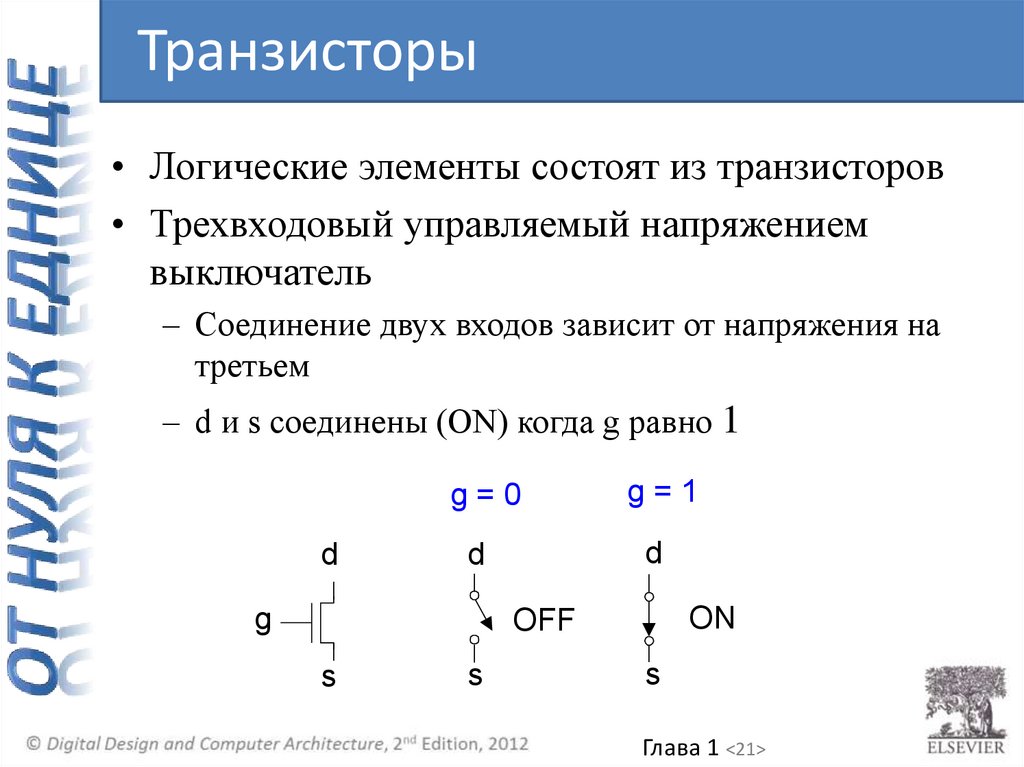

Транзисторы• Логические элементы состоят из транзисторов

• Трехвходовый управляемый напряжением

выключатель

– Соединение двух входов зависит от напряжения на

третьем

– d и s соединены (ON) когда g равно 1

d

g=0

g=1

d

d

g

ON

OFF

s

s

s

Глава 1 <21>

22.

Роберт Нойс, 1927-1990• Прозвище - “Мэр

Силиконовой долины”

• Со-основатель Fairchild

Semiconductor в 1957 году

• Со-основатель Intel в 1968

году

• Одни из изобретателей

интегральной микросхемы

Глава 1 <22>

23.

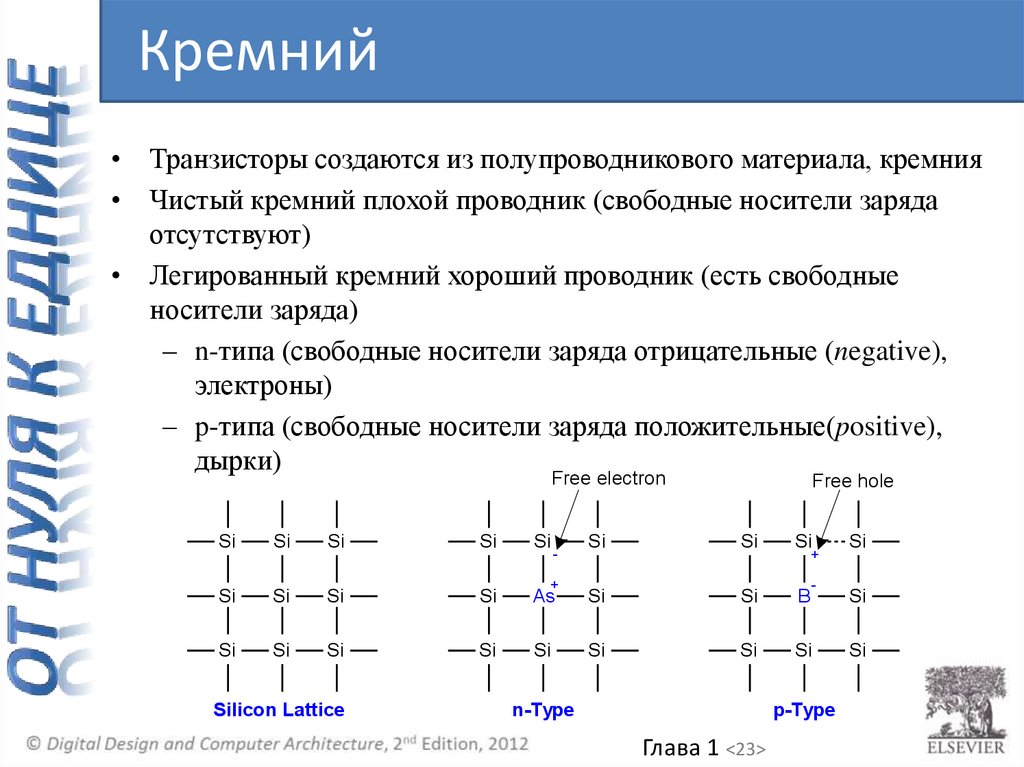

Кремний• Транзисторы создаются из полупроводникового материала, кремния

• Чистый кремний плохой проводник (свободные носители заряда

отсутствуют)

• Легированный кремний хороший проводник (есть свободные

носители заряда)

– n-типа (свободные носители заряда отрицательные (negative),

электроны)

– p-типа (свободные носители заряда положительные(positive),

дырки)

Free electron

Si

Si

Si

Si

Si

Si

Si

Si

Si

Si

Si

Si

Si

Silicon Lattice

Free hole

Si

Si

Si

As

Si

Si

B

Si

Si

Si

Si

-

+

n-Type

+

-

p-Type

Глава 1 <23>

Si

Si

Si

24.

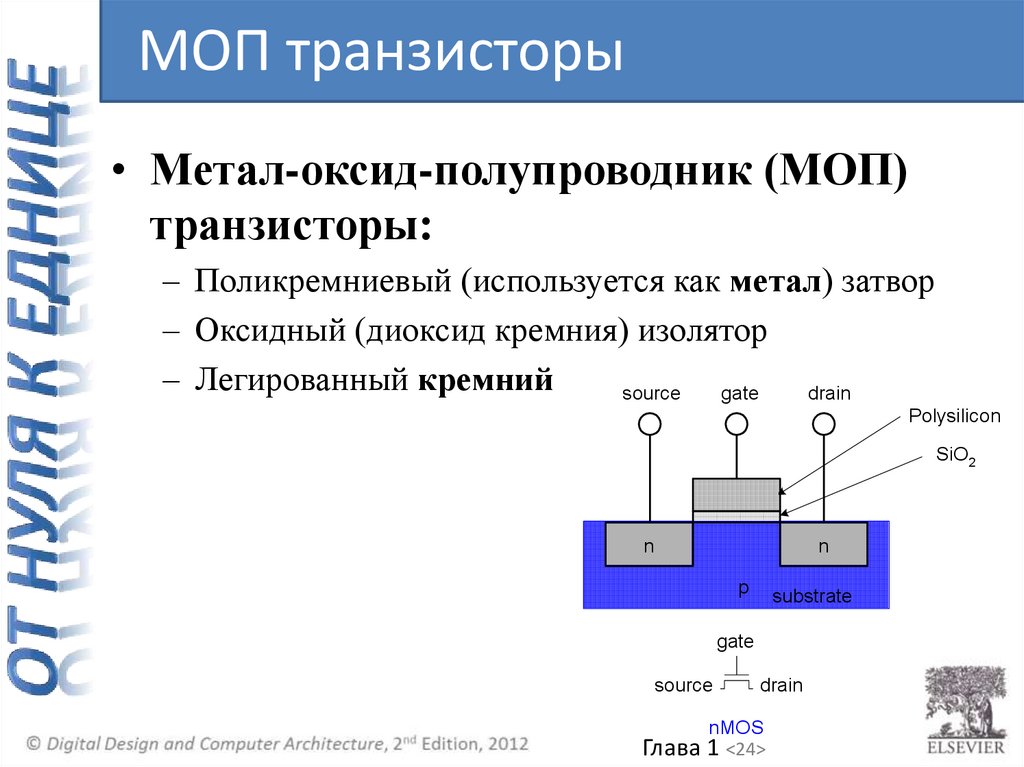

МОП транзисторы• Метал-оксид-полупроводник (МОП)

транзисторы:

– Поликремниевый (используется как метал) затвор

– Оксидный (диоксид кремния) изолятор

– Легированный кремний

source

gate

drain

Polysilicon

SiO2

n

n

p

substrate

gate

source

Глава

drain

nMOS

1 <24>

25.

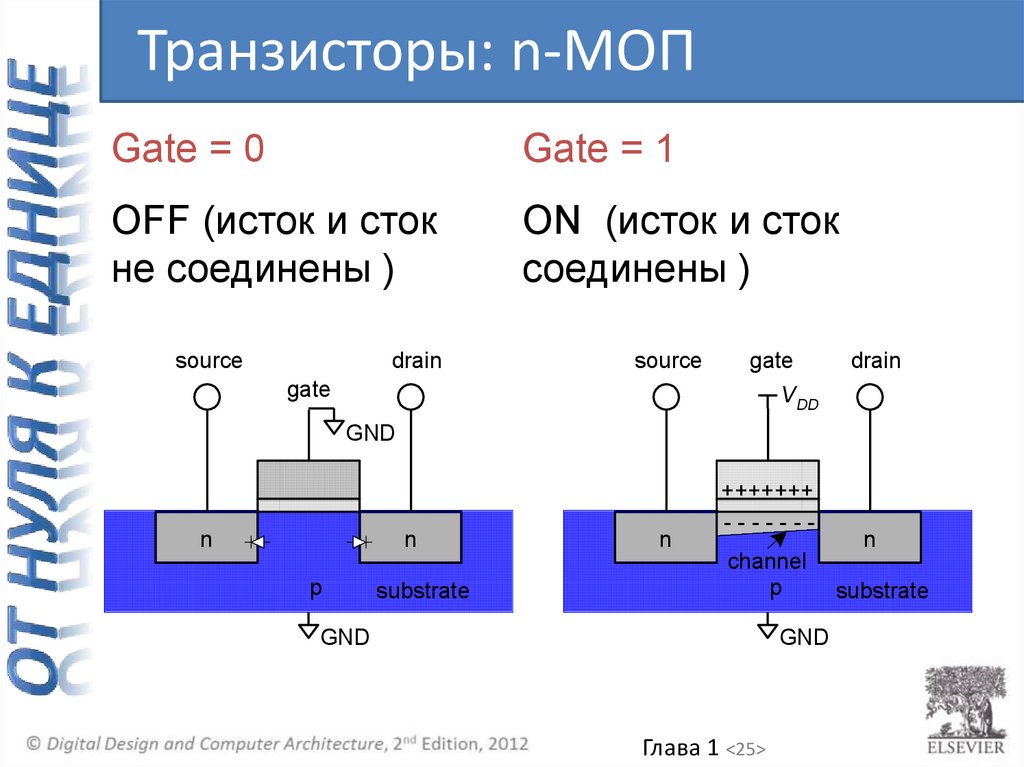

Транзисторы: n-МОПGate = 0

Gate = 1

OFF (исток и сток

не соединены )

ON (исток и сток

соединены )

source

drain

source

gate

gate

VDD

drain

GND

n

n

p

substrate

n

+++++++

------channel

p

GND

GND

Глава 1 <25>

n

substrate

26.

Транзисторы: p-МОП• p-МОП транзистор работает

противоположным образом

– ON, когда Gate = 0

– OFF, когда Gate = 1

source

gate

drain

Polysilicon

SiO2

p

p

n

substrate

gate

source

drain

Глава 1 <26>

27.

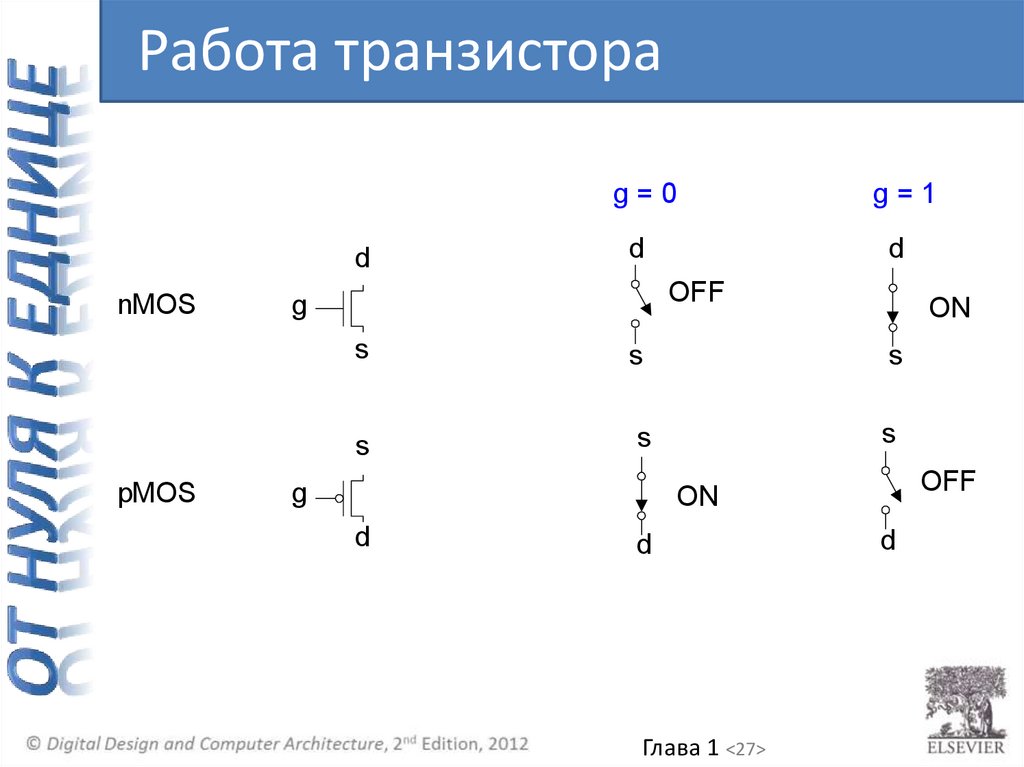

Работа транзистораd

nMOS

pMOS

g=0

g=1

d

d

OFF

g

ON

s

s

s

s

s

s

g

OFF

ON

d

d

Глава 1 <27>

d

28.

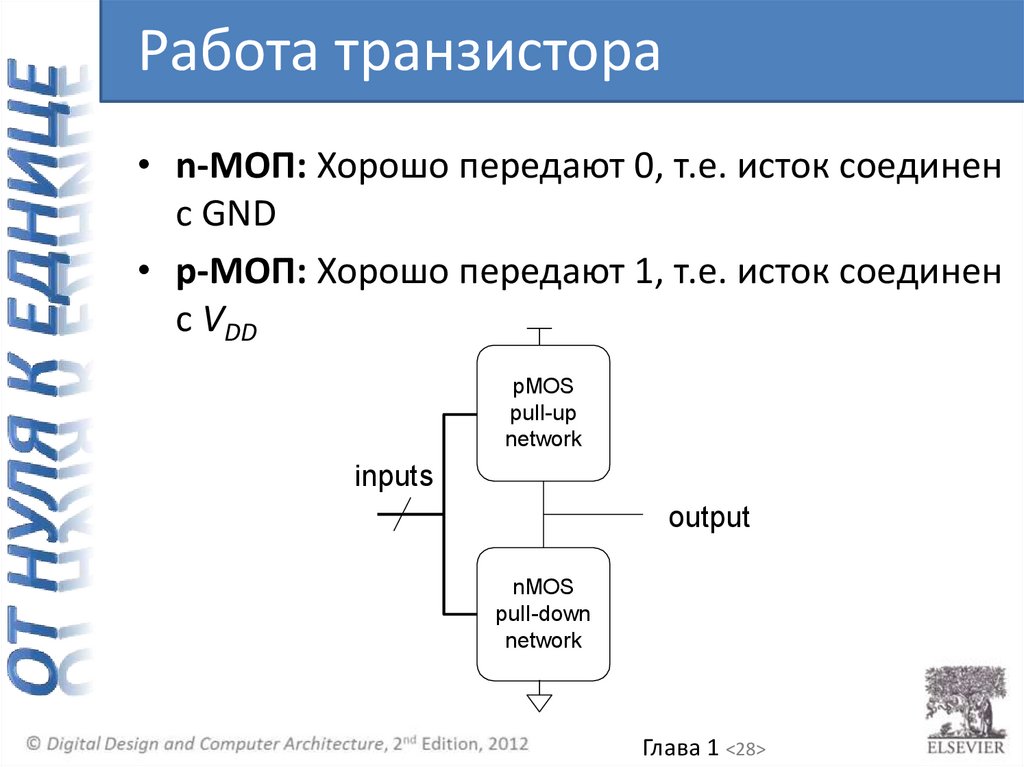

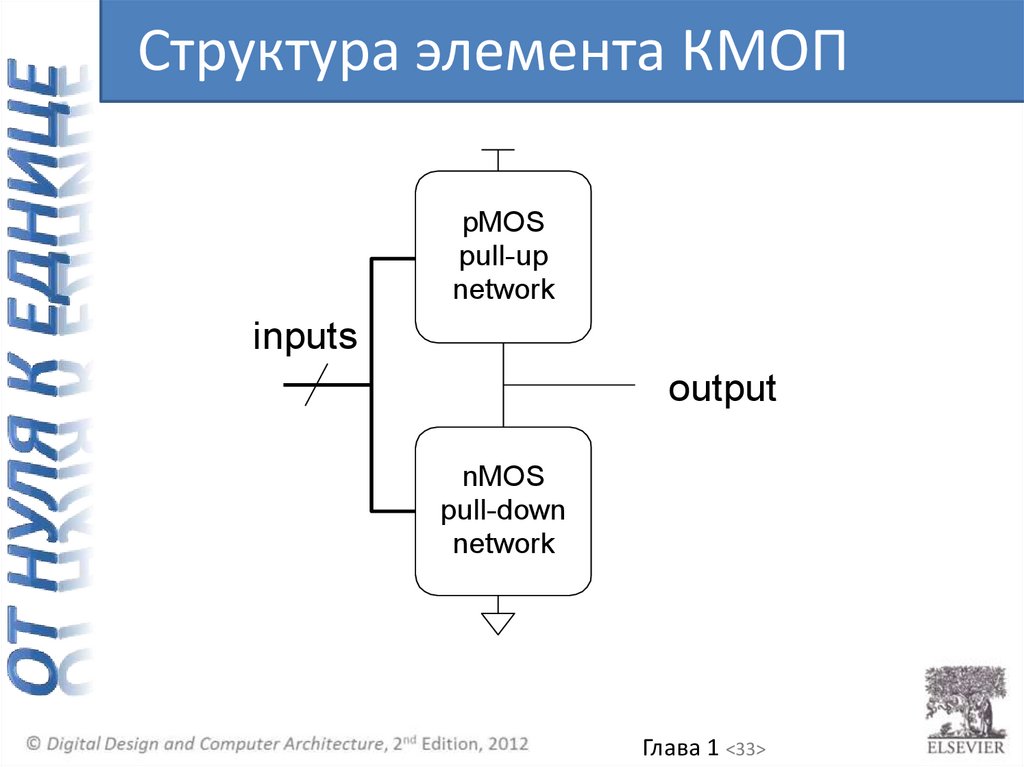

Работа транзистора• n-МОП: Хорошо передают 0, т.е. исток соединен

с GND

• p-МОП: Хорошо передают 1, т.е. исток соединен

с VDD

pMOS

pull-up

network

inputs

output

nMOS

pull-down

network

Глава 1 <28>

29.

Логические элементы КМОП: Логический элементНЕ:

NOT

A

VDD

Y

A

Y=A

A

0

1

Y

1

0

A

P1

Y

N1

GND

P1

N1

Y

0

1

Глава 1 <29>

30.

Логические элементы КМОП: Логический элементНЕ:

NOT

A

VDD

Y

A

Y=A

A

0

1

Y

1

0

P1

Y

N1

GND

A

P1

N1

Y

0

Вкл.

Выкл.

1

1

Выкл.

Вкл.

0

Глава 1 <30>

31.

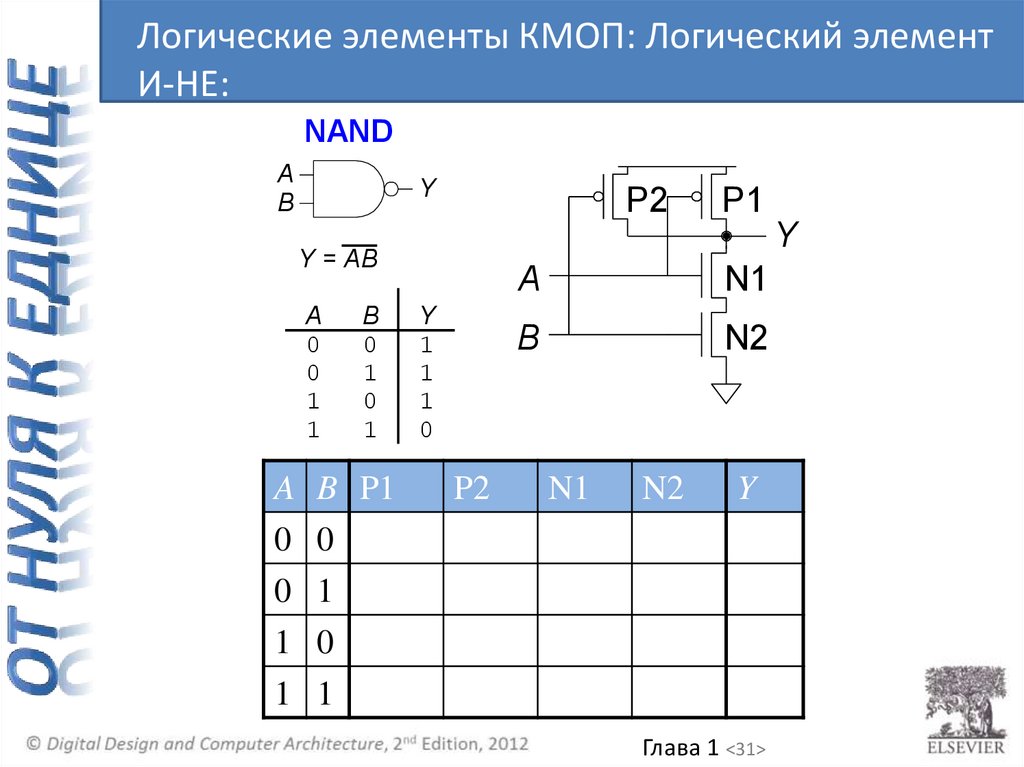

Логические элементы КМОП: Логический элементИ-НЕ:

NAND

A

B

Y

P2

Y

Y = AB

A

0

0

1

1

A

0

0

1

1

B

0

1

0

1

B P1

0

1

0

1

P1

Y

1

1

1

0

P2

A

N1

B

N2

N1

N2

Y

Глава 1 <31>

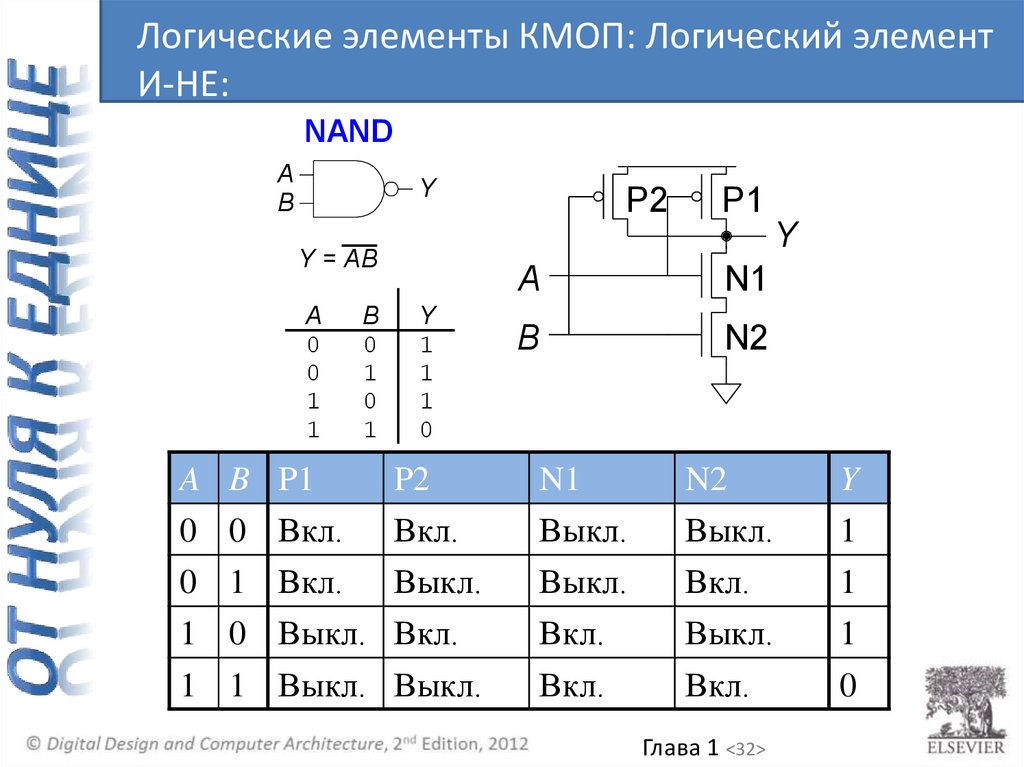

32.

Логические элементы КМОП: Логический элементИ-НЕ:

NAND

A

B

Y

A B P1

B

0

1

0

1

P1

Y

Y = AB

A

0

0

1

1

P2

Y

1

1

1

0

P2

A

N1

B

N2

N1

N2

Y

0 0 Вкл. Вкл.

0 1 Вкл. Выкл.

1 0 Выкл. Вкл.

Выкл.

Выкл.

Вкл.

Выкл.

Вкл.

Выкл.

1

1

1

1 1 Выкл. Выкл.

Вкл.

Вкл.

0

Глава 1 <32>

33.

Структура элемента КМОПpMOS

pull-up

network

inputs

output

nMOS

pull-down

network

Глава 1 <33>

34.

Логический элемент ИЛИ-НЕКак построить элемент ИЛИ-НЕ?

Глава 1 <34>

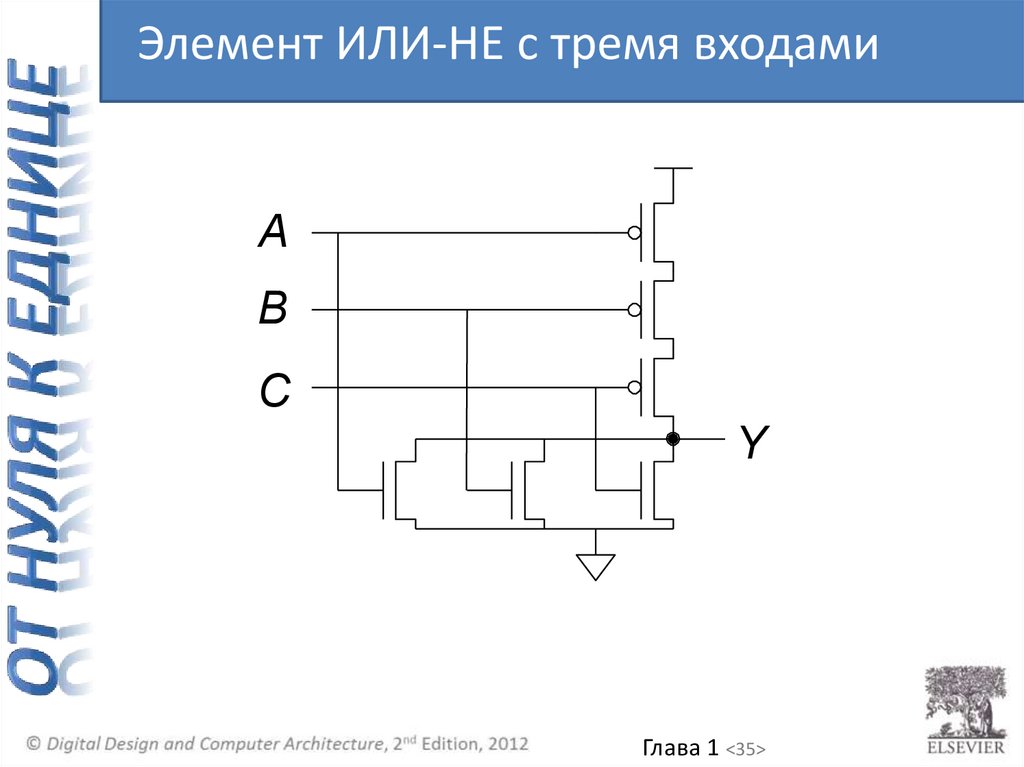

35.

Элемент ИЛИ-НЕ с тремя входамиA

B

C

Y

Глава 1 <35>

36.

Другие элементы КМОПКак построить элемент И с двумя входами?

Глава 1 <36>

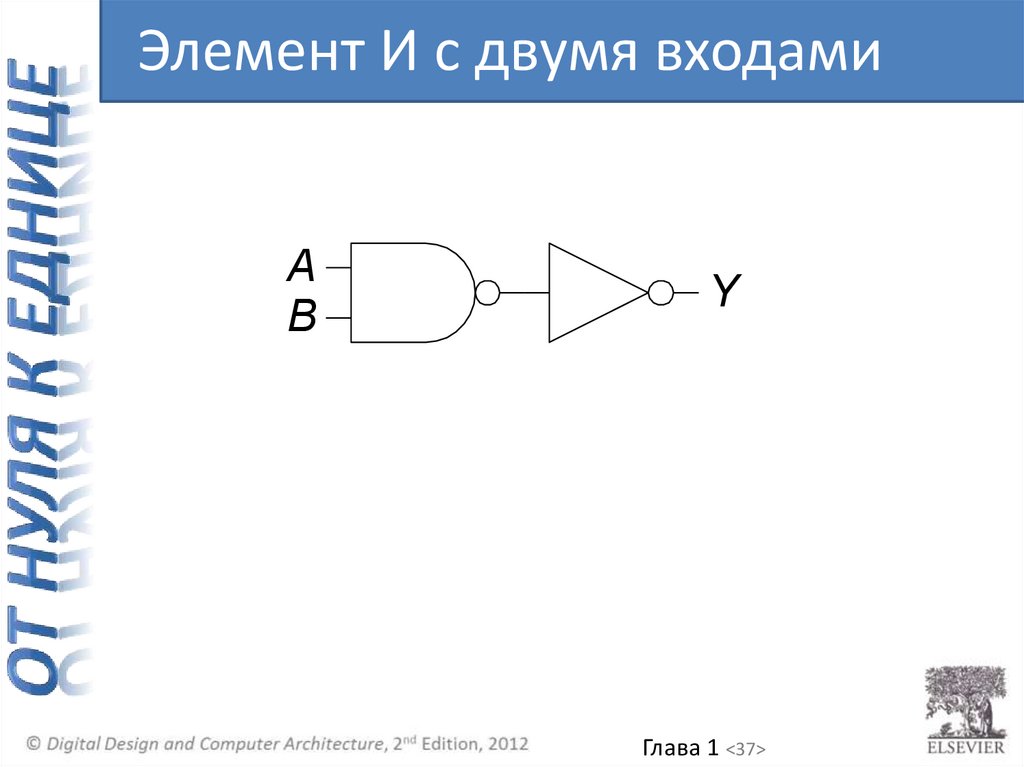

37.

Элемент И с двумя входамиA

B

Y

Глава 1 <37>

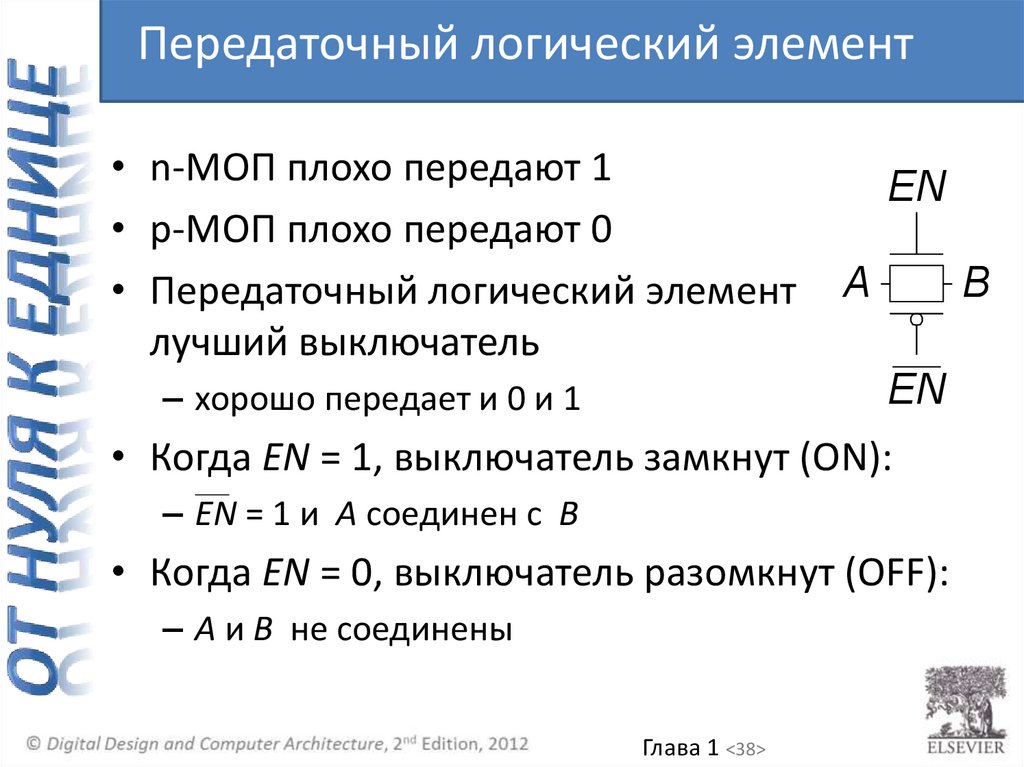

38.

Передаточный логический элемент• n-МОП плохо передают 1

• p-МОП плохо передают 0

• Передаточный логический элемент

лучший выключатель

EN

A

B

EN

– хорошо передает и 0 и 1

• Когда EN = 1, выключатель замкнут (ON):

– EN = 1 и A соединен с B

• Когда EN = 0, выключатель разомкнут (OFF):

– A и B не соединены

Глава 1 <38>

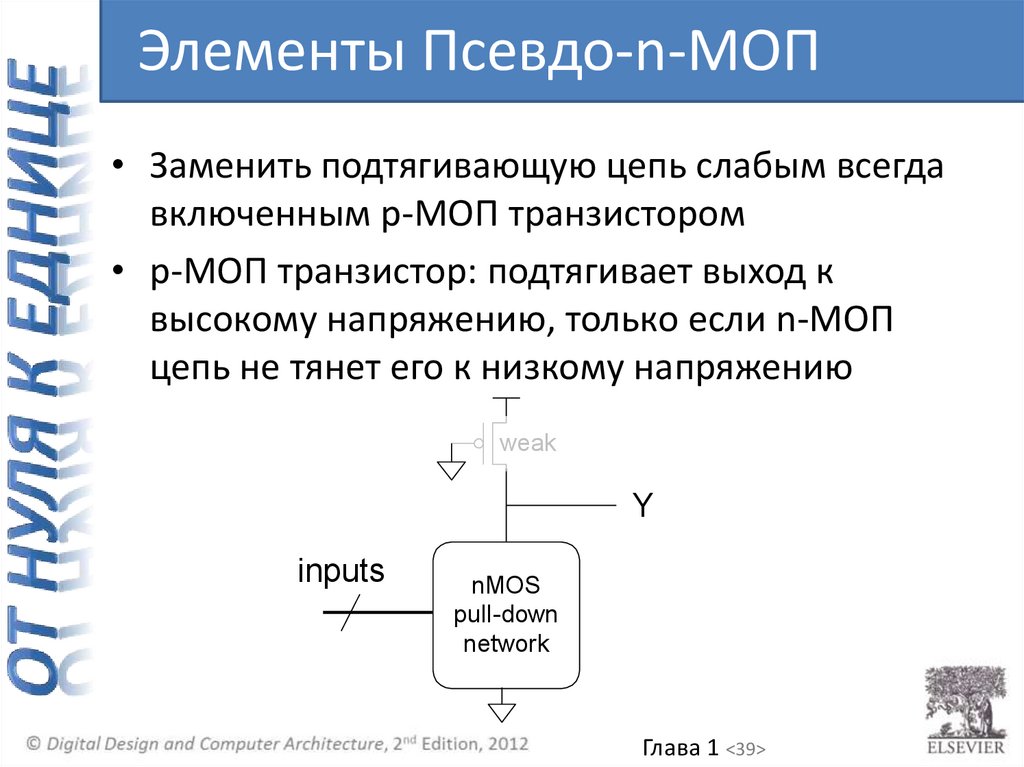

39.

Элементы Псевдо-n-МОП• Заменить подтягивающую цепь слабым всегда

включенным p-МОП транзистором

• p-МОП транзистор: подтягивает выход к

высокому напряжению, только если n-МОП

цепь не тянет его к низкому напряжению

weak

Y

inputs

nMOS

pull-down

network

Глава 1 <39>

40.

Пример элемента Псевдо-n-МОППсевдо-n-МОП элемент NOR4

weak

Y

A

B

C

D

Глава 1 <40>

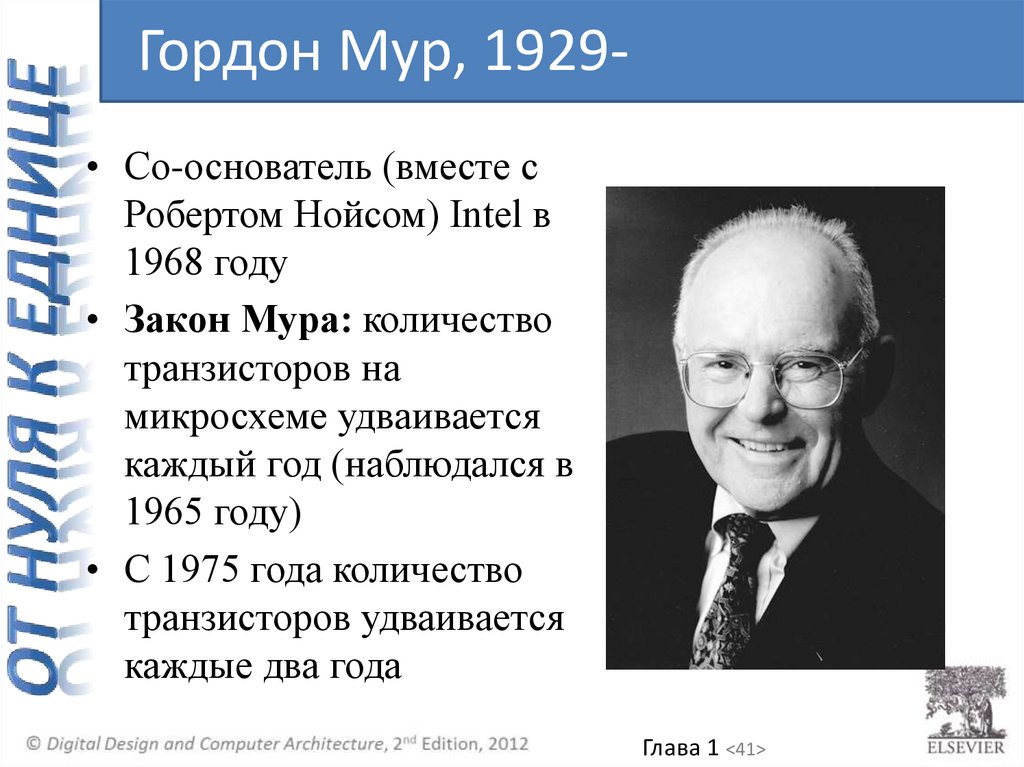

41.

Гордон Мур, 1929• Со-основатель (вместе сРобертом Нойсом) Intel в

1968 году

• Закон Мура: количество

транзисторов на

микросхеме удваивается

каждый год (наблюдался в

1965 году)

• С 1975 года количество

транзисторов удваивается

каждые два года

Глава 1 <41>

42.

Закон Мура:• “Если автомобильная промышленность подчинялась бы

такому же циклу развития, как и компьютерная, Rolls-Royce

стоил бы сейчас $100, на одном галлоне бензина проезжал бы

миллион миль и взрывался бы раз в году. . .”

– Robert Cringley

Глава 1 <42>

43.

Энергопотребление• Мощность = Потребление энергии в

единицу времени

– Динамическая потребляемая мощность

– Статическая потребляемая мощность

Глава 1 <43>

44.

Динамическая потребляемая мощность• Мощность идет на зарядку емкостей

заторов транзисторов

– Для зарядки конденсатора емкостью C до

напряжения VDD необходима энергия CVDD2

– Ток переключается с частотой f: транзистор

переключается (от 0 в 1 или наоборот) с

такой частотой

– Конденсатор заряжается f/2 раз за секунду

(разрядка из 1 в 0 не требует энергии)

• Динамическая потребляемая мощность:

Pdynamic = ½CVDD2f

Глава 1 <44>

45.

Статическая потребляемая мощность• Мощность, потребляемая, когда

элементы не переключаются

• Обусловлена токами покоя (токами

утечки), IDD

• Статическая потребляемая мощность:

Pstatic = IDDVDD

Глава 1 <45>

46.

Пример оценкиэнергопотребления

• Оцените мощность, потребляемую

беспроводным переносным

компьютером

– VDD = 1.2 В

– C = 20 нФ

– f = 1 ГГц

– IDD = 20 мА

Глава 1 <46>

47.

Пример оценкиэнергопотребления

• Оцените мощность, потребляемую

беспроводным переносным компьютером

–

–

–

–

VDD = 1.2 В

C = 20 нФ

f = 1 ГГц

IDD = 20 мА

P = ½CVDD2f + IDDVDD

= ½(20 nF)(1.2 V)2(1 GHz) +

(20 mA)(1.2 V)

= 14.4 W

Глава 1 <47>

Электроника

Электроника