Похожие презентации:

Out-of-Order Pipe. Chapter 2

1.

Chapter 2:Out-of-Order Pipe

McGraw-Hill |

Advanced Computer Architecture. Smruti R. Sarangi

1

2.

Background Required to Understand this ChapterAssembly Languages

Basic Processor Design

Basic Pipeline Design

http://www.cse.iitd.ac.in/~srsarangi/archbooksoft.html

McGraw-Hill | Advanced Computer Architecture. Smruti R. Sarangi

2

3.

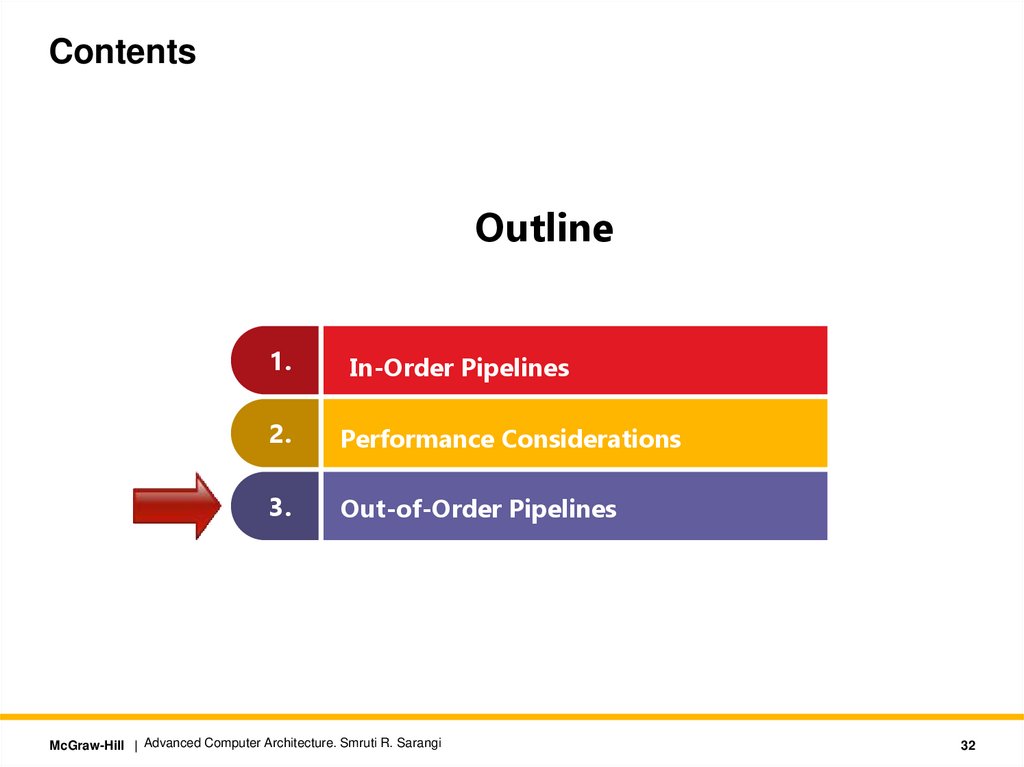

Outline1.

In-Order Pipelines

2.

Performance Considerations

3.

Out-of-Order Pipelines

McGraw-Hill | Advanced Computer Architecture. Smruti R. Sarangi

3

4.

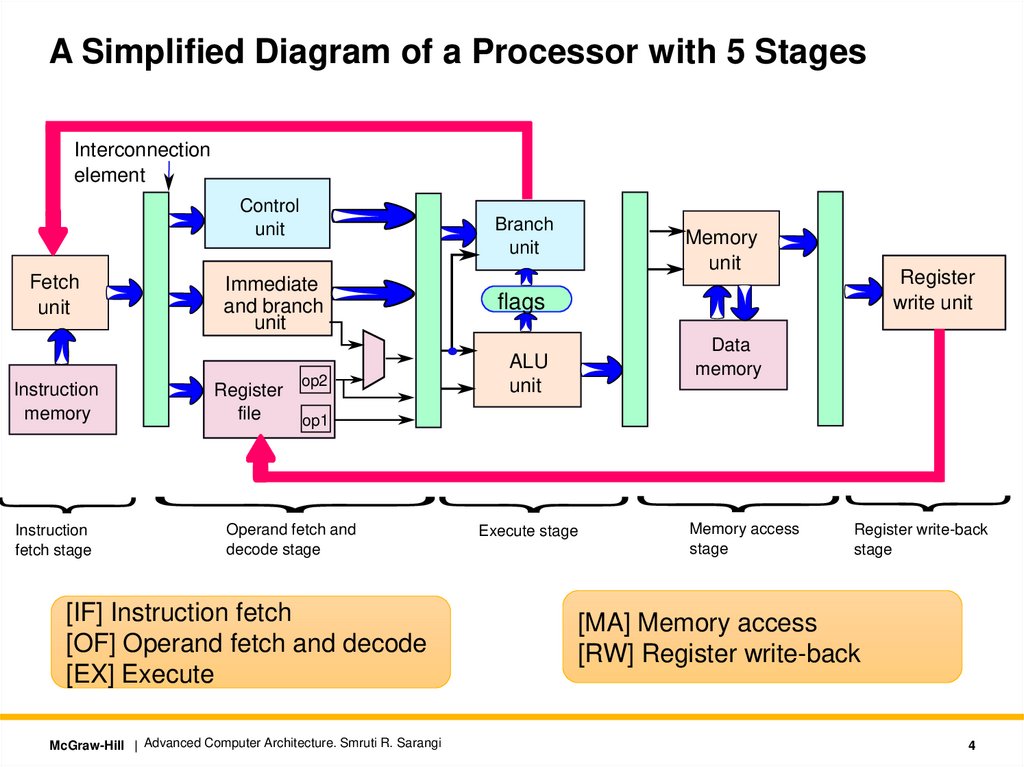

A Simplified Diagram of a Processor with 5 StagesInterconnection

element

Control

unit

Fetch

unit

Instruction

memory

Instruction

fetch stage

Branch

unit

Immediate

and branch

unit

flags

op2

ALU

unit

Register

file

Memory

unit

Register

write unit

Data

memory

op1

Operand fetch and

decode stage

[IF] Instruction fetch

[OF] Operand fetch and decode

[EX] Execute

McGraw-Hill | Advanced Computer Architecture. Smruti R. Sarangi

Execute stage

Memory access

stage

Register write-back

stage

[MA] Memory access

[RW] Register write-back

4

5.

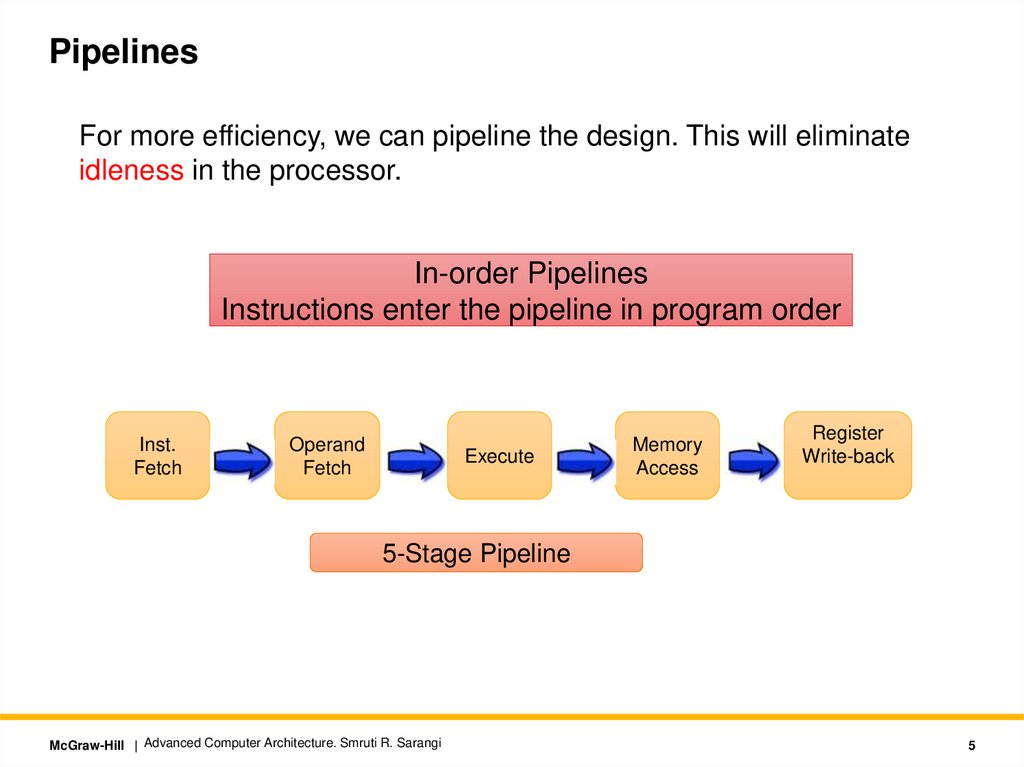

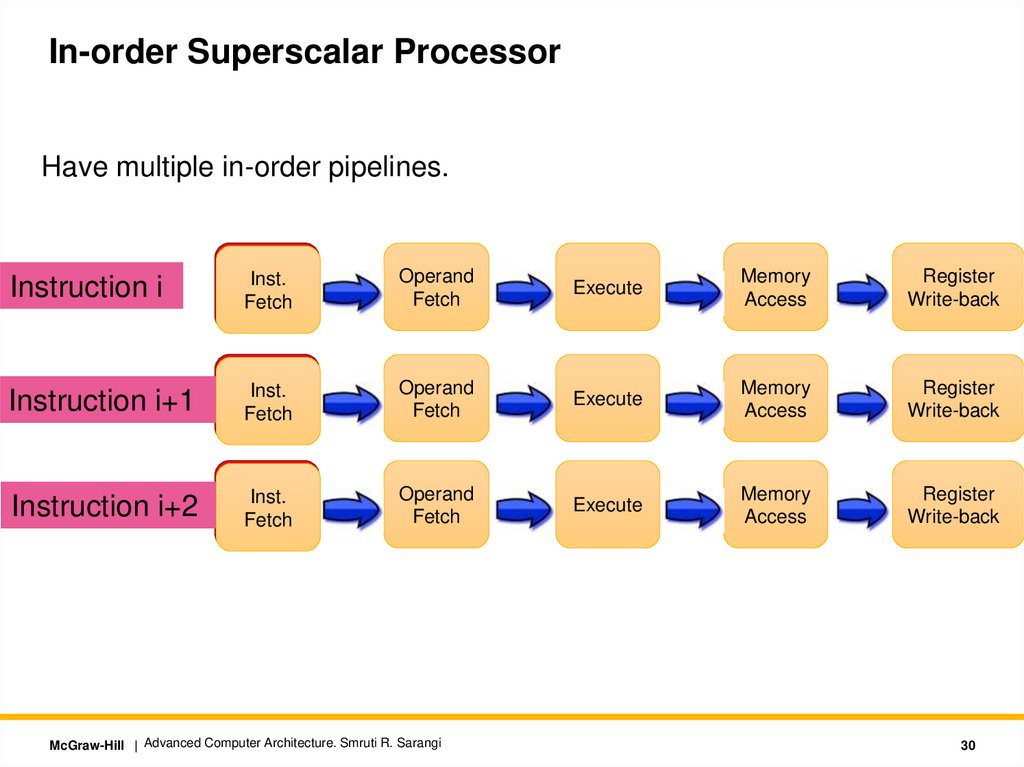

PipelinesFor more efficiency, we can pipeline the design. This will eliminate

idleness in the processor.

In-order Pipelines

Instructions enter the pipeline in program order

Inst.

Fetch

Operand

Fetch

Execute

Memory

Access

Register

Write-back

5-Stage Pipeline

McGraw-Hill | Advanced Computer Architecture. Smruti R. Sarangi

5

6.

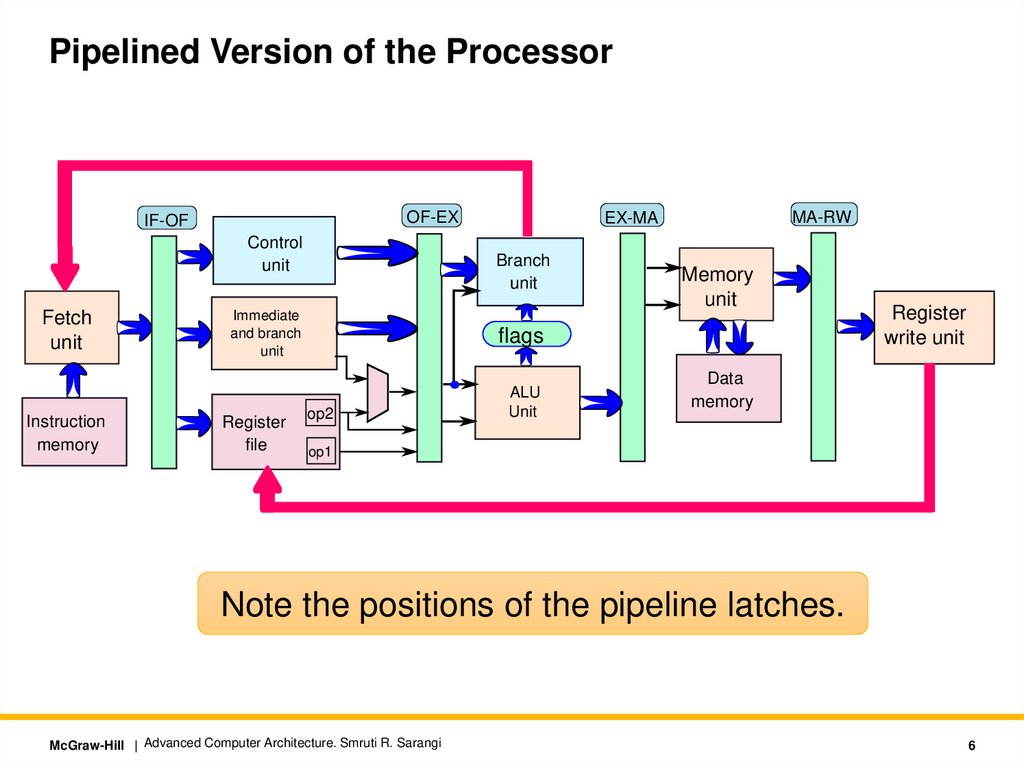

Pipelined Version of the ProcessorOF-EX

IF-OF

Control

unit

Fetch

unit

Instruction

memory

Branch

unit

Immediate

and branch

unit

Register

file

MA-RW

EX-MA

Memory

unit

flags

op2

ALU

Unit

Register

write unit

Data

memory

op1

Note the positions of the pipeline latches.

McGraw-Hill | Advanced Computer Architecture. Smruti R. Sarangi

6

7.

Problems with In-order PipelinesInst.

Fetch

Operand

Fetch

Execute

Memory

Access

Register

Write-back

Hazards

• Structural Hazards Two instructions vie for the same resource

(NOT possible in simple 5-stage pipelines)

• Data Hazards An instruction stands to read or write the wrong data.

• Control Hazards Instructions are fetched from the wrong path of the

branch

McGraw-Hill | Advanced Computer Architecture. Smruti R. Sarangi

7

8.

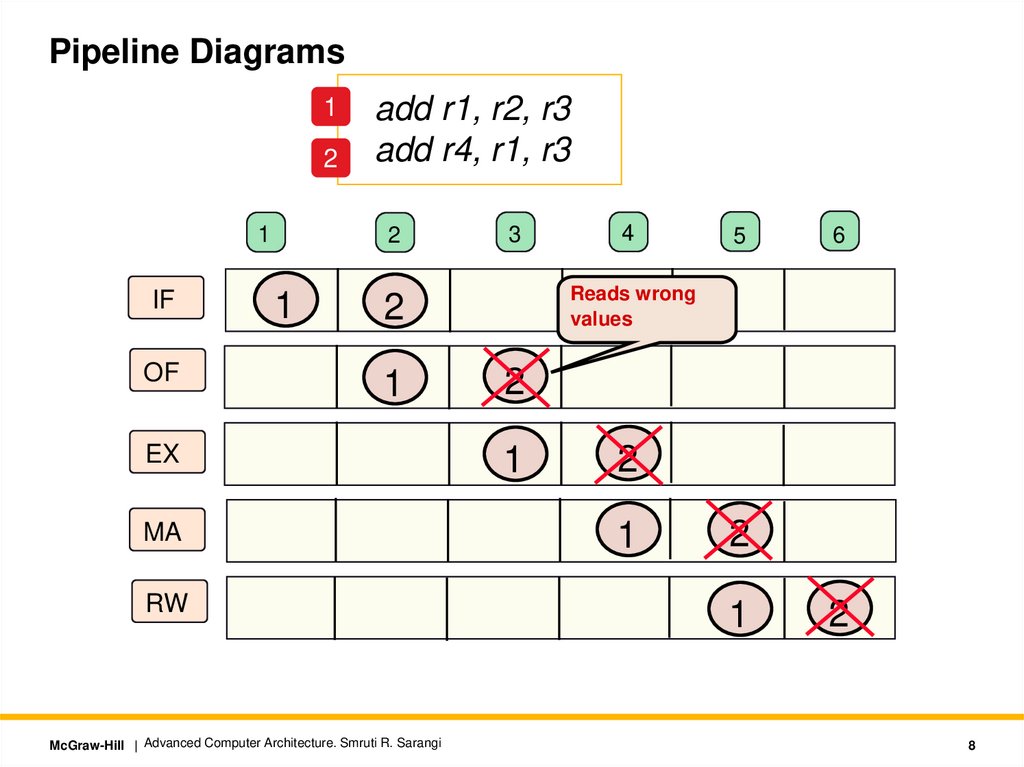

Pipeline Diagrams1

2

1

IF

OF

add r1, r2, r3

add r4, r1, r3

2

1

3

EX

MA

RW

McGraw-Hill | Advanced Computer Architecture. Smruti R. Sarangi

5

6

Reads wrong

values

2

1

4

2

1

2

1

2

1

2

8

9.

Pipeline Interlocks1

IF

OF

1

2

3

4

5

6

2

3

3

3

3

1

2

2

2

2

7

3

Pipeline

EX

2

1

bubble

1

MA

RW

1

An interlock inserts a nop instruction (bubble) in the pipeline

McGraw-Hill | Advanced Computer Architecture. Smruti R. Sarangi

9

10.

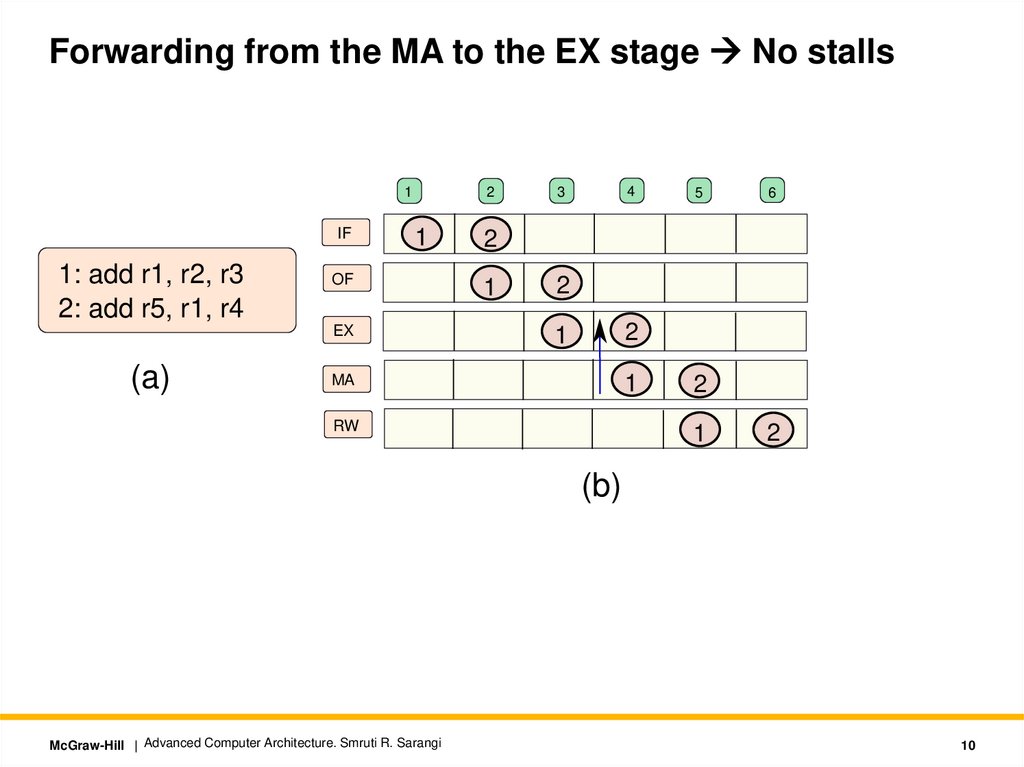

Forwarding from the MA to the EX stage No stalls1

IF

1: add r1, r2, r3

2: add r5, r1, r4

2

1

OF

EX

(a)

4

3

5

6

2

1

2

2

1

1

MA

RW

2

1

2

(b)

McGraw-Hill | Advanced Computer Architecture. Smruti R. Sarangi

10

11.

Forwarding MultiplexersLatch

EX stage

MA stage

Input 1

Memory

ALU

Input 2

access unit

Forwarded input

McGraw-Hill | Advanced Computer Architecture. Smruti R. Sarangi

11

12.

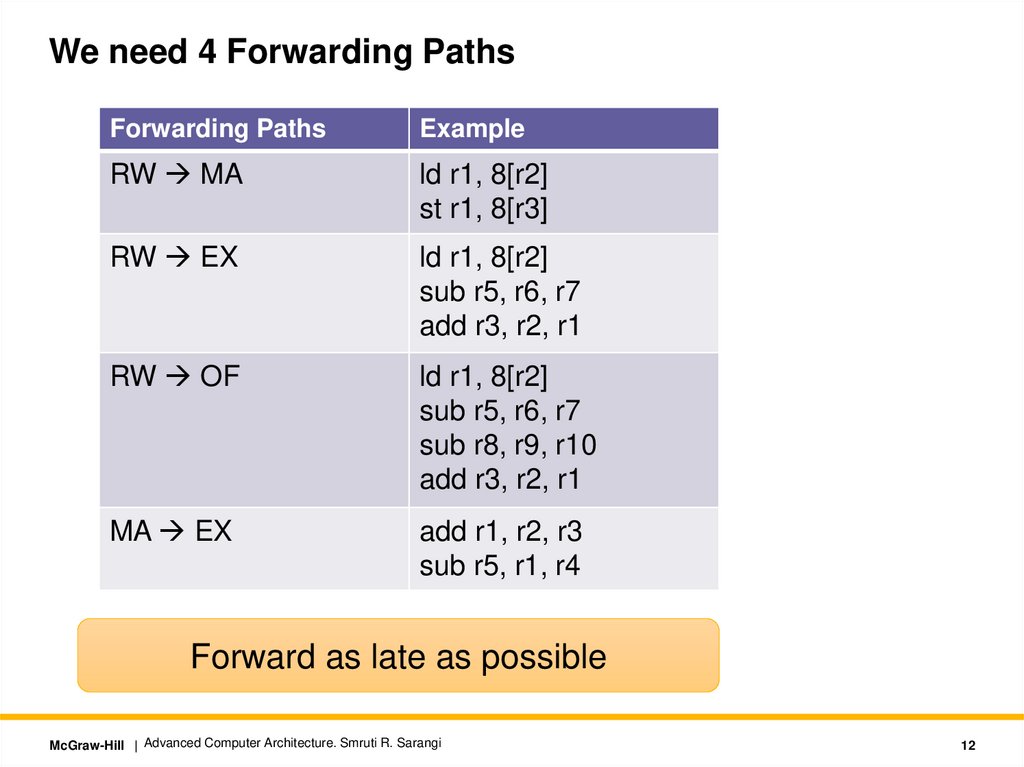

We need 4 Forwarding PathsForwarding Paths

Example

RW MA

ld r1, 8[r2]

st r1, 8[r3]

RW EX

ld r1, 8[r2]

sub r5, r6, r7

add r3, r2, r1

RW OF

ld r1, 8[r2]

sub r5, r6, r7

sub r8, r9, r10

add r3, r2, r1

MA EX

add r1, r2, r3

sub r5, r1, r4

Forward as late as possible

McGraw-Hill | Advanced Computer Architecture. Smruti R. Sarangi

12

13.

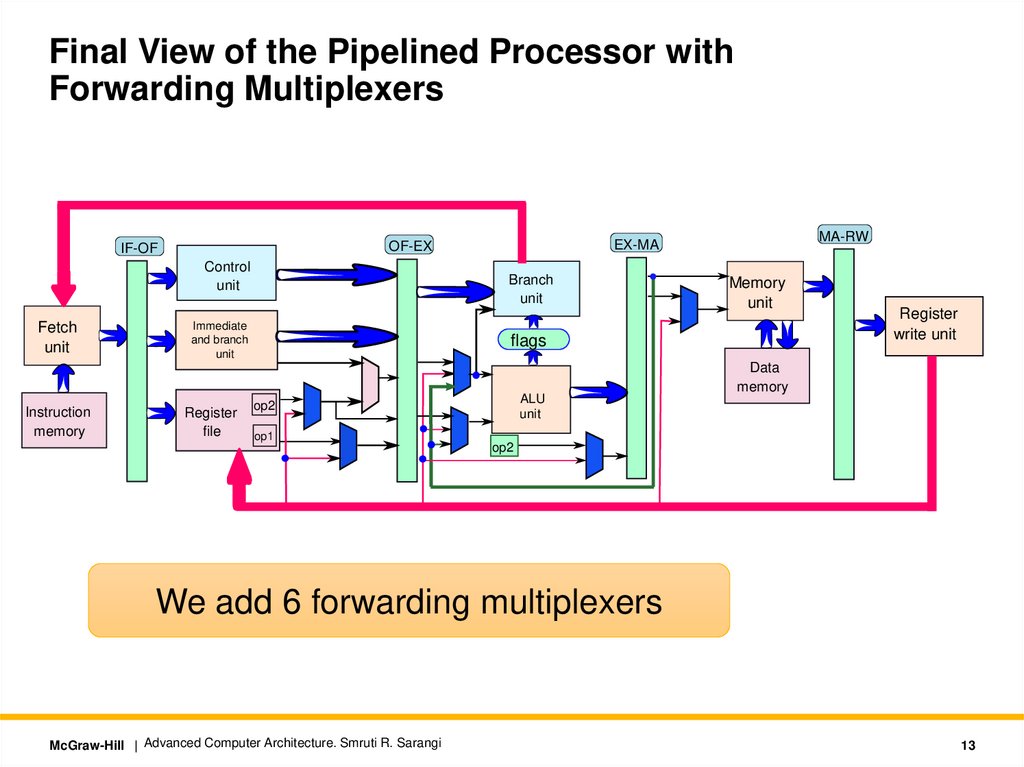

Final View of the Pipelined Processor withForwarding Multiplexers

Control

unit

Fetch

unit

Instruction

memory

Branch

unit

Immediate

and branch

unit

Register

file

MA-RW

EX-MA

OF-EX

IF-OF

Memory

unit

flags

ALU

unit

op2

Register

write unit

Data

memory

op1

op2

We add 6 forwarding multiplexers

McGraw-Hill | Advanced Computer Architecture. Smruti R. Sarangi

13

14.

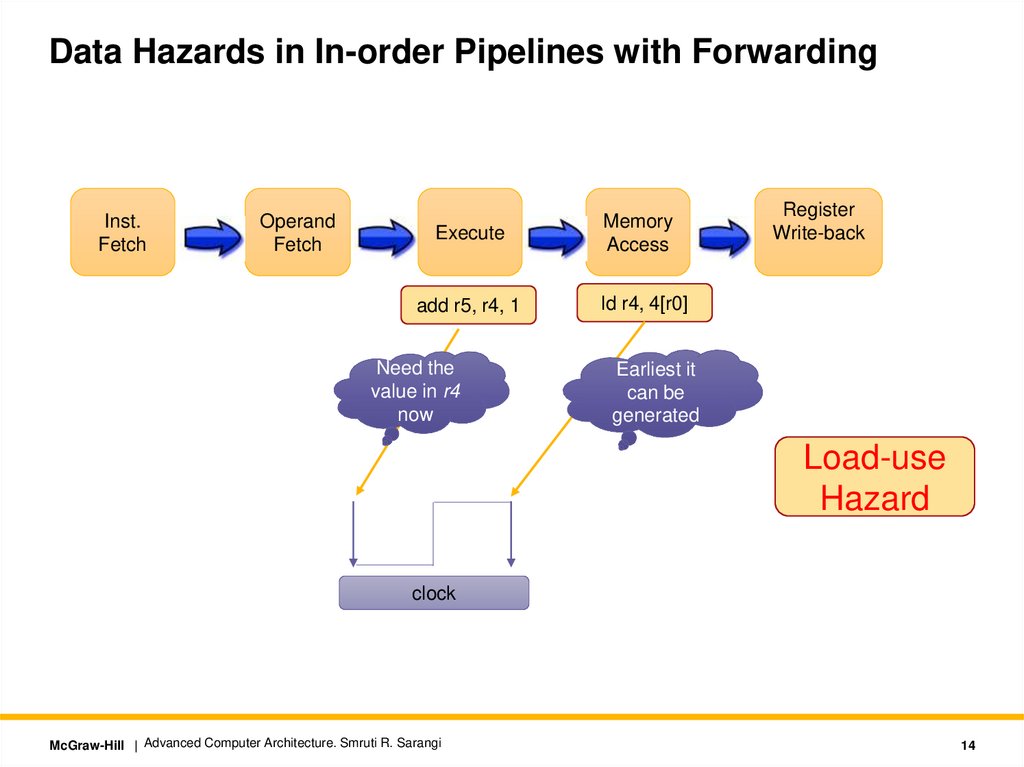

Data Hazards in In-order Pipelines with ForwardingInst.

Fetch

Operand

Fetch

Execute

Memory

Access

add r5, r4, 1

ld r4, 4[r0]

Need the

value in r4

now

Register

Write-back

Earliest it

can be

generated

Load-use

Hazard

clock

McGraw-Hill | Advanced Computer Architecture. Smruti R. Sarangi

14

15.

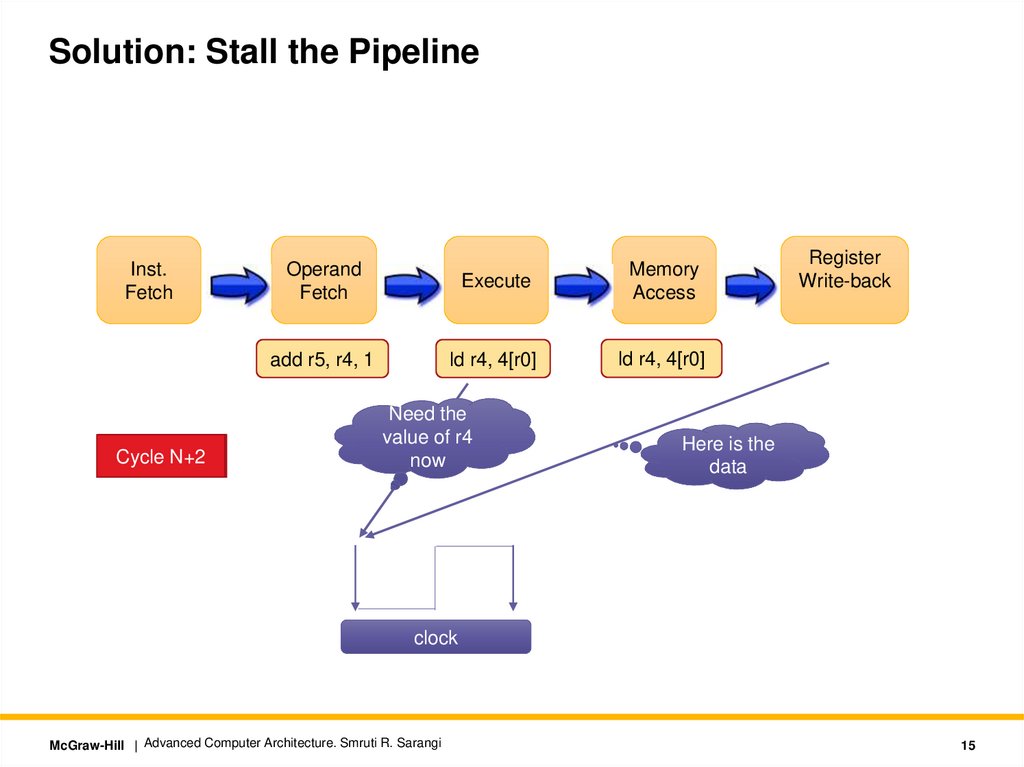

Solution: Stall the PipelineInst.

Fetch

Cycle

CycleN+2

N+1

N

Operand

Fetch

Execute

Memory

Access

add r5, r4, 1

ld r4, 4[r0]

ld r4, 4[r0]

Need the

value of r4

now

Register

Write-back

Here is the

data

clock

McGraw-Hill | Advanced Computer Architecture. Smruti R. Sarangi

15

16.

Control HazardsInst.

Fetch

Operand

Fetch

add

sub

beq r5,

r1,

.label

r6,

r2, r7

r3

beq .label

Cancel these

instructions

Execute

Memory

Access

Register

Write-back

We know the status of

the branch now.

Assume it is taken.

Two instruction slots are wasted

McGraw-Hill | Advanced Computer Architecture. Smruti R. Sarangi

16

17.

Outline1.

In-Order Pipelines

2.

Performance Considerations

3.

Out-of-Order Pipelines

McGraw-Hill | Advanced Computer Architecture. Smruti R. Sarangi

17

18.

Performance Equation - IIs Computer A faster that Computer B

• Wrong Answers:

• More is the clock speed, faster is the computer

• More is the RAM, faster is the computer

What does it mean for computer A to be faster than computer B

Short Answer: NOTHING

Performance is always with respect to a program. You can say

that a certain program runs faster on computer A as compared

to computer B.

McGraw-Hill | Advanced Computer Architecture. Smruti R. Sarangi

18

19.

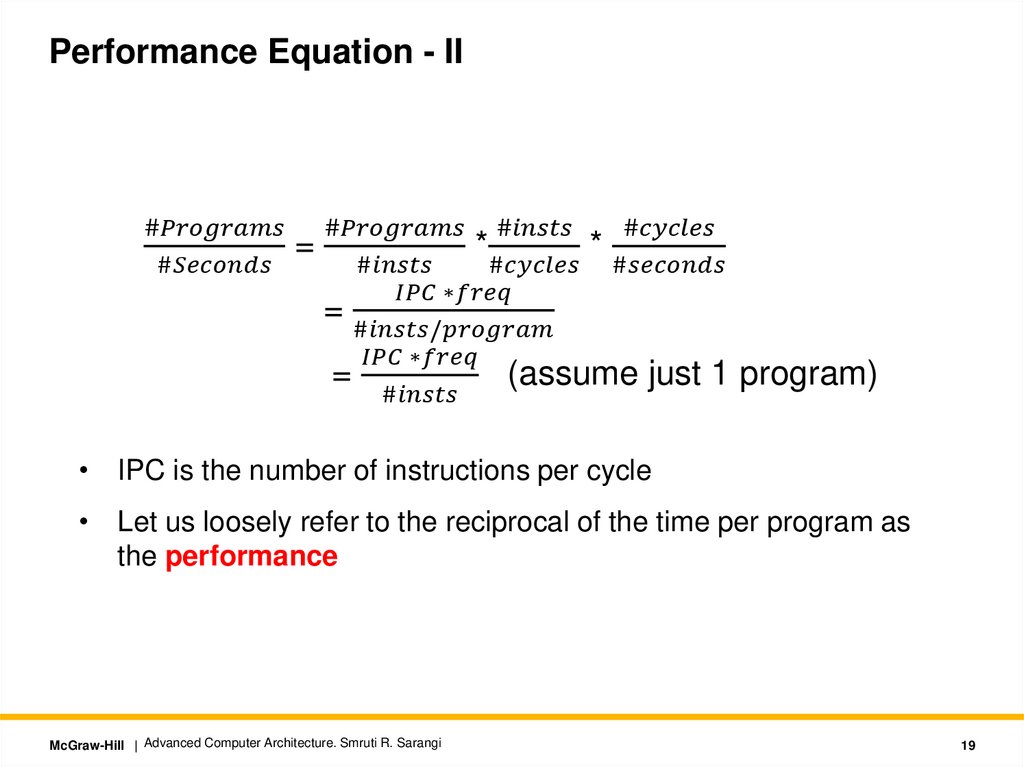

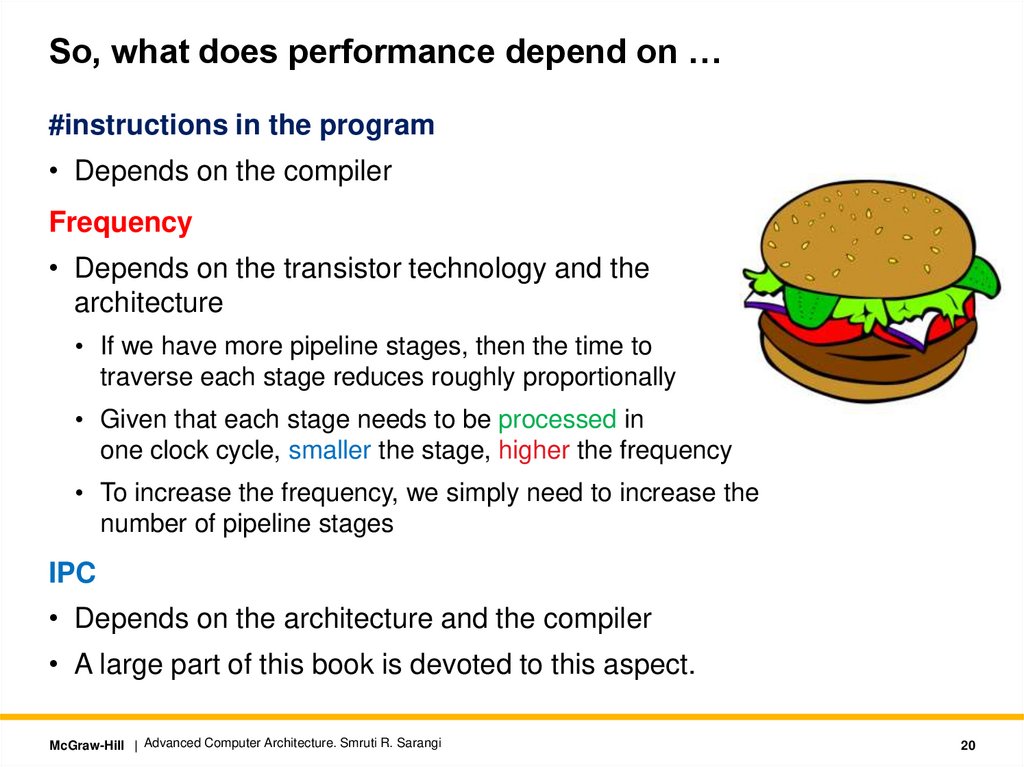

Performance Equation - II#

Электроника

Электроника