Похожие презентации:

Проектирование систем автоматизации. Проектная компоновка УВК

1. ПРОЕКТИРОВАНИЕ СИСТЕМ АВТОМАТИЗАЦИИ модуль 5. Проектная компоновка УВК

2.

Шевкопляс Б.В. Микропроцессорные структуры.Инженерные решения: Спрапвочник. – М.: Радио и

связь, 1990. – 512 с.

Гук М. Ю. Аппаратные средства IBMРС. Энциклопедия.

З-е изд. —СПб.: Питер, 2006. —1072 с.

Гук М. Интерфейсы ПК.

Справочник. — СПб: Питер Ком,

1999.

Скотт Мюллер.Модернизация и ремонт ПК. -19-е издание.

М.: Вильямс, 2011. – 1072 с.

3.

1. СОСТАВ ТЕХНИЧЕСКОГО ОБЕСПЕЧЕНИЯ АСУ ТПД

Д

Д

ИМ

ИМ

ИМ

УСОП

УСО

ВК

УВК

Д – датчики (технологические измерители)

ИМ – исполнительные механизмы

ВК – вычислительный комплекс

УСО – устройства связи с объектом

УВК – управляющий вычислительный комплекс

1

4.

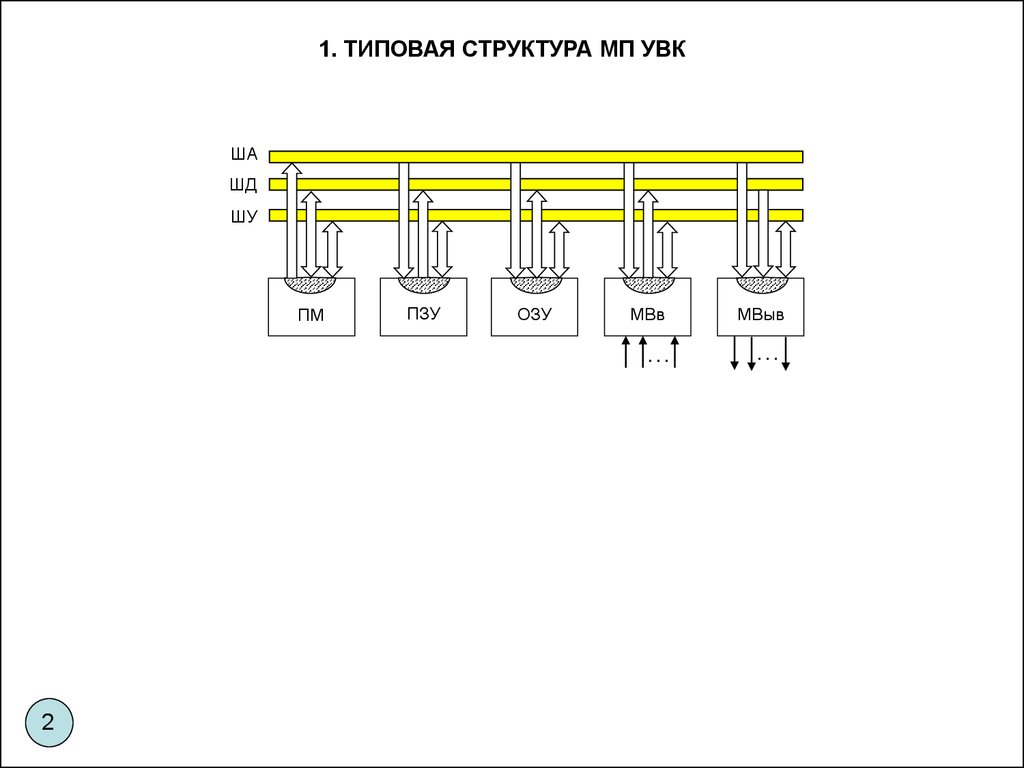

1. ТИПОВАЯ СТРУКТУРА МП УВКШA

ШД

ШУ

ПМ

ПЗУ

ОЗУ

МВв

…

2

МВыв

…

5.

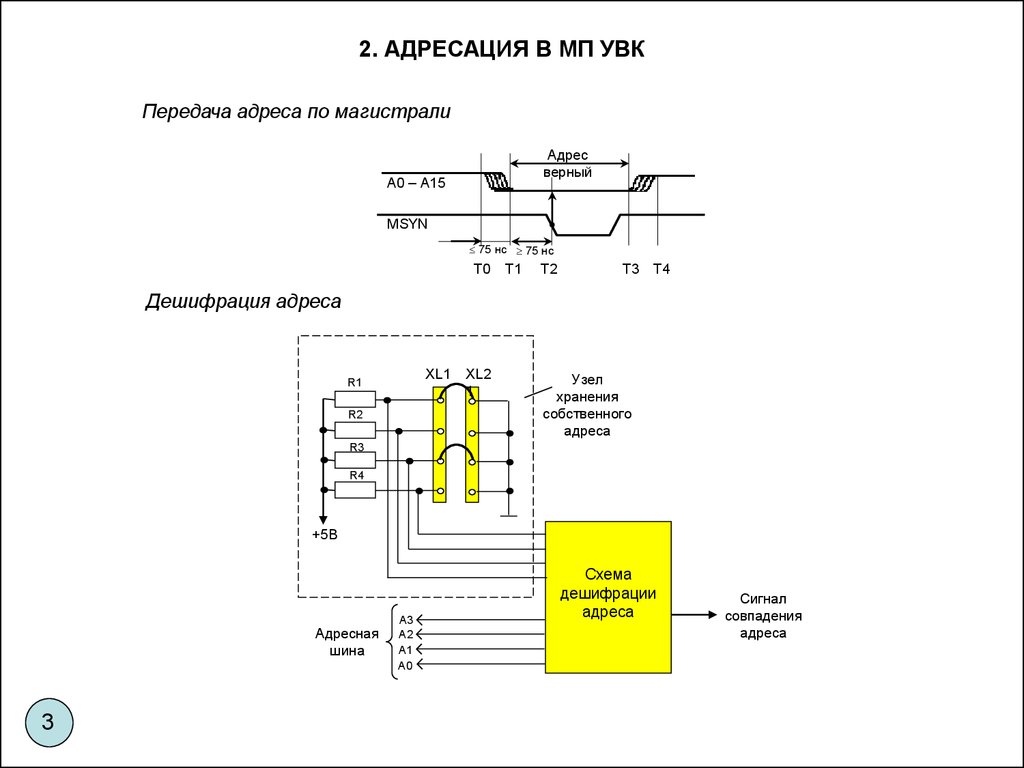

2. АДРЕСАЦИЯ В МП УВКПередача адреса по магистрали

Адрес

верный

A0 – A15

MSYN

75 нс 75 нс

Т0

Т1

Т2

Т3 Т4

Дешифрация адреса

ХL1

R1

R2

ХL2

1

Узел

хранения

собственного

адреса

R3

R4

+5В

Адресная

шина

3

А3

А2

А1

А0

Схема

дешифрации

адреса

Сигнал

совпадения

адреса

6.

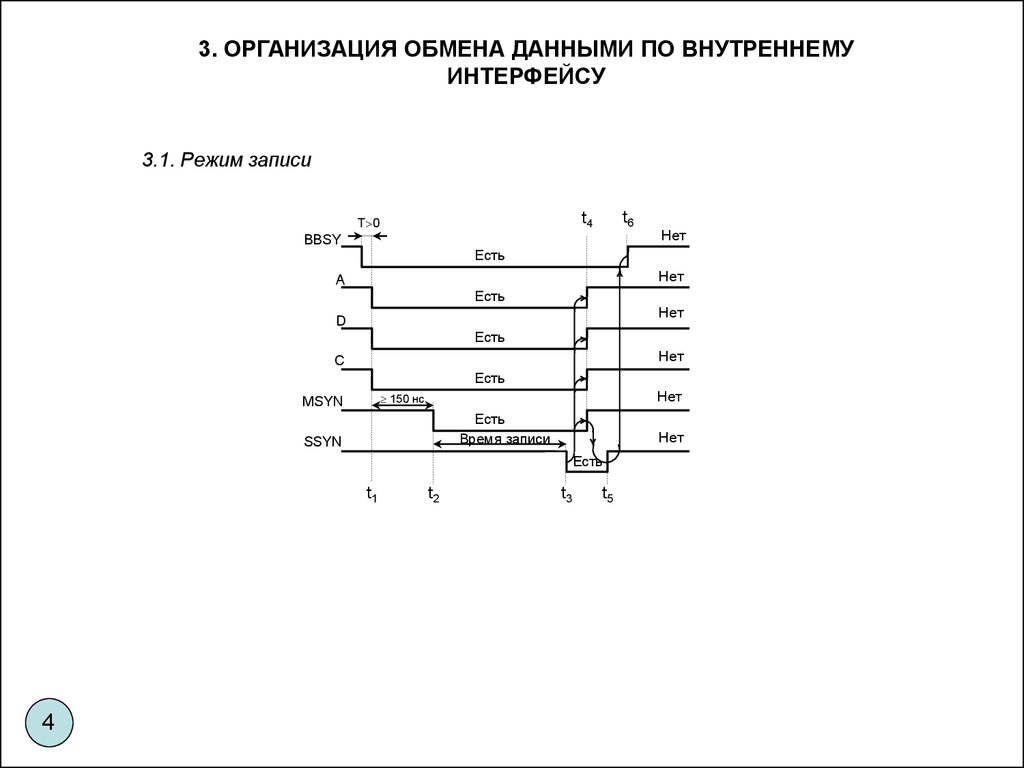

3. ОРГАНИЗАЦИЯ ОБМЕНА ДАННЫМИ ПО ВНУТРЕННЕМУИНТЕРФЕЙСУ

3.1. Режим записи

t6

t4

Т 0

BBSY

Нет

Есть

Нет

A

Есть

Нет

D

Есть

Нет

С

Есть

Нет

150 нс

MSYN

Есть

Время записи

SSYN

Нет

Есть

t1

4

t2

t3

t5

7.

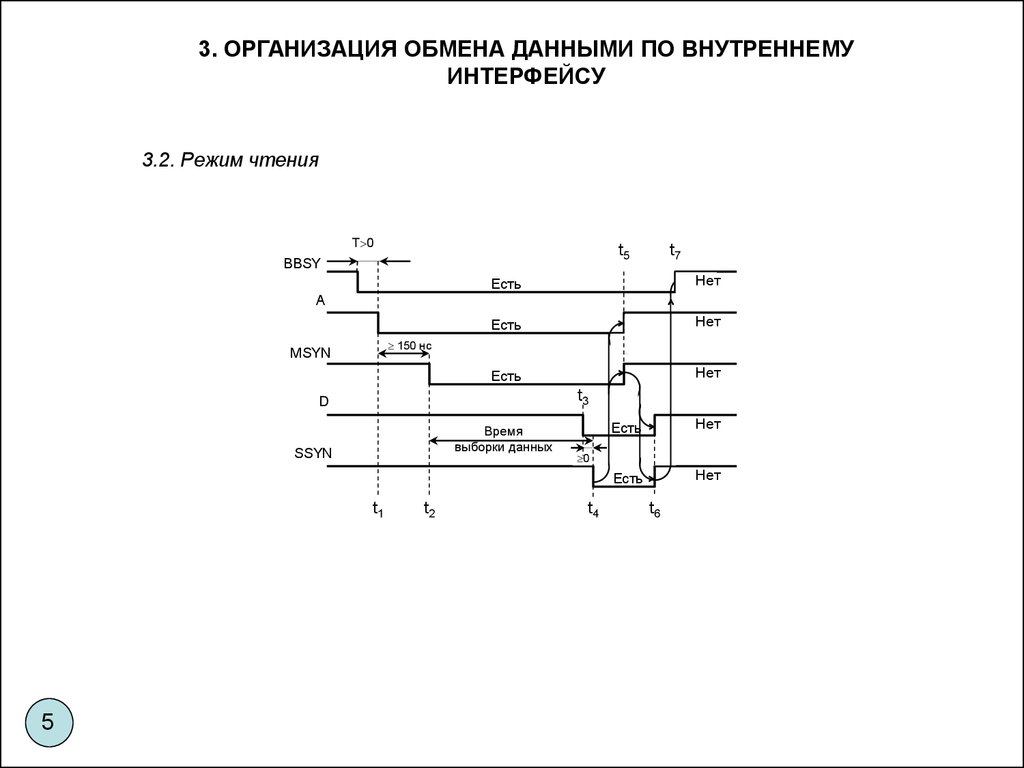

3. ОРГАНИЗАЦИЯ ОБМЕНА ДАННЫМИ ПО ВНУТРЕННЕМУИНТЕРФЕЙСУ

3.2. Режим чтения

Т 0

t5

BBSY

t7

Есть

Нет

Есть

Нет

Есть

Нет

A

150 нс

MSYN

t3

D

Время

выборки данных

SSYN

t1

5

t2

Есть

Нет

Есть

Нет

0

t4

t6

8.

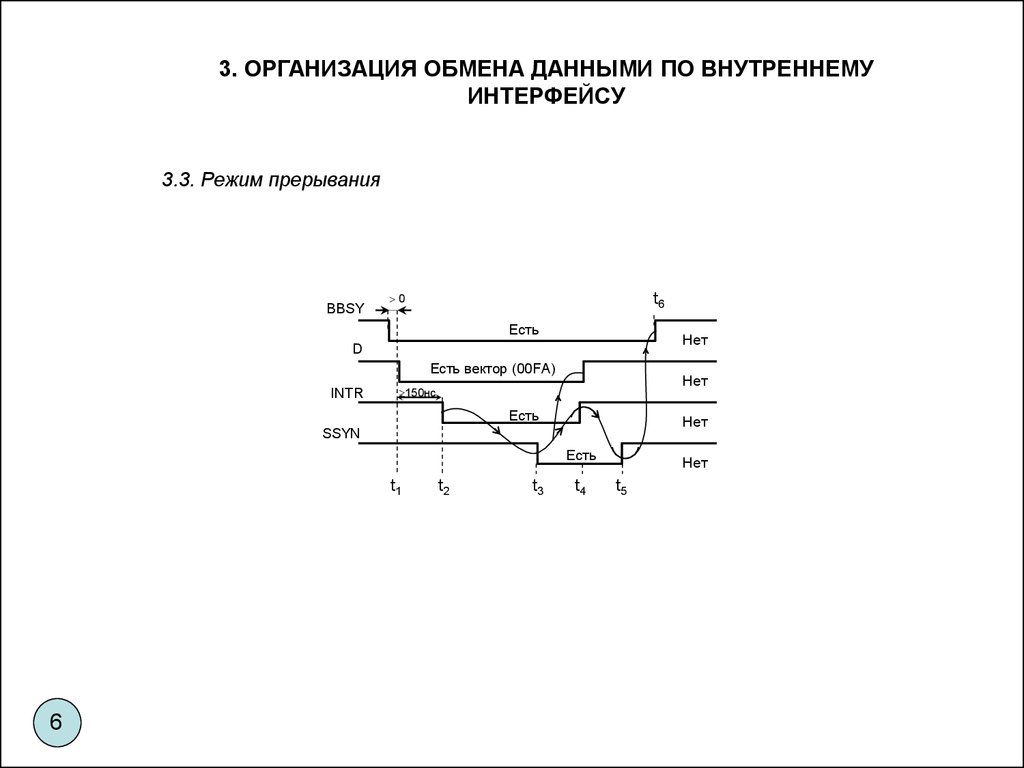

3. ОРГАНИЗАЦИЯ ОБМЕНА ДАННЫМИ ПО ВНУТРЕННЕМУИНТЕРФЕЙСУ

3.3. Режим прерывания

BBSY

0

t6

Есть

Нет

D

Есть вектор (00FA)

INTR

Нет

150нс

Есть

Нет

SSYN

Есть

t1

6

t2

t3

t4

Нет

t5

9.

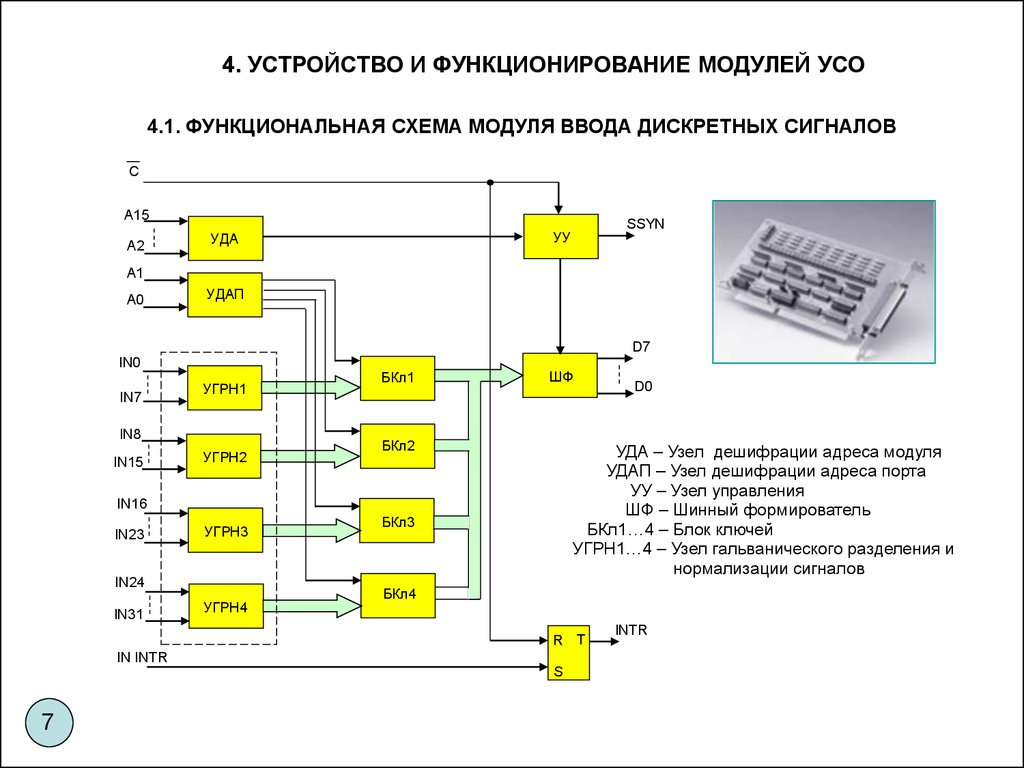

4. УСТРОЙСТВО И ФУНКЦИОНИРОВАНИЕ МОДУЛЕЙ УСО4.1. ФУНКЦИОНАЛЬНАЯ СХЕМА МОДУЛЯ ВВОДА ДИСКРЕТНЫХ СИГНАЛОВ

C

A15

A2

SSYN

УУ

УДА

A1

A0

УДАП

D7

IN0

IN7

УГРН1

IN8

IN15

УГРН2

БКл1

ШФ

БКл2

УДА – Узел дешифрации адреса модуля

УДАП – Узел дешифрации адреса порта

УУ – Узел управления

ШФ – Шинный формирователь

БКл1…4 – Блок ключей

УГРН1…4 – Узел гальванического разделения и

нормализации сигналов

IN16

IN23

УГРН3

IN24

IN31

УГРН4

БКл3

БКл4

R T

IN INTR

S

7

D0

INTR

10.

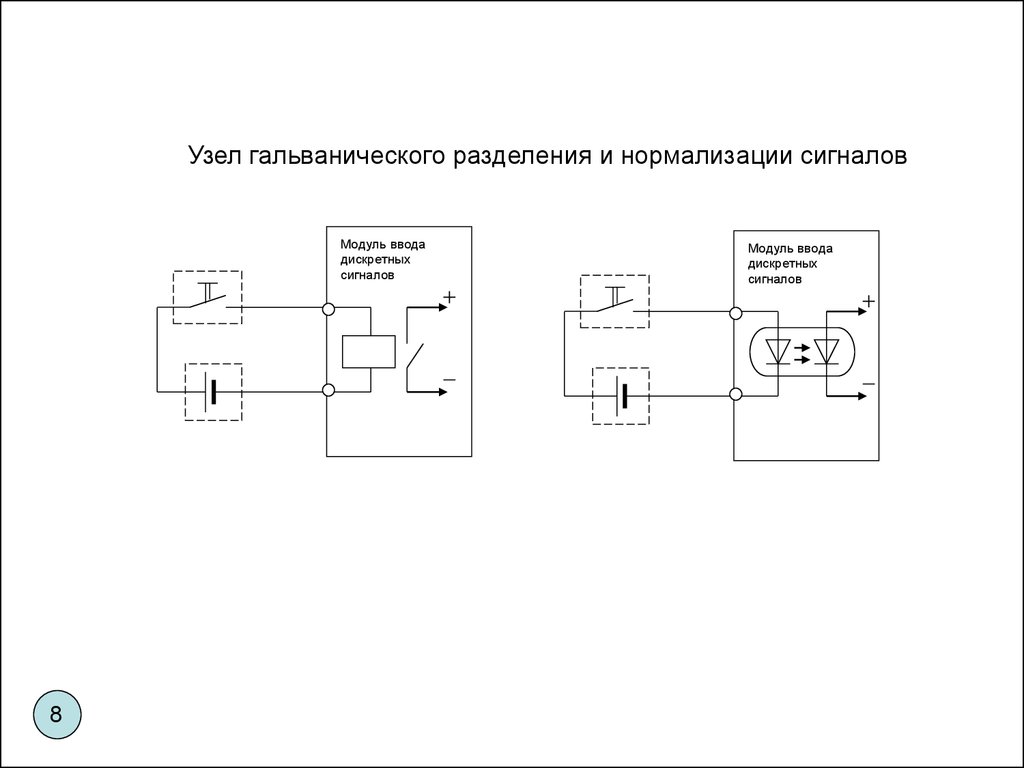

Узел гальванического разделения и нормализации сигналовМодуль ввода

дискретных

сигналов

8

Модуль ввода

дискретных

сигналов

11.

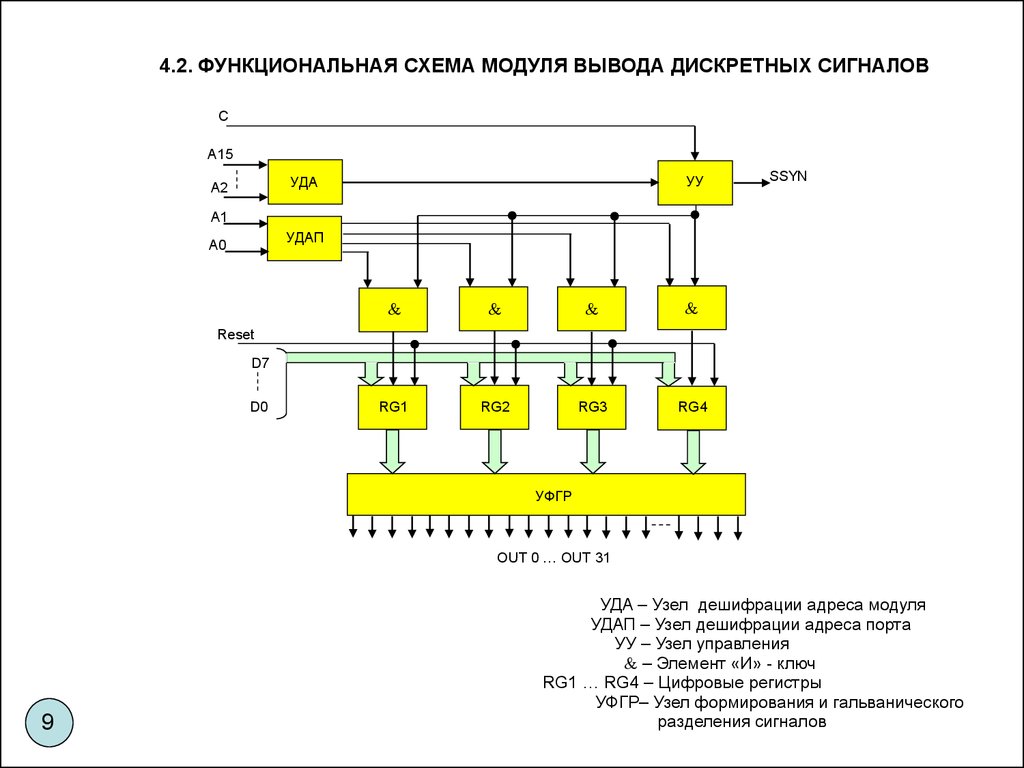

4.2. ФУНКЦИОНАЛЬНАЯ СХЕМА МОДУЛЯ ВЫВОДА ДИСКРЕТНЫХ СИГНАЛОВC

A15

УУ

УДА

A2

SSYN

A1

УДАП

A0

RG1

RG2

RG3

RG4

Reset

D7

D0

УФГР

OUT 0 … OUT 31

9

УДА – Узел дешифрации адреса модуля

УДАП – Узел дешифрации адреса порта

УУ – Узел управления

– Элемент «И» - ключ

RG1 … RG4 – Цифровые регистры

УФГР– Узел формирования и гальванического

разделения сигналов

12.

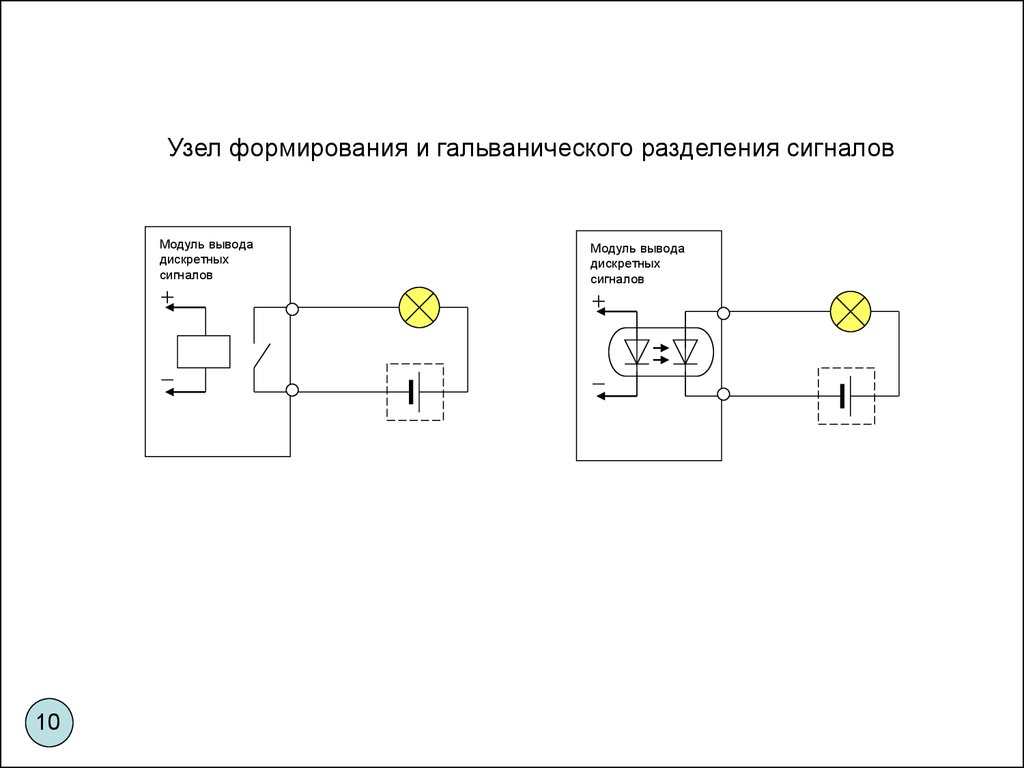

Узел формирования и гальванического разделения сигналовМодуль вывода

дискретных

сигналов

10

Модуль вывода

дискретных

сигналов

13.

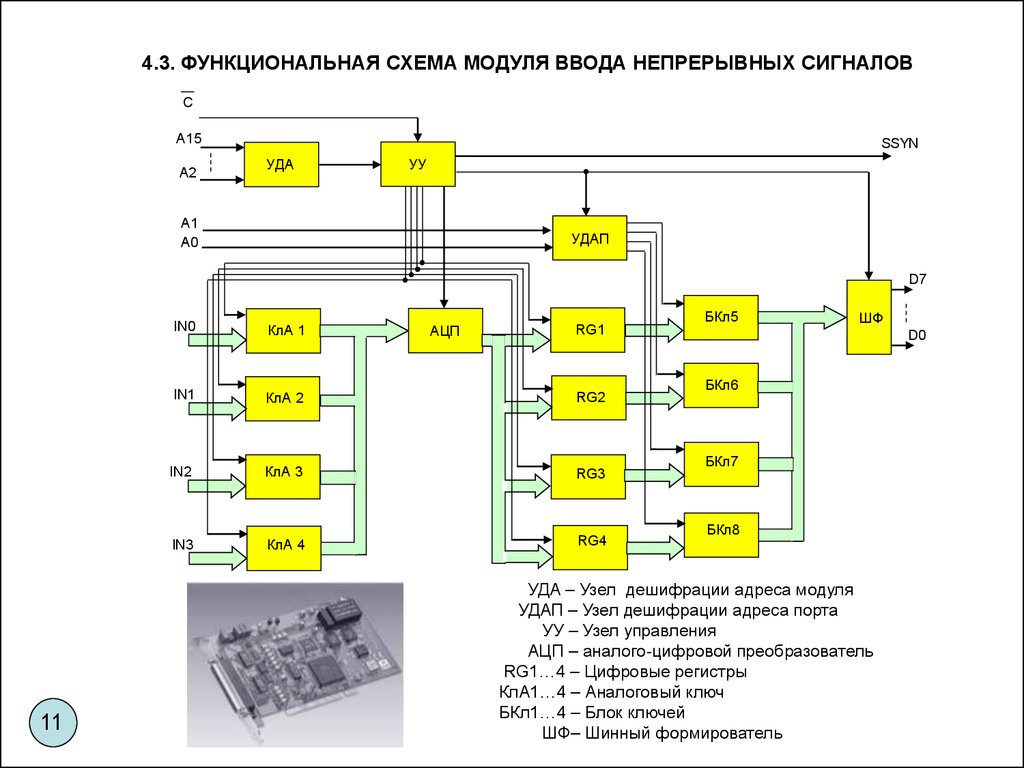

4.3. ФУНКЦИОНАЛЬНАЯ СХЕМА МОДУЛЯ ВВОДА НЕПРЕРЫВНЫХ СИГНАЛОВC

A15

A2

SSYN

УДА

УУ

A1

A0

УДАП

D7

11

IN0

КлА 1

IN1

КлА 2

RG2

IN2

КлА 3

RG3

IN3

КлА 4

RG4

АЦП

RG1

БКл5

ШФ

D0

БКл6

БКл7

БКл8

УДА – Узел дешифрации адреса модуля

УДАП – Узел дешифрации адреса порта

УУ – Узел управления

АЦП – аналого-цифровой преобразователь

RG1…4 – Цифровые регистры

КлА1…4 – Аналоговый ключ

БКл1…4 – Блок ключей

ШФ– Шинный формирователь

14.

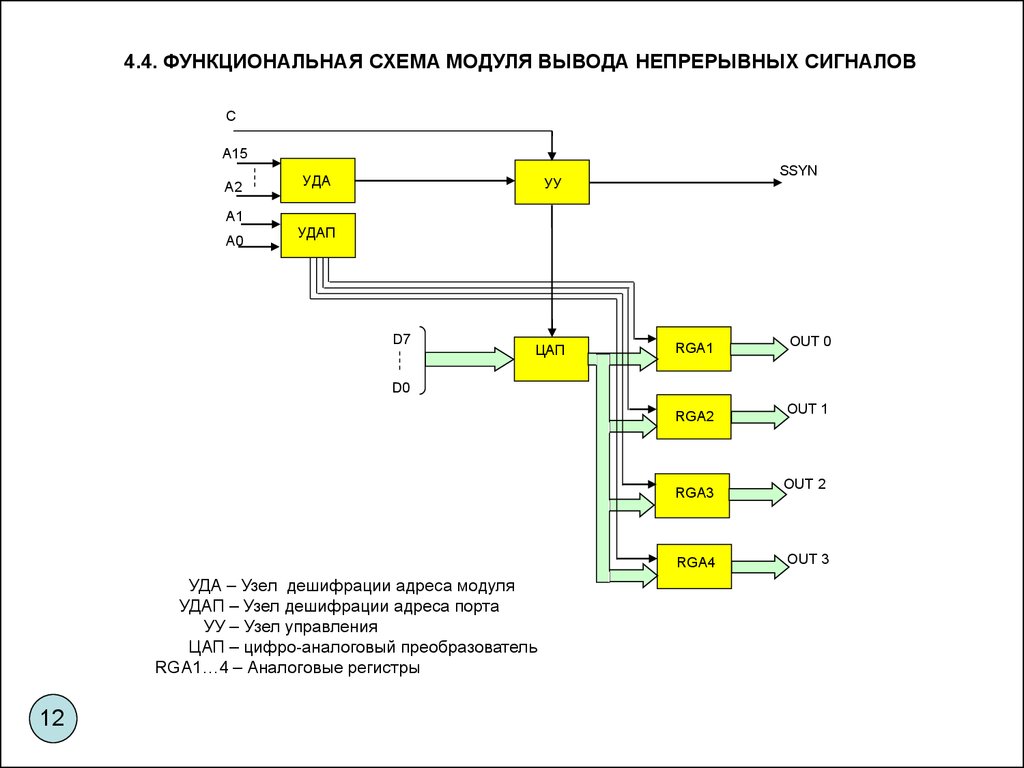

4.4. ФУНКЦИОНАЛЬНАЯ СХЕМА МОДУЛЯ ВЫВОДА НЕПРЕРЫВНЫХ СИГНАЛОВC

A15

A2

УДА

SSYN

УУ

A1

A0

УДАП

D7

ЦAП

RGА1

OUT 0

RGА2

OUT 1

RGА3

OUT 2

RGА4

OUT 3

D0

УДА – Узел дешифрации адреса модуля

УДАП – Узел дешифрации адреса порта

УУ – Узел управления

ЦАП – цифро-аналоговый преобразователь

RGА1…4 – Аналоговые регистры

12

15.

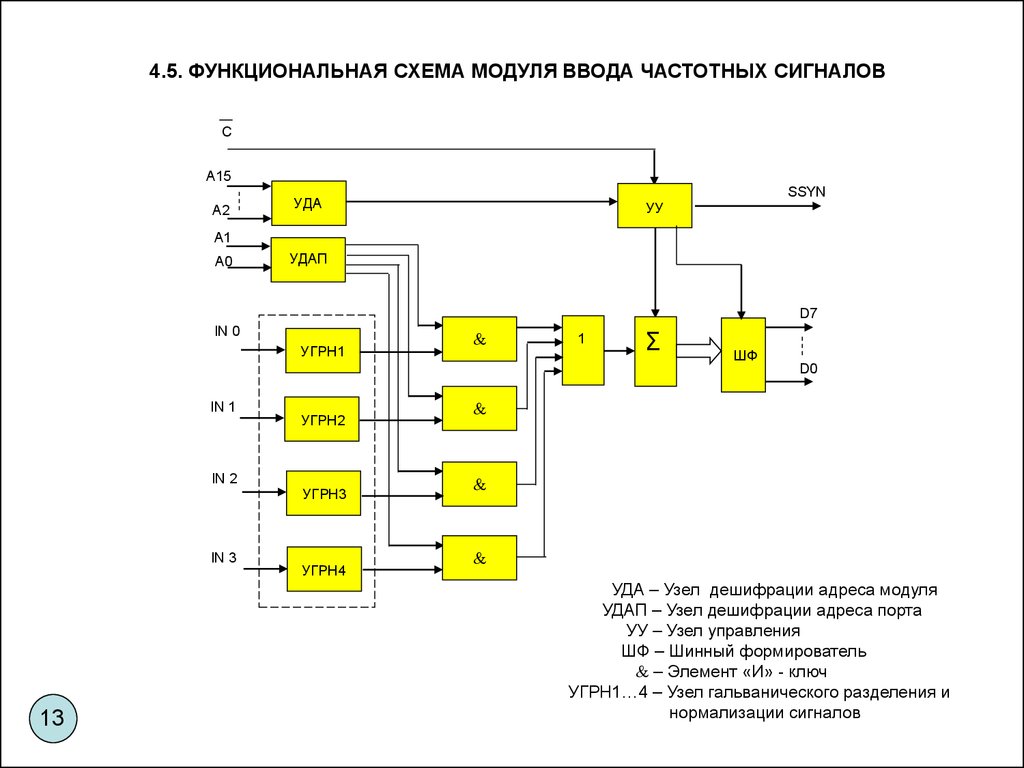

4.5. ФУНКЦИОНАЛЬНАЯ СХЕМА МОДУЛЯ ВВОДА ЧАСТОТНЫХ СИГНАЛОВC

A15

A2

SSYN

УДА

УУ

A1

A0

УДАП

D7

IN 0

УГРН1

1

Σ

ШФ

D0

IN 1

IN 2

IN 3

13

УГРН2

УГРН3

УГРН4

УДА – Узел дешифрации адреса модуля

УДАП – Узел дешифрации адреса порта

УУ – Узел управления

ШФ – Шинный формирователь

– Элемент «И» - ключ

УГРН1…4 – Узел гальванического разделения и

нормализации сигналов

16.

5. ОРГАНИЗАЦИЯ ЭЛЕКТРОННОЙ ПАМЯТИ В УВК5.1. ОРГАНИЗАЦИЯ ЭЛЕКТРОННОЙ ПАМЯТИ В ПЭВМ

ПАМЯТЬ

ПЭВМ

ВНУТРЕННЯЯ

ПАМЯТЬ

ПЗУ

(ROM)

ОЗУ

(RAM)

Динамическое ОЗУ

(DRAM)

14

ВНЕШНЯЯ

ПАМЯТЬ

Статическое

ОЗУ (SRAM)

17.

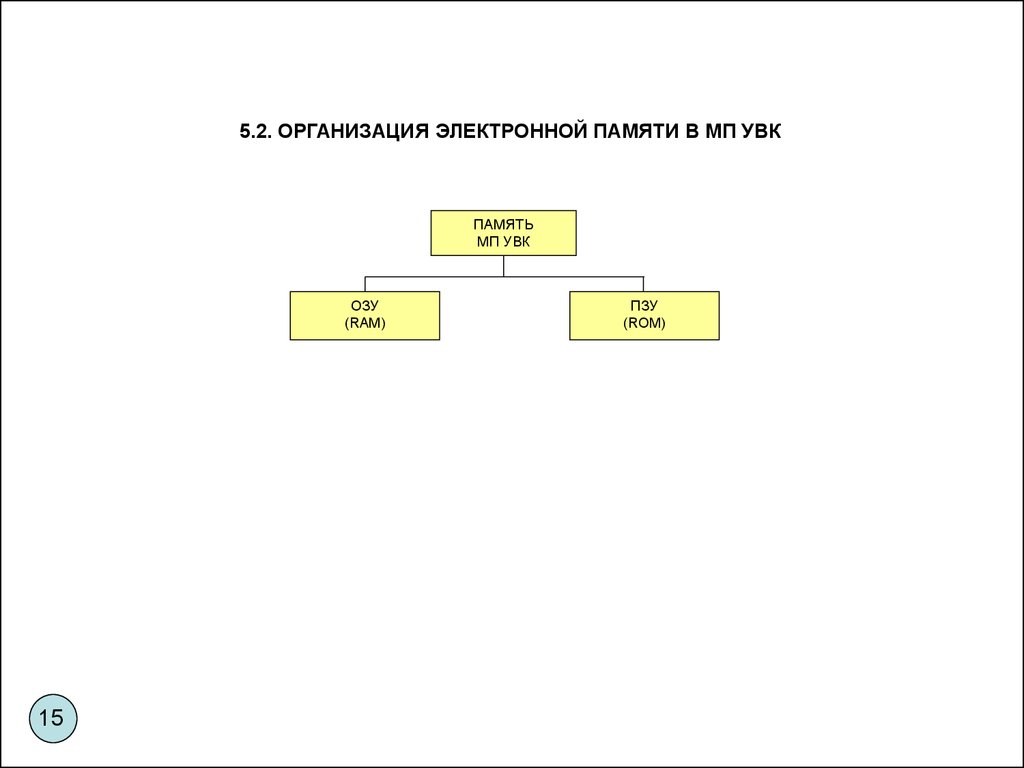

5.2. ОРГАНИЗАЦИЯ ЭЛЕКТРОННОЙ ПАМЯТИ В МП УВКПАМЯТЬ

МП УВК

ОЗУ

(RAM)

15

ПЗУ

(ROM)

18.

6. СТРУКТУРА МОДУЛЯ ЦПУ266 МГц

Pentium

кеш

L1

6.1. Структура платы ЦПУ

с процессором Рentium

ШИНА

кеш

L2

П Р О Ц Е С О Р А - 66МГц

66 МГц

North

Bridge

EDO SIMM

SDRAM DIMM

P C I – 33МГц

USB1 USB2

PCI

Video

CMOS

RTS

PCI

South

Bridge

IDE1

IDE2

I S A - 8МГц

Дисковод

ISA

COM1

COM2

Мыша Клавіатура

16

ROM

LPT1

19.

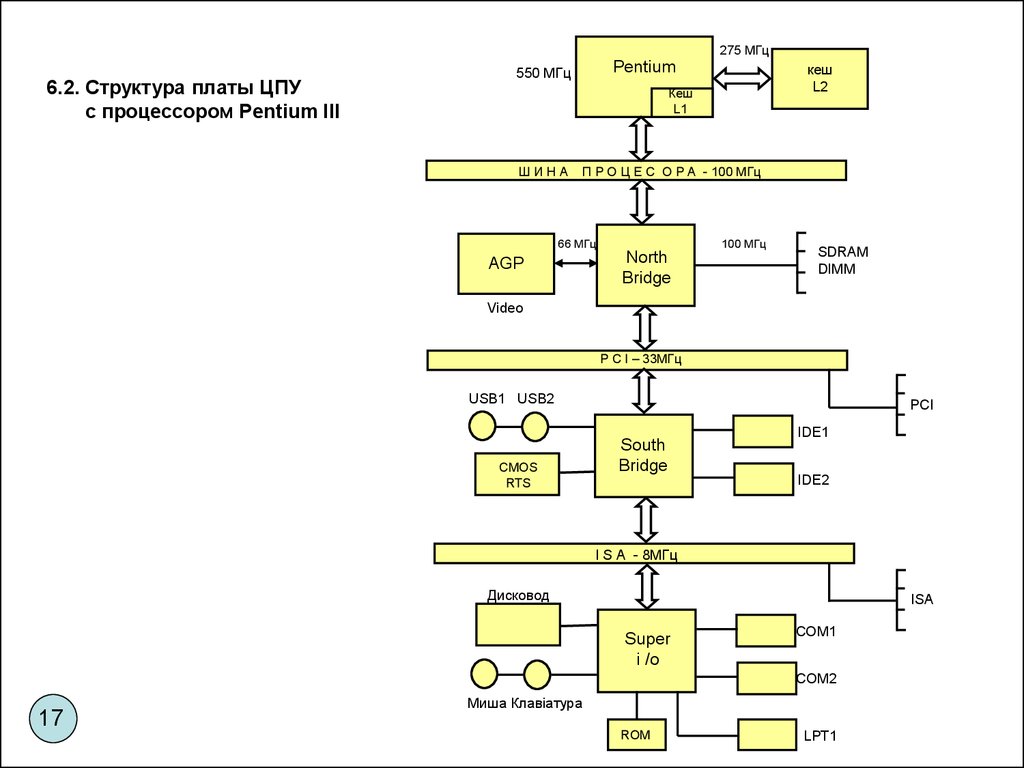

275 МГц6.2. Структура платы ЦПУ

с процессором Рentium III

Pentium

550 МГц

кеш

L2

Кеш

L1

ШИНА

П Р О Ц Е С О Р А - 100 МГц

66 МГц

AGP

North

Bridge

100 МГц

SDRAM

DIMM

Video

P C I – 33МГц

USB1 USB2

CMOS

RTS

PCI

South

Bridge

IDE1

IDE2

I S A - 8МГц

Дисковод

ISA

Super

i /o

COM1

COM2

17

Миша Клавіатура

ROM

LPT1

20.

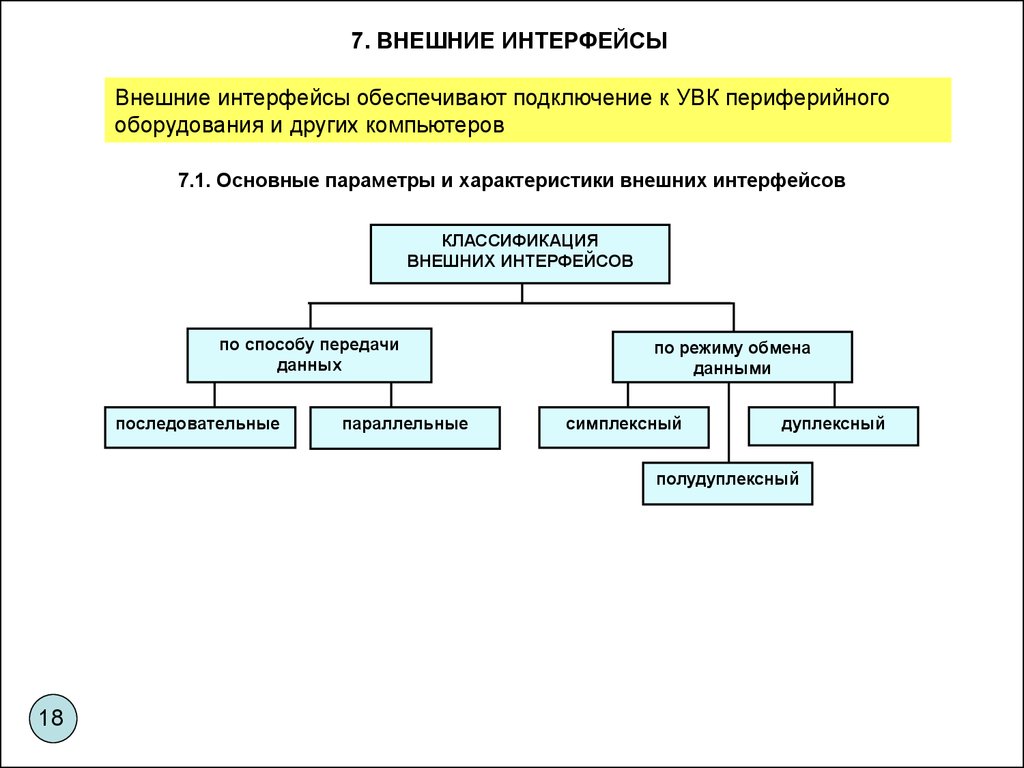

7. ВНЕШНИЕ ИНТЕРФЕЙСЫВнешние интерфейсы обеспечивают подключение к УВК периферийного

оборудования и других компьютеров

7.1. Основные параметры и характеристики внешних интерфейсов

КЛАССИФИКАЦИЯ

ВНЕШНИХ ИНТЕРФЕЙСОВ

по способу передачи

данных

последовательные

параллельные

по режиму обмена

данными

симплексный

дуплексный

полудуплексный

18

21.

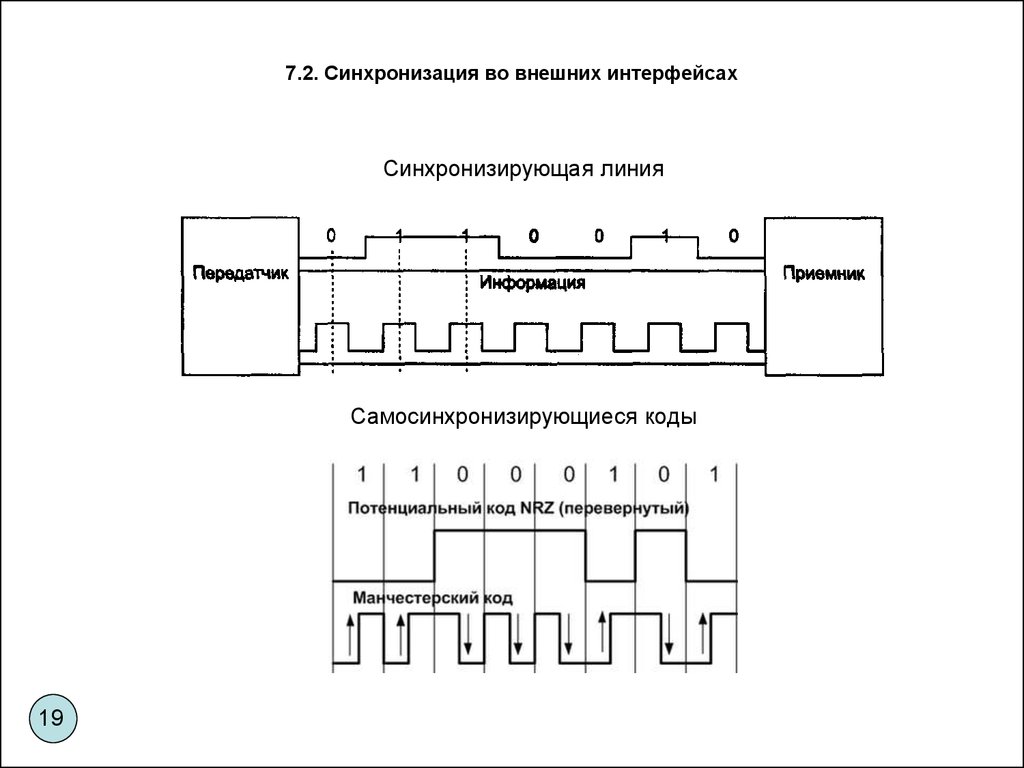

7.2. Синхронизация во внешних интерфейсахСинхронизирующая линия

Самосинхронизирующиеся коды

19

22.

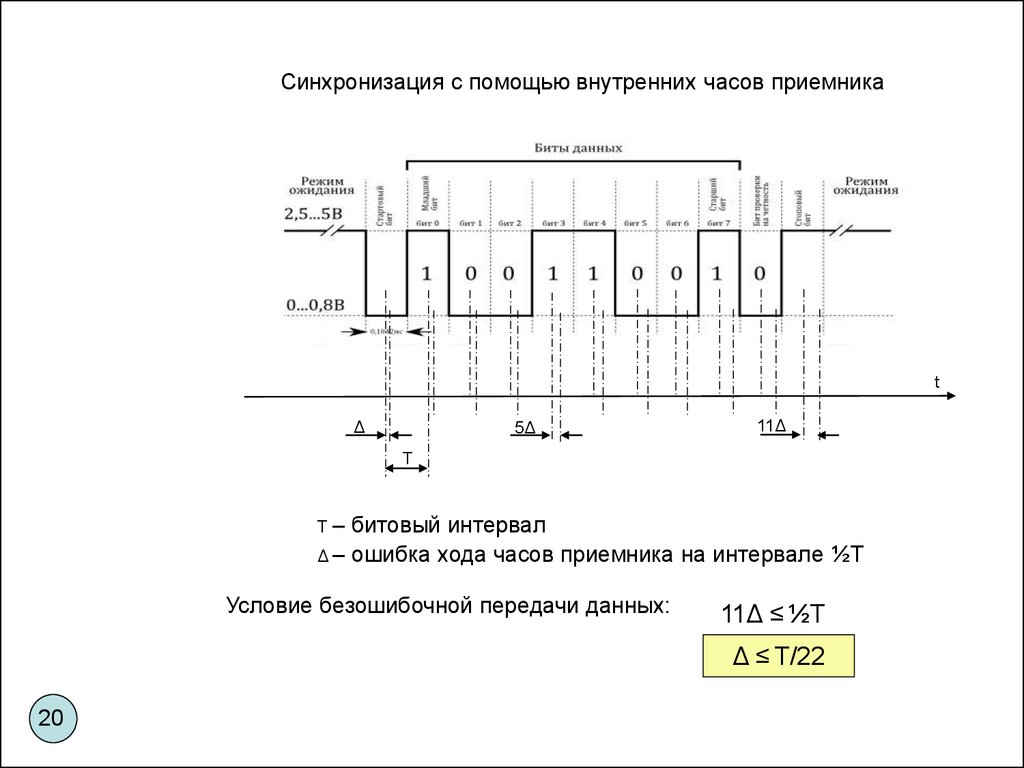

Синхронизация с помощью внутренних часов приемникаt

Δ

5Δ

11Δ

T

T–

битовый интервал

Δ – ошибка хода часов приемника на интервале ½T

Условие безошибочной передачи данных:

11Δ ≤ ½T

Δ ≤ T/22

20

23.

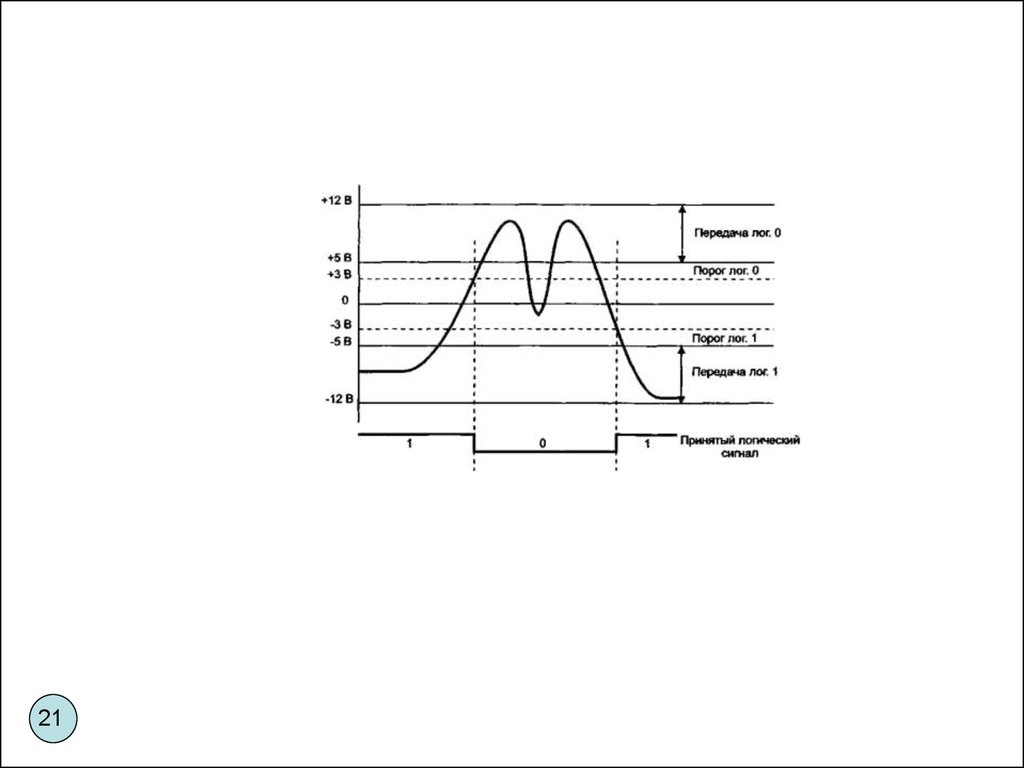

2124.

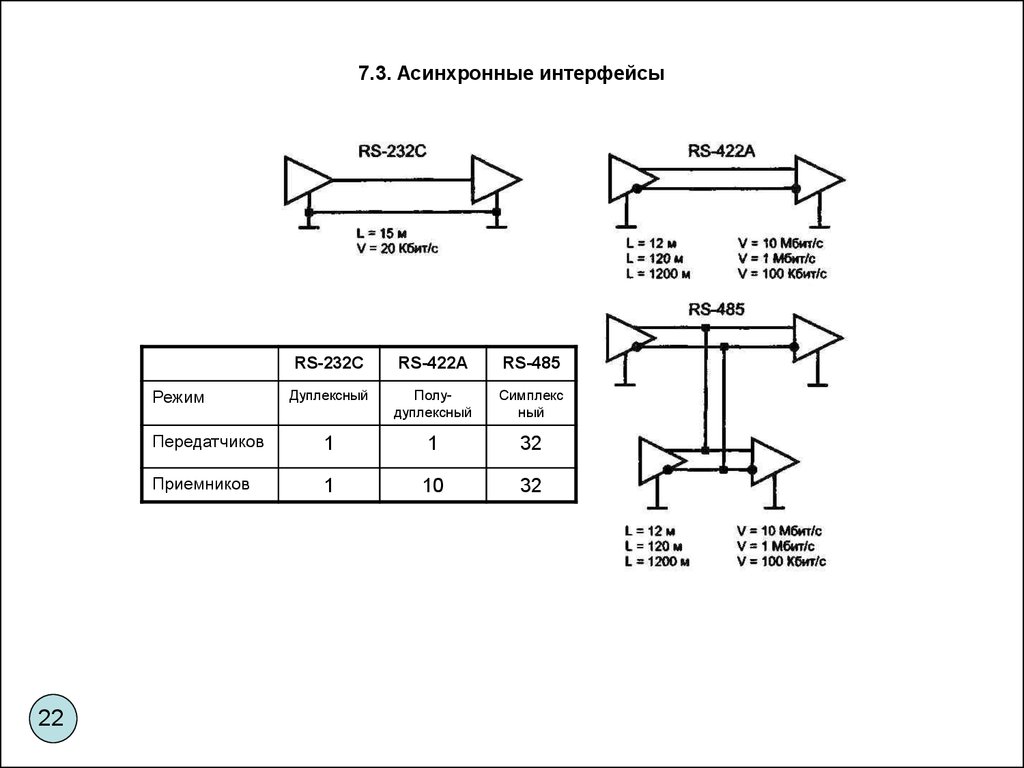

7.3. Асинхронные интерфейсыRS-232C

RS-422A

RS-485

Дуплексный

Полудуплексный

Симплекс

ный

Передатчиков

1

1

32

Приемников

1

10

32

Режим

22

25.

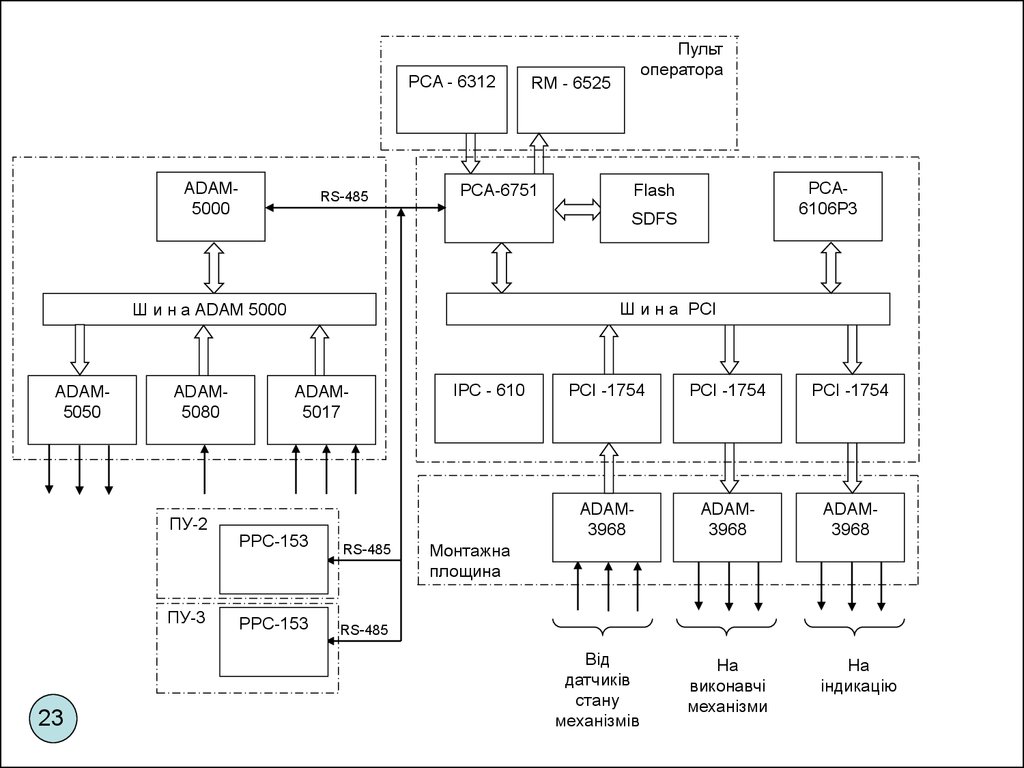

PCA - 6312ADAM5000

RS-485

ADAM5080

23

РСА6106Р3

Flash

SDFS

Ш и н а PCI

ADAM5017

ІРС - 610

ПУ-2

ПУ-3

RM - 6525

РСА-6751

Ш и н а ADAM 5000

ADAM5050

Пульт

оператора

PPC-153

RS-485

PPC-153

RS-485

РСІ -1754

РСІ -1754

РСІ -1754

ADAM3968

ADAM3968

ADAM3968

Монтажна

площина

Від

датчиків

стану

механізмів

На

виконавчі

механізми

На

індикацію

Программирование

Программирование