Похожие презентации:

Основы цифровой техники. (Лекция 2)

1. Лекция вторая

Основы цифровой техники2.

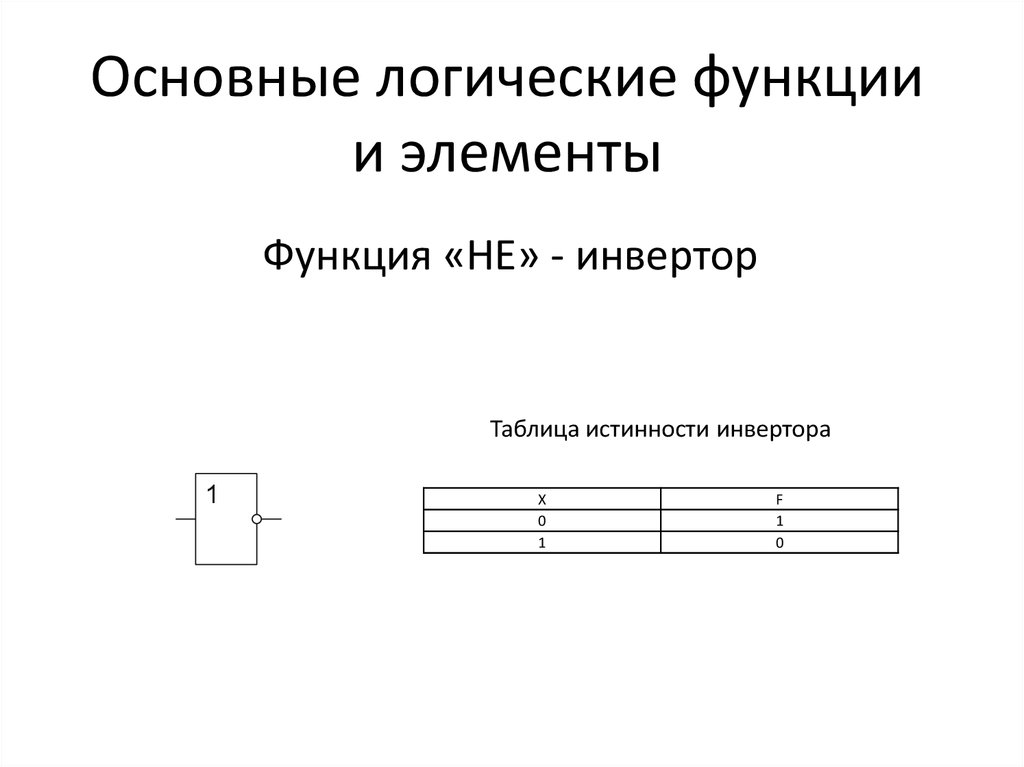

Основные логические функциии элементы

Функция «НЕ» - инвертор

Таблица истинности инвертора

1

X

0

1

F

1

0

3.

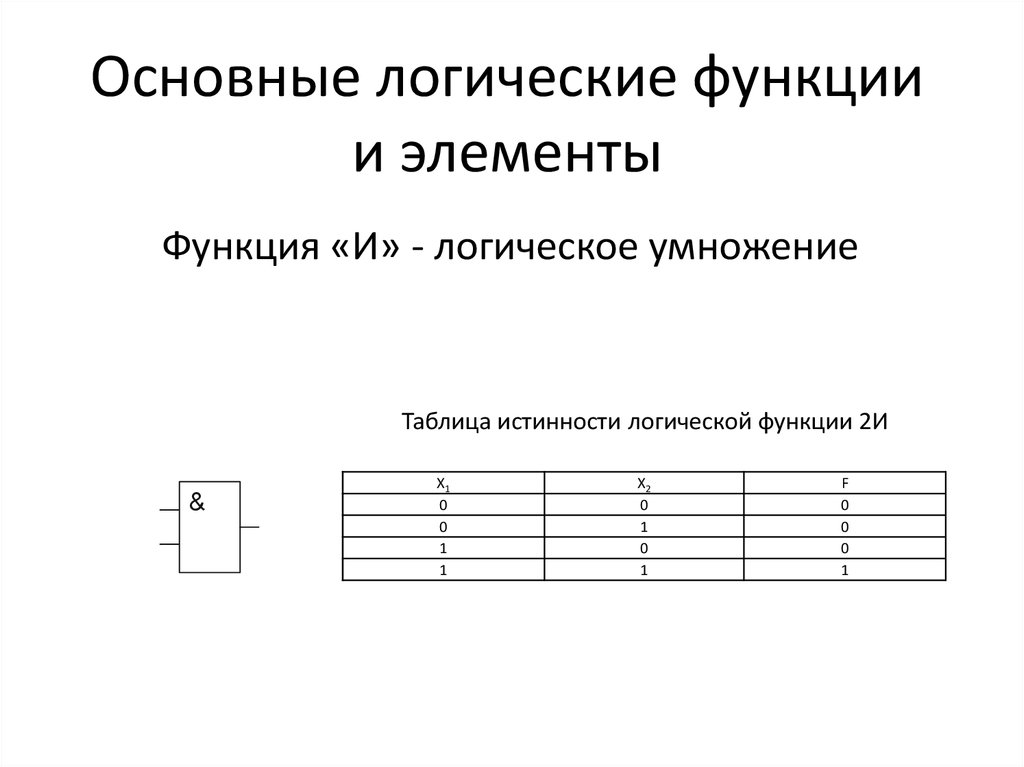

Основные логические функциии элементы

Функция «И» - логическое умножение

Таблица истинности логической функции 2И

&

X1

0

0

1

1

X2

0

1

0

1

F

0

0

0

1

4.

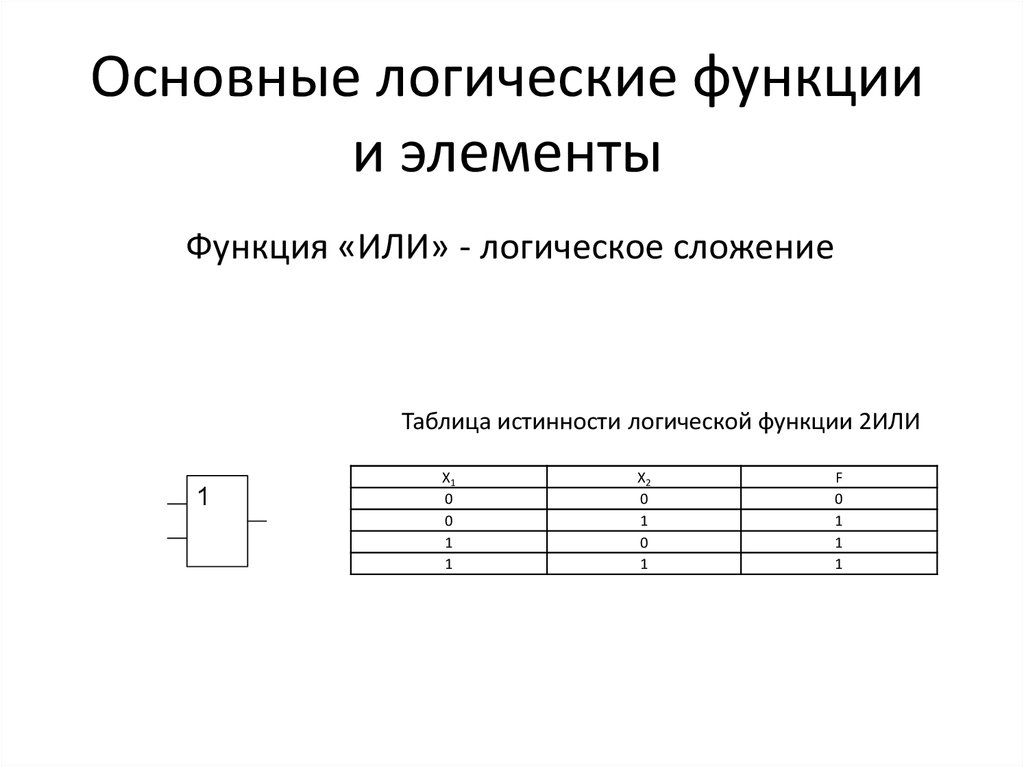

Основные логические функциии элементы

Функция «ИЛИ» - логическое сложение

Таблица истинности логической функции 2ИЛИ

1

X1

0

0

1

1

X2

0

1

0

1

F

0

1

1

1

5.

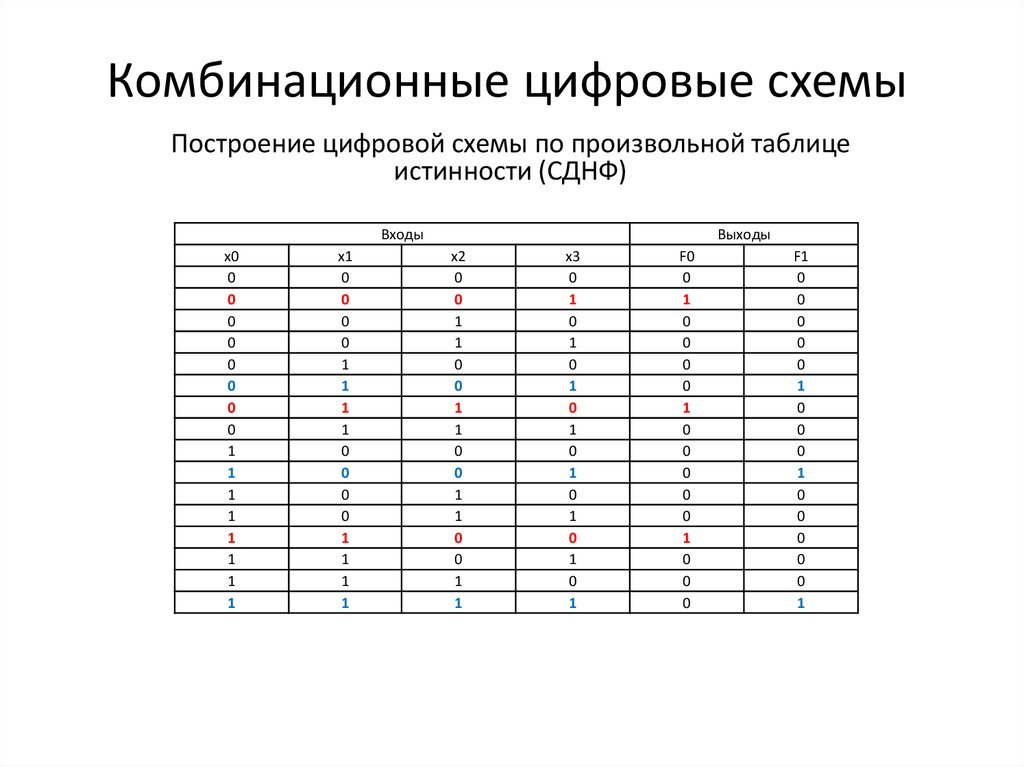

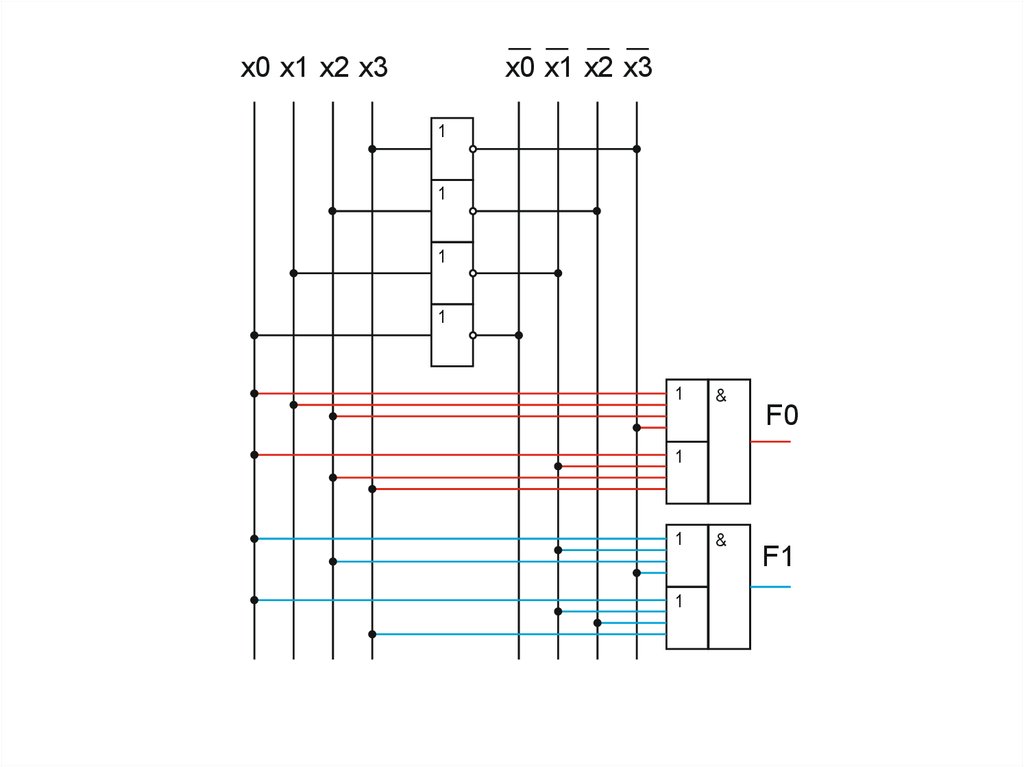

Комбинационные цифровые схемыПостроение цифровой схемы по произвольной таблице

истинности (СДНФ)

Входы

x0

0

0

0

0

0

0

0

0

1

1

1

1

1

1

1

1

x1

0

0

0

0

1

1

1

1

0

0

0

0

1

1

1

1

Выходы

x2

0

0

1

1

0

0

1

1

0

0

1

1

0

0

1

1

x3

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

F0

0

1

0

0

0

0

1

0

0

0

0

0

1

0

0

0

F1

0

0

0

0

0

1

0

0

0

1

0

0

0

0

0

1

6.

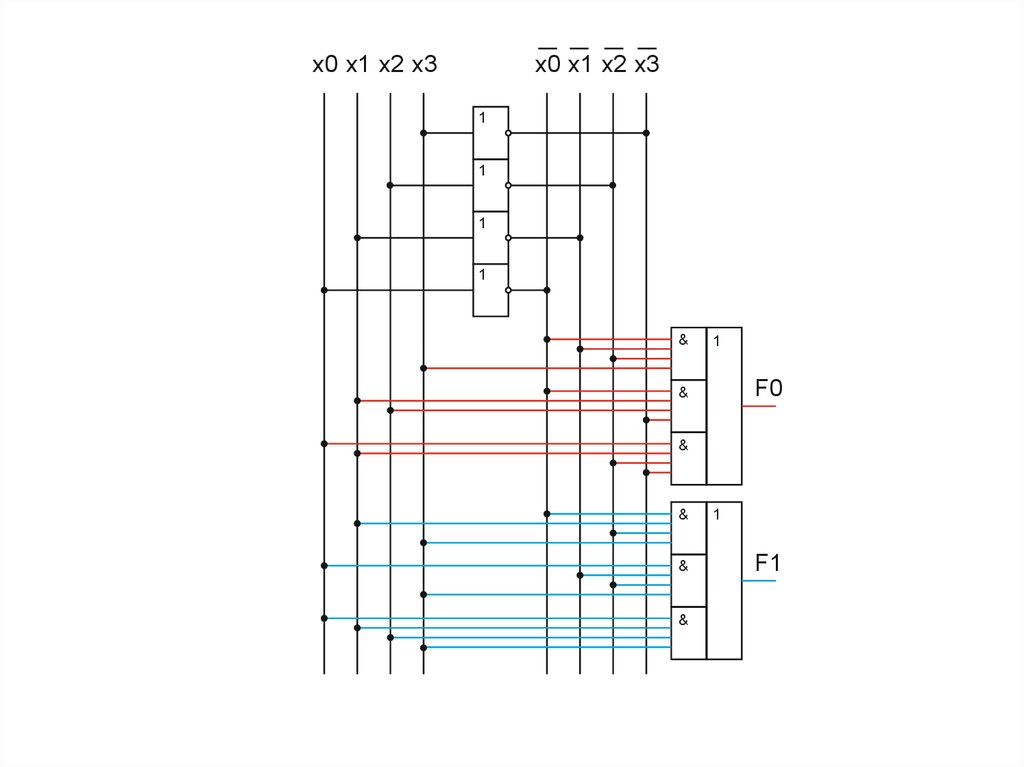

x0 x1 x2 x3x0 x1 x2 x3

1

1

1

1

&

1

F0

&

&

&

&

&

1

F1

7.

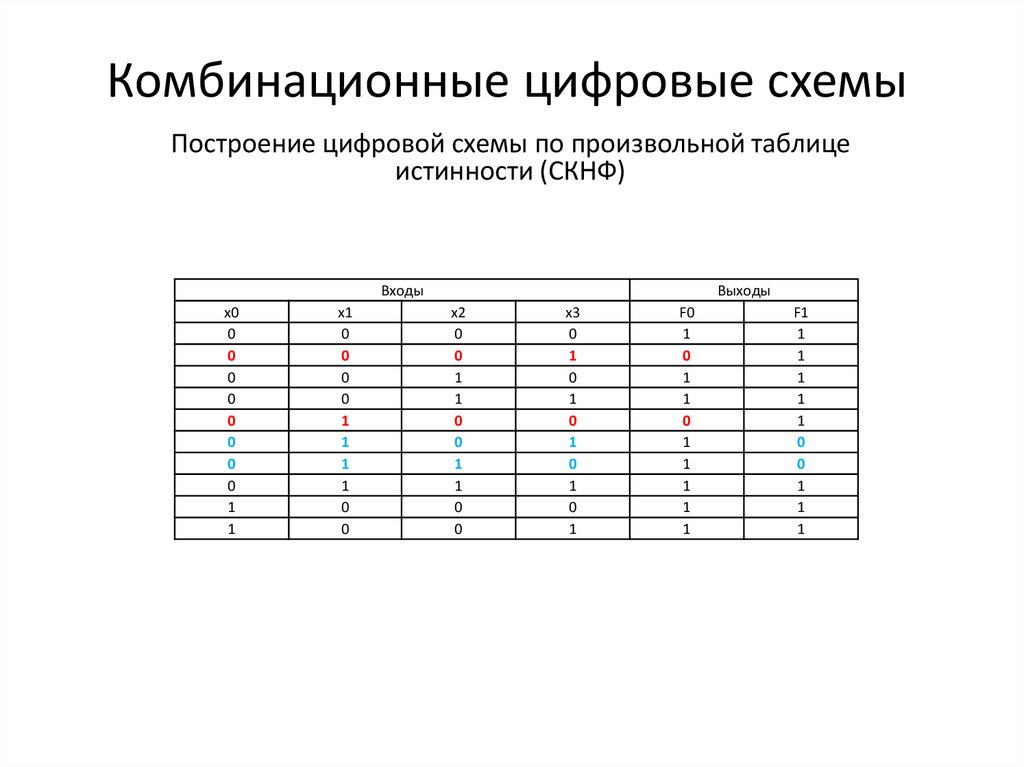

Комбинационные цифровые схемыПостроение цифровой схемы по произвольной таблице

истинности (СКНФ)

Входы

x0

0

0

0

0

0

0

0

0

1

1

x1

0

0

0

0

1

1

1

1

0

0

Выходы

x2

0

0

1

1

0

0

1

1

0

0

x3

0

1

0

1

0

1

0

1

0

1

F0

1

0

1

1

0

1

1

1

1

1

F1

1

1

1

1

1

0

0

1

1

1

8.

x0 x1 x2 x3x0 x1 x2 x3

1

1

1

1

1

&

F0

1

1

1

&

F1

9.

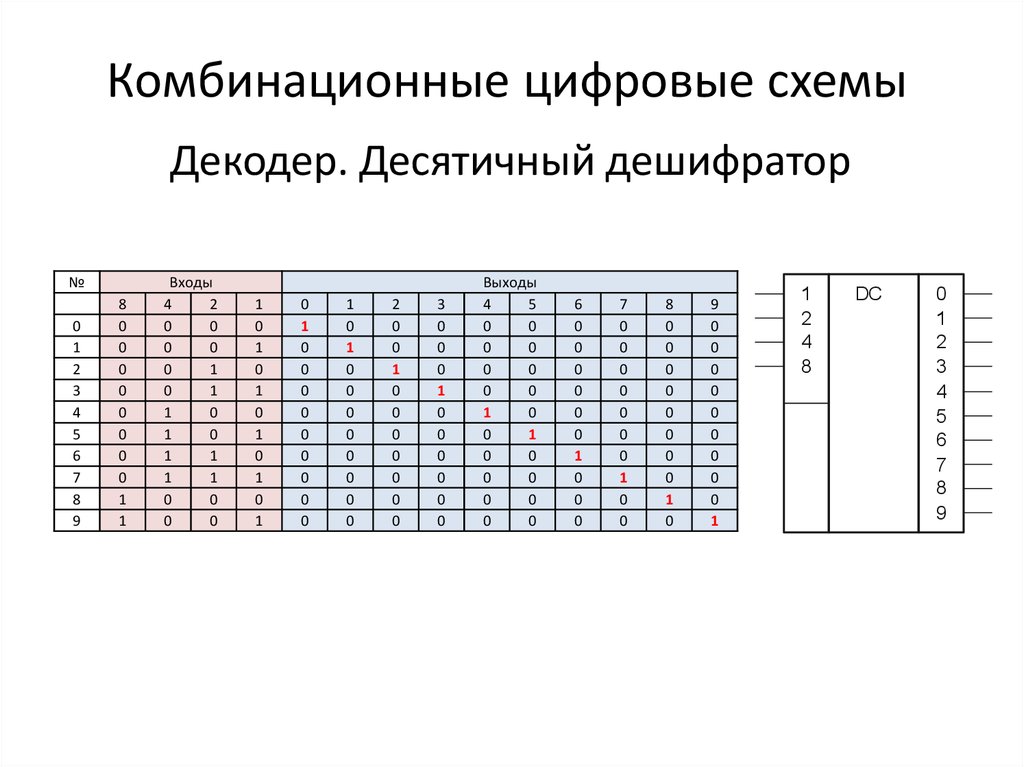

Комбинационные цифровые схемыДекодер. Десятичный дешифратор

№

0

1

2

3

4

5

6

7

8

9

8

0

0

0

0

0

0

0

0

1

1

Входы

4

2

0

0

0

0

0

1

0

1

1

0

1

0

1

1

1

1

0

0

0

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

0

0

0

0

0

0

0

0

1

0

1

0

0

0

0

0

0

0

0

2

0

0

1

0

0

0

0

0

0

0

3

0

0

0

1

0

0

0

0

0

0

Выходы

4

5

0

0

0

0

0

0

0

0

1

0

0

1

0

0

0

0

0

0

0

0

6

0

0

0

0

0

0

1

0

0

0

7

0

0

0

0

0

0

0

1

0

0

8

0

0

0

0

0

0

0

0

1

0

9

0

0

0

0

0

0

0

0

0

1

1

2

4

8

DC

0

1

2

3

4

5

6

7

8

9

10.

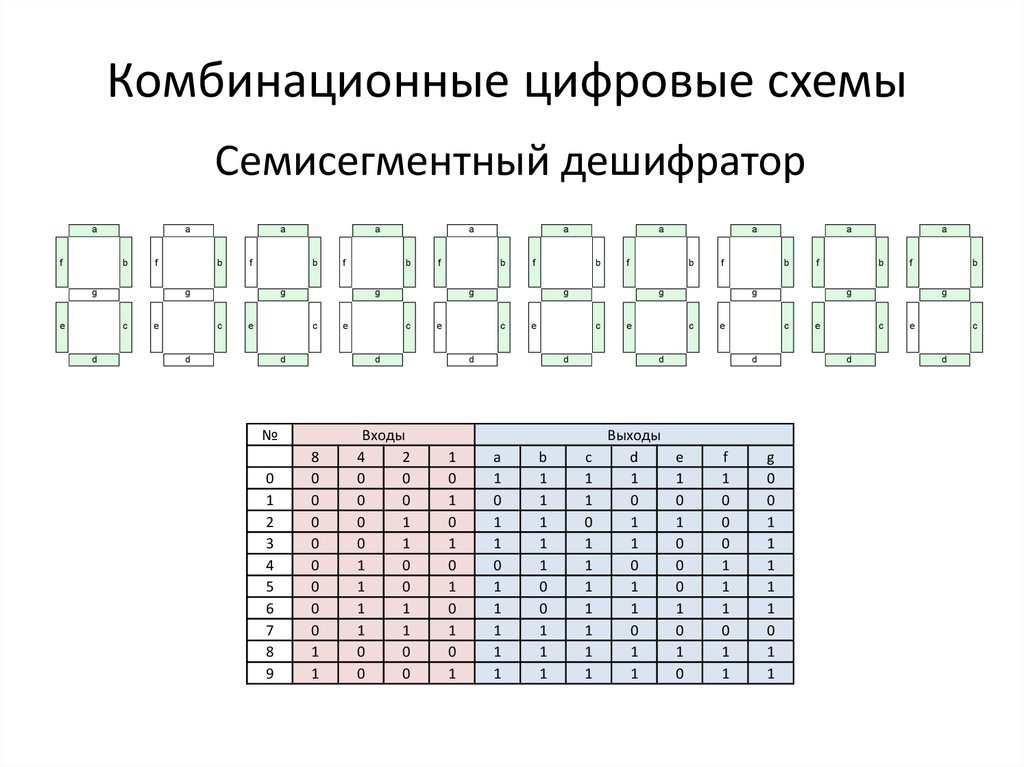

Комбинационные цифровые схемыСемисегментный дешифратор

a

f

a

b

f

g

e

b

f

e

a

b

g

c

d

a

f

g

c

e

d

f

e

8

0

0

0

0

0

0

0

0

1

1

a

b

c

e

Входы

4

2

0

0

0

0

0

1

0

1

1

0

1

0

1

1

1

1

0

0

0

0

b

c

d

a

1

0

1

1

0

1

1

1

1

1

b

1

1

1

1

1

0

0

1

1

1

b

c

f

c

d

e

1

0

1

0

0

0

1

0

1

0

f

1

0

0

0

1

1

1

0

1

1

a

b

f

g

e

d

c

1

1

0

1

1

1

1

1

1

1

b

g

e

Выходы

d

1

0

1

1

0

1

1

0

1

1

a

f

g

e

d

a

f

g

c

1

0

1

0

1

0

1

0

1

0

1

a

f

g

d

№

0

1

2

3

4

5

6

7

8

9

b

g

c

d

a

e

g

0

0

1

1

1

1

1

0

1

1

g

c

d

b

e

c

d

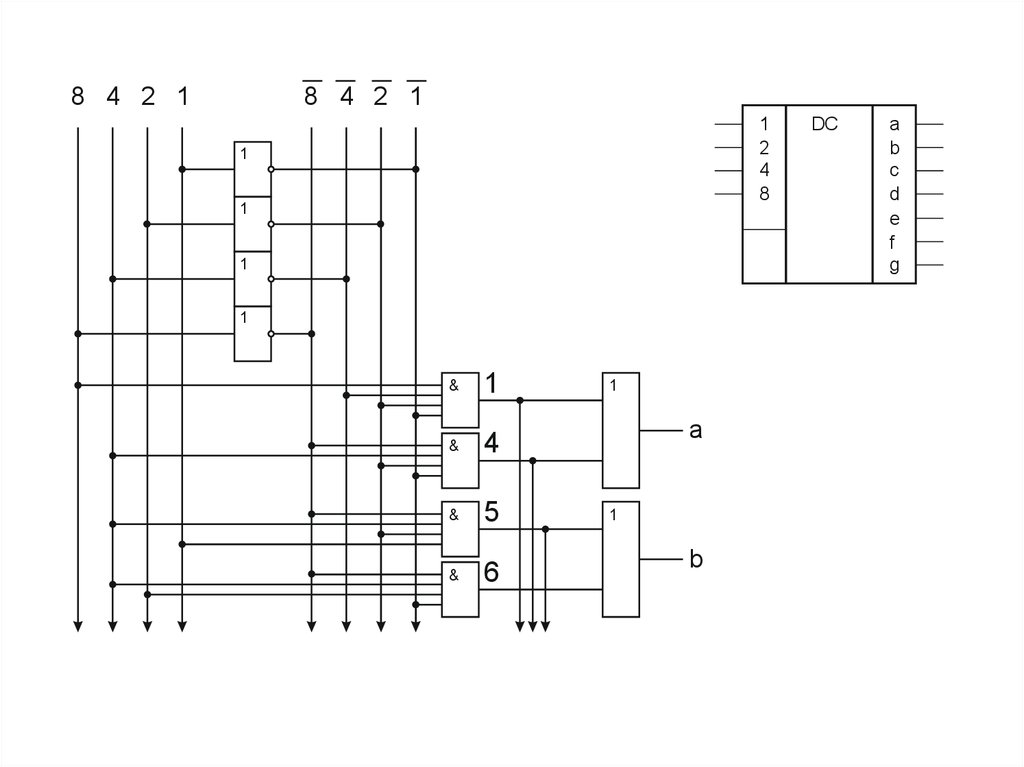

11.

8 4 2 18 4 2 1

1

2

4

8

1

1

1

1

&

1

&

4

&

5

&

6

1

a

1

b

DC

a

b

c

d

e

f

g

12.

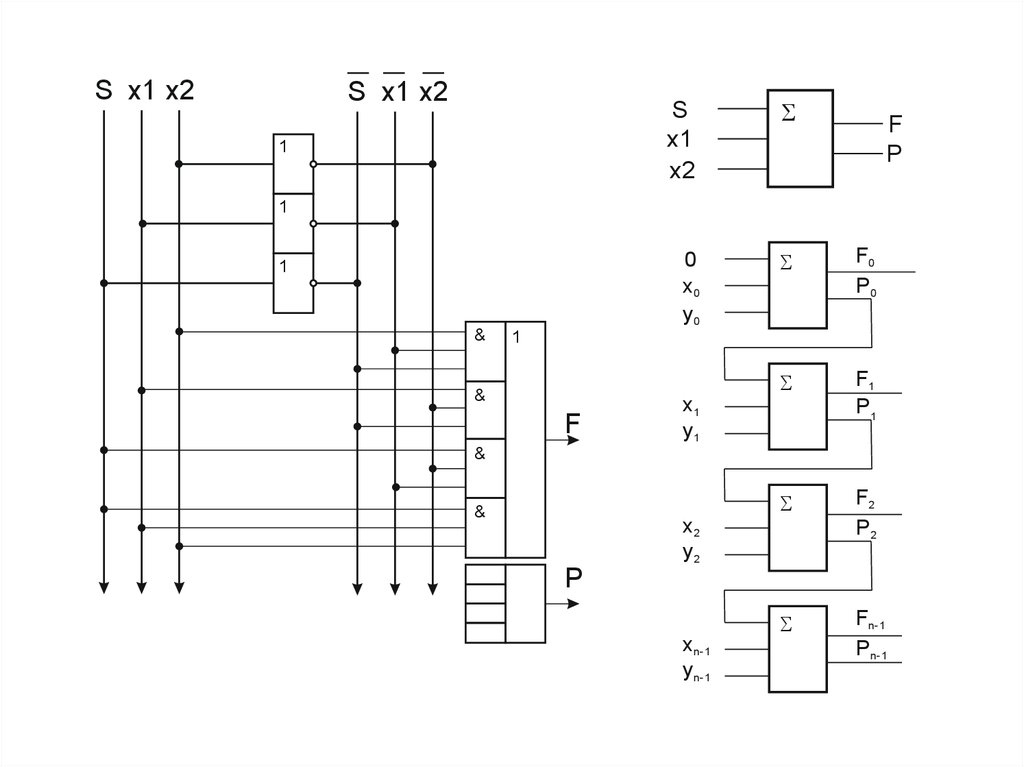

Комбинационные цифровые схемыСумматор

S

0

0

0

0

1

1

1

1

Входы

x1

0

0

1

1

0

0

1

1

Выходы

x2

0

1

0

1

0

1

0

1

F

0

1

1

0

1

0

0

1

P

0

0

0

1

0

1

1

1

13.

S x1 x2S x1 x2

1

S

x1

x2

0

x0

y0

F0

P0

F1

P1

F2

P2

Fn-1

P n-1

F

P

1

1

&

1

&

F

x1

y1

&

&

x2

y2

P

xn-1

yn-1

14.

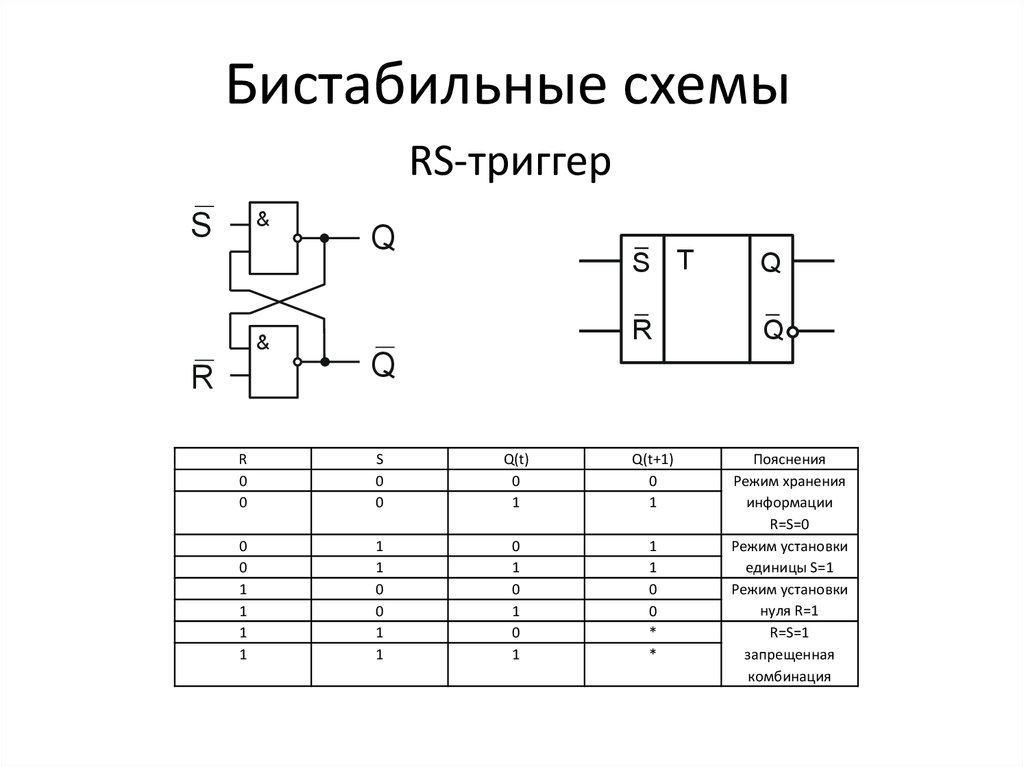

Бистабильные схемыRS-триггер

&

S

&

R

Q

S T

Q

R

Q

Q

R

0

0

S

0

0

Q(t)

0

1

Q(t+1)

0

1

0

0

1

1

1

1

1

1

0

0

1

1

0

1

0

1

0

1

1

1

0

0

*

*

Пояснения

Режим хранения

информации

R=S=0

Режим установки

единицы S=1

Режим установки

нуля R=1

R=S=1

запрещенная

комбинация

15.

Бистабильные схемыСинхронный RS-триггер

&

S

&

Q

S T

C

R

C

&

&

R

Q

Q

Q

С

0

0

1

1

1

1

R

X

X

0

0

0

0

S

X

X

0

0

1

1

Q(t)

0

1

0

1

0

1

Q(t+1)

0

1

0

1

1

1

1

1

1

1

0

0

0

1

0

0

1

1

1

1

1

1

0

1

*

*

Пояснения

Режим хранения

информации

Режим хранения

информации

Режим

установки

единицы S=1

Режим

установки нуля

R=1

R=S=1

запрещенная

комбинация

16.

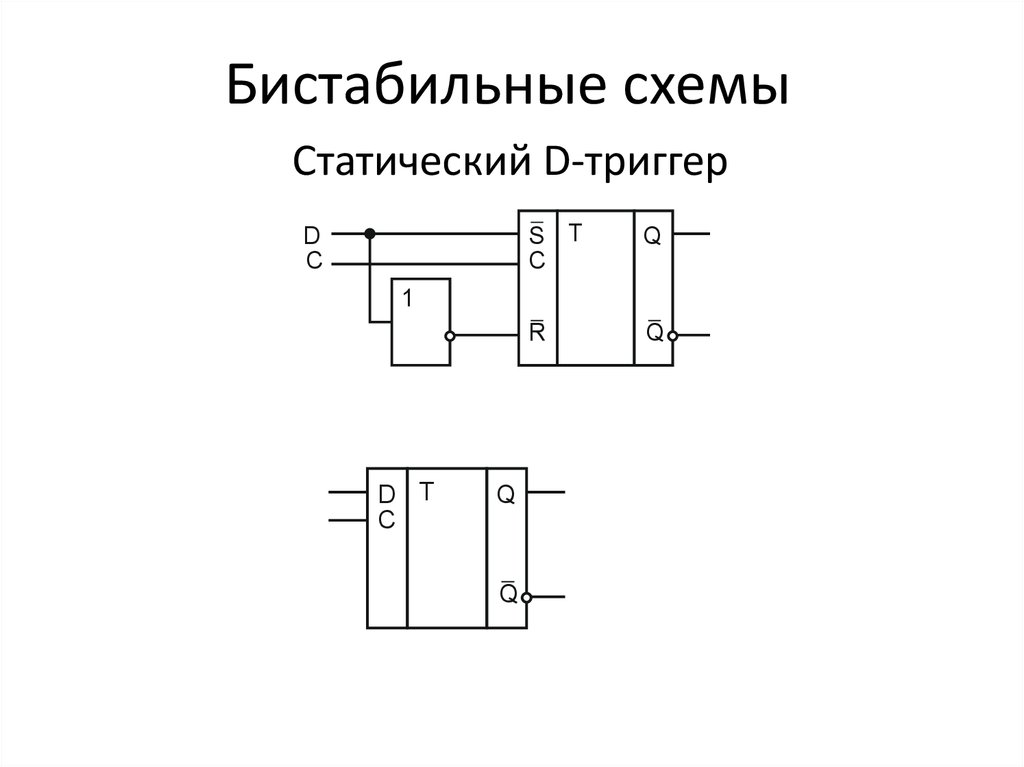

Бистабильные схемыСтатический D-триггер

D

C

S T

C

Q

R

Q

1

D T

C

Q

Q

17.

Бистабильные схемыДинамический D-триггер

D T

C

Q

Q’

D T

C

Q

Q

Q

1

D TT

C

Q

Q

18.

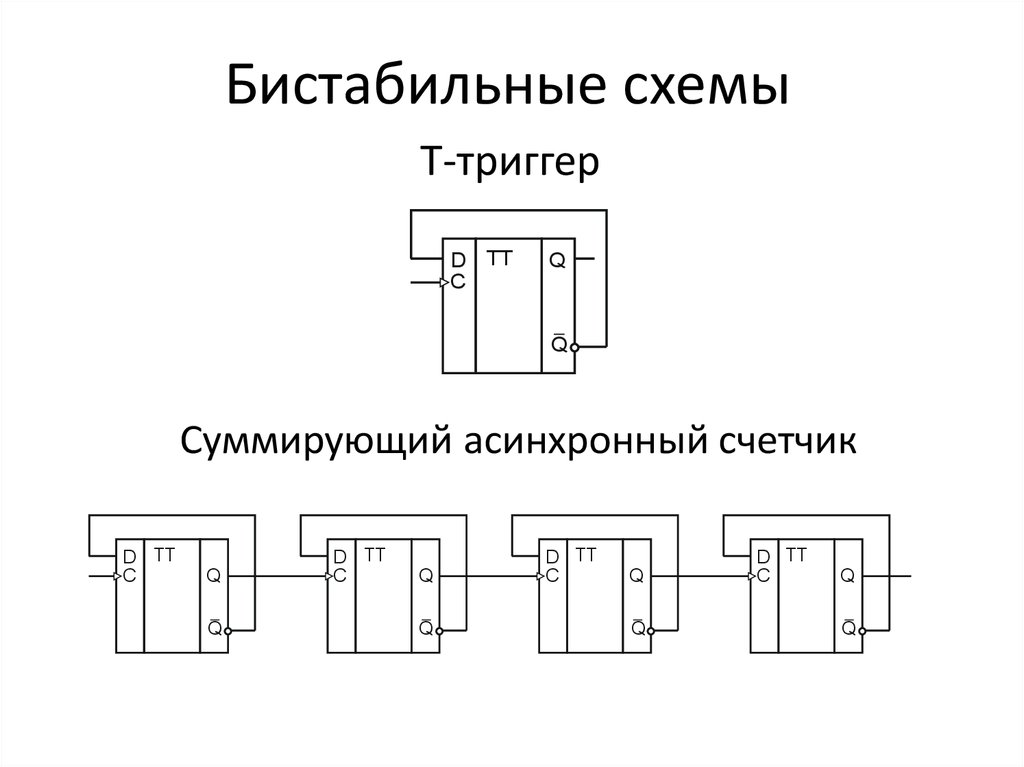

Бистабильные схемыT-триггер

D TT

C

Q

Q

Суммирующий асинхронный счетчик

D TT

C

Q

Q

D TT

C

Q

Q

D TT

C

Q

Q

D TT

C

Q

Q

19.

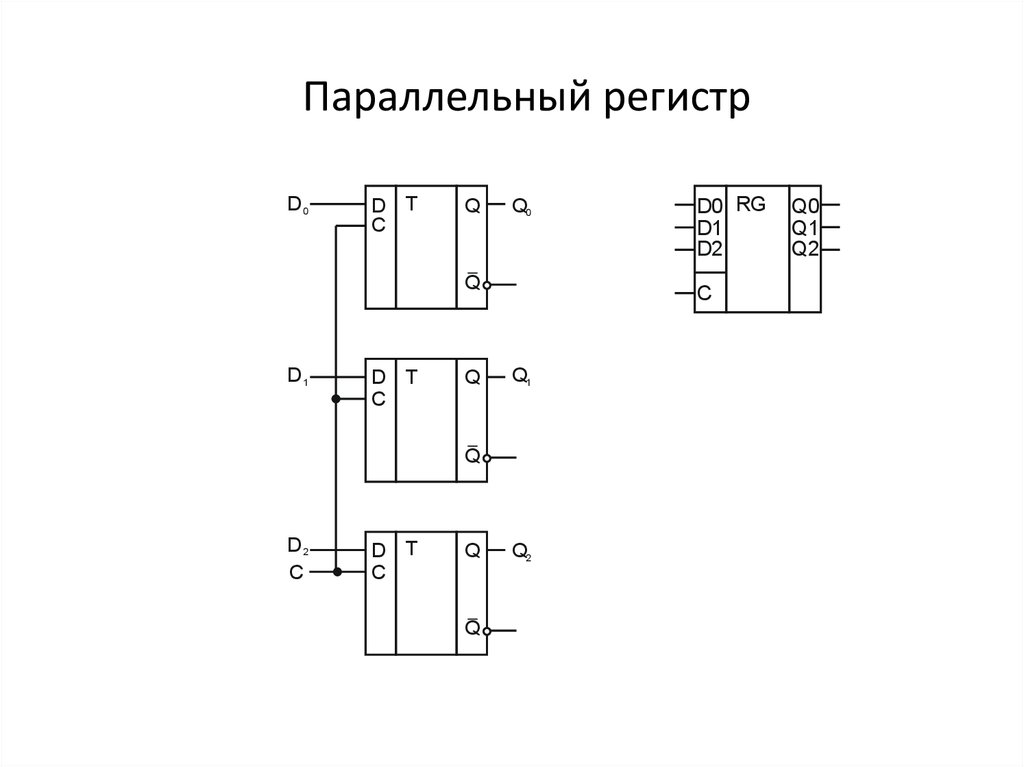

Параллельный регистрD0

D T

C

Q

Q0

Q

D1

D T

C

Q

C

Q1

Q

D2

C

D T

C

Q

Q

D0 RG

D1

D2

Q2

Q0

Q1

Q2

20.

Последовательный регистрD0

D T

C

Q

Q0

Q

D T

C

Q

C

Q1

Q

C

D T

C

Q

Q

D0 RG

Q2

Q0

Q1

Q2

21.

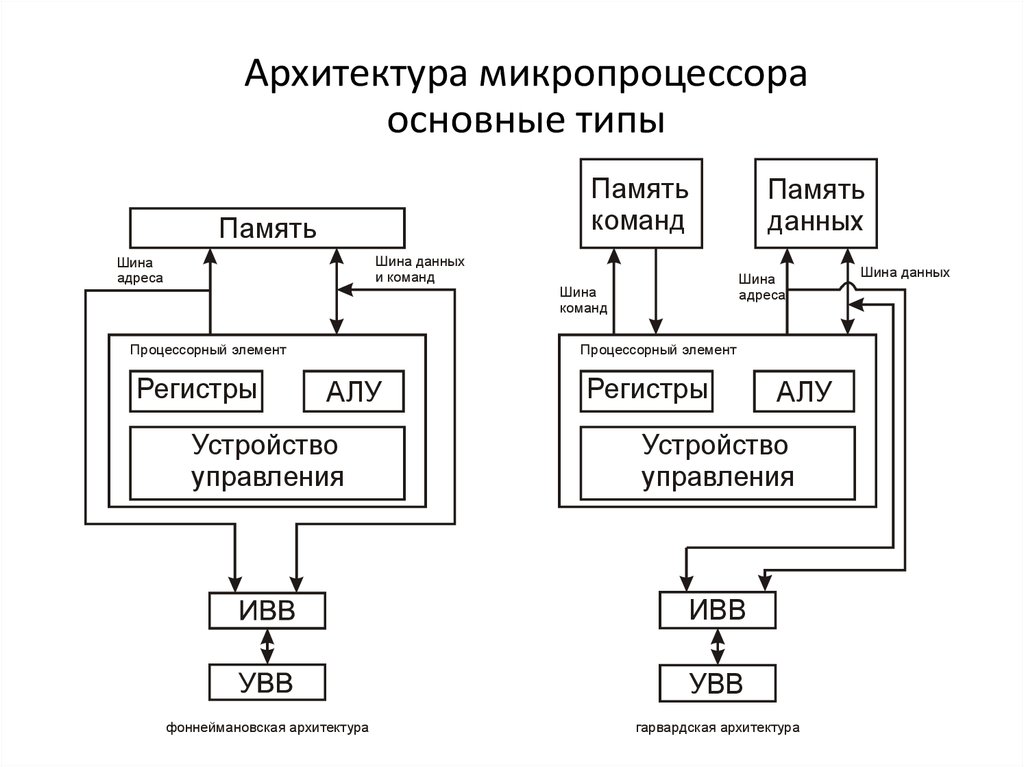

Архитектура микропроцессораосновные типы

Память

команд

Память

Шина данных

и команд

Шина

адреса

Процессорный элемент

Регистры

Память

данных

Шина

адреса

Шина

команд

Процессорный элемент

АЛУ

Устройство

управления

Регистры

АЛУ

Устройство

управления

ИВВ

УВВ

фоннеймановская архитектура

гарвардская архитектура

Шина данных

22.

Структурная схемамикропроцессорной системы

Информатика

Информатика